**Delft University of Technology**

## A 28-W, -102.2-dB THD+N Class-D Amplifier Using a Hybrid ΔΣM-PWM Scheme

Karmakar, Shoubhik; Zhang, Huajun; van Veldhoven, Robert; Breems, Lucien J.; Berkhout, Marco; Fan, Qinwen; Makinwa, Kofi A.A.

DOI 10.1109/JSSC.2020.3023874

**Publication date** 2020

**Document Version** Final published version

Published in IEEE Journal of Solid-State Circuits

**Citation (APA)** Karmakar, S., Zhang, H., van Veldhoven, R., Breems, L. J., Berkhout, M., Fan, Q., & Makinwa, K. A. A. (2020). A 28-W, -102.2-dB THD+N Class-D Amplifier Using a Hybrid  $\Delta\Sigma$ M-PWM Scheme. *IEEE Journal of* Solid-State Circuits, 55(12), 3146-3156. Article 9207737. https://doi.org/10.1109/JSSC.2020.3023874

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

# 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A 28-W, -102.2-dB THD+N Class-D Amplifier Using a Hybrid $\Delta \Sigma$ M-PWM Scheme

Shoubhik Karmakar<sup>®</sup>, Graduate Student Member, IEEE, Huajun Zhang<sup>®</sup>, Graduate Student Member, IEEE,

Robert van Veldhoven, Senior Member, IEEE, Lucien J. Breems<sup>(D)</sup>, Fellow, IEEE,

Marco Berkhout, Member, IEEE, Qinwen Fan, Senior Member, IEEE,

and Kofi A. A. Makinwa<sup>10</sup>, *Fellow, IEEE*

Abstract—This article presents a 28-W class-D amplifier for automotive applications. The combination of a high switching frequency and a hybrid multibit  $\Delta \Sigma$ M-PWM scheme results in high linearity over a wide range of output power, as well as low AM-band EMI. As a result, only a small (150-kHz cutoff frequency), and thus low-cost, *LC* filter is needed to meet the CISPR-25 EMI average limit (150 kHz–30 MHz) with 10-dB margin. At 28-W output power, the proposed amplifier achieves 91% efficiency while driving a 4- $\Omega$  load from a 14.4-V supply. It attains a peak THD+N of 0.00077% (-102.2 dB) for a 1-kHz input signal.

Index Terms— $\Delta \Sigma M$ , audio power amplifier, class-D amplifier, electro-magnetic interference (EMI), hybrid, pulsewidth modulation (PWM).

### I. INTRODUCTION

THE trend toward more and more audio channels in modern automobiles is driving the development of highly efficient audio amplifiers with small system size and a low bill-of-materials. Compared with their class-AB counterparts, class-D amplifiers are well suited for such applications due to their high power efficiency (~90%), which makes their thermal management lighter and cheaper.

Compared with class-AB amplifiers, one drawback of class-D amplifiers is the presence of high-frequency switching activity at their outputs. While this is not necessarily an issue in mobile devices [1], it can be quite detrimental to automotive applications. The long cables connecting such amplifiers to their power supplies and speakers can act as antennas for high-frequency switching signals, causing unacceptable levels of electro-magnetic interference (EMI). Consequently, automotive class-D amplifiers are subject to stringent EMI standards, the most common being CISPR-25 [2].

Manuscript received April 24, 2020; revised July 28, 2020; accepted September 1, 2020. Date of publication September 28, 2020; date of current version November 24, 2020. This article was approved by Associate Editor David Blaauw. (*Corresponding author: Qinwen Fan.*)

Shoubhik Karmakar, Huajun Zhang, Qinwen Fan, and Kofi A. A. Makinwa are with the Electronic Instrumentation Laboratory, Microelectronics Department, Faculty of EEMCS, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: q.fan@tudelft.nl).

Robert van Veldhoven and Lucien J. Breems are with NXP Semiconductors, 5656 AE Eindhoven, The Netherlands.

Marco Berkhout is with Goodix Technologies, 6537 TL Nijmegen, The Netherlands.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2020.3023874

EMI is especially problematic when it falls in the AM band (535–1605 kHz). In conventional class-D amplifiers, which are based on fixed-frequency pulsewidth-modulation (PWM), the PWM carrier frequency ( $f_{PWM}$ ) is generally set below 500 kHz to avoid AM-band interference. However, bulky *LC* filters with low cutoff frequencies ( $f_{LC}$  between 20 and 40 kHz) are then required to suppress the resulting PWM tones (harmonics of  $f_{PWM}$ ), leading to significant increases in system size and cost.

In a bid to achieve higher LC cutoff frequencies, while meeting the same EMI standards, and without altering  $f_{PWM}$ , additional measures are required. Examples of these are the use of multilevel or multiphase PWM architectures [3]-[8]. The multiphase architecture described in [3], reduces the ripple current in the speaker cables and, therefore, lowers EMI. However, this is at the cost of two extra inductors per channel, significantly increasing system bulk and cost. Multilevel output stages [5], [6], can also reduce PWM tones by decreasing the voltage swing across the switching nodes. The 7-level output stage in [5] uses each half of an H-bridge output stage to realize two extra levels, thereby reducing PWM tone energy. However, it requires an extra power supply capable of sinking and sourcing large load currents, which significantly increases system size and cost. Similarly, Høyerby et al. [6] realizes one extra level per half H-bridge, at the cost of two external flying capacitors. In general, both multilevel and multiphase architectures also require larger power stages and, hence, more die area to implement the additional low ohmic output switches.

A more cost-effective way to satisfy EMI requirements and relax *LC* cutoff frequency is to increase  $f_{PWM}$  beyond the AM band [9]. Since the unity gain frequency of a stable class-D amplifier must be less than  $f_{PWM}/\pi$  [10], increasing  $f_{PWM}$  enables higher loop gain in the audio band (20 Hz–20 kHz), which, in turn, results in better suppression of output-stage non-linearity. However, increasing  $f_{PWM}$  means that the output stage will have to reproduce narrower pulses. Due to its finite slew rate, however, sufficiently narrow pulses will not be able to swing from rail to rail, thus causing extra non-linearity.

To avoid the narrow pulses produced by conventional PWM, pulse-density-modulation (PDM), using a 1-bit delta– sigma modulator ( $\Delta \Sigma M$ ), can be used [11]. The minimum pulsewidth will then be defined by the modulator's sampling frequency ( $f_S$ ), which can be optimized to prevent slew-rate

0018-9200 © 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

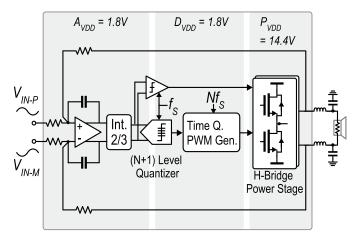

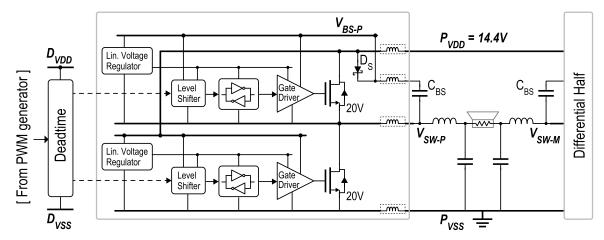

Fig. 1. Simplified block diagram of the fully differential CDA.

distortion, while still being high enough to achieve high loop gain, and thus high linearity. However, a 1-bit  $\Delta \Sigma M$  will typically have a limited stable input range, and its out-of-band (OOB) quantization noise will cause EMI. Simply increasing  $f_S$  to reduce the OOB noise in the AM band will drastically increase the modulator's average switching frequency and, therefore, increase the amplifier's switching losses proportionally. In [11], adding hysteresis to the quantizer of a  $\Delta \Sigma M$ lowers the average switching frequency. However, it will still generate excessive AM-band EMI. Moreover, its loop filter must be dynamically switched from 7th order (for low in-band quantization noise) to 2nd order (to maintain largesignal stability), which complicates its design and degrades large-signal linearity.

This article, an extension of [12], describes a class-D amplifier that employs a hybrid  $\Delta \Sigma$ M-PWM architecture to limit the minimum pulsewidth applied to the output stage, as well as the resulting AM-band EMI. An overview of the fully differential, analog-input class-D amplifier is shown in Fig. 1. It consists of a 3rd order loop filter, followed by a multilevel quantizer, whose output is then applied to a pulsewidth modulator that drives a 2-level output stage. A prototype achieves the stateof-the-art linearity over a wide output power range, while meeting the CRISPR-25 standard with a relaxed *LC* filter, and no additional off-chip components.

This article is organized as follows. Section II introduces the proposed architecture and describes its benefits and challenges. Sections III and IV describe the implementation of the lowand high-voltage blocks, respectively, at the circuit level. Measurement results and comparisons are given in Section V, and the conclusions are summarized in Section VI.

#### **II. MODULATOR ARCHITECTURE**

Compared with their 1-bit counterparts, multilevel  $\Delta \Sigma Ms$  have several advantages, such as reduced OOB noise and a larger stable input range. However, as discussed in the introduction, multilevel output stages are expensive in terms of both silicon area and off-chip components.

In this work, a multilevel  $\Delta \Sigma$  to PWM convertor drives an H-bridge in a bid to achieve the best of both worlds. An (N + 1)-level quantizer converts the loop filter output

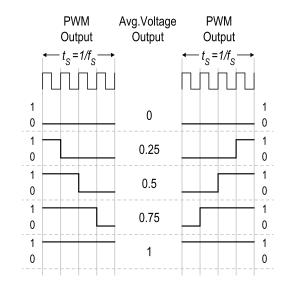

Fig. 2. Generation of time-quantized PWM pulses using a higher clock rate.

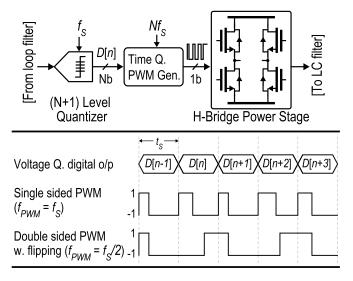

Fig. 3. Time-domain signal path from quantized digital outputs to normalized PWM signals.

into a multilevel digital output, which is then converted into a two-level signal by a PWM generator that outputs a series of 1s and 0s at a higher clock frequency  $f_{CLK} = N \cdot f_S$  [13]. The case when N = 4 is illustrated in Fig. 2, where five different two-level PWM pulses with a period  $t_S$  result in five different average values that can each be assigned to one level of a 5-level quantizer. The main considerations that inform the choice of N and  $f_S$  are the *LC* filter cutoff frequency and its tolerance, the desired in-band SQNR, and the narrowest pulsewidth that the output stage can faithfully reproduce. Each of these considerations will be discussed in detail below.

#### A. Modulation Scheme and Sample-Rate-fs

The signal path from the N-level quantizer to the highvoltage output stage is shown in Fig. 3, along with the normalized time-domain signals. Based on the quantizer's output, the PWM generator serially outputs the appropriate bits at  $f_{\text{CLK}}$ . As shown in Fig. 2, there are two ways of generating

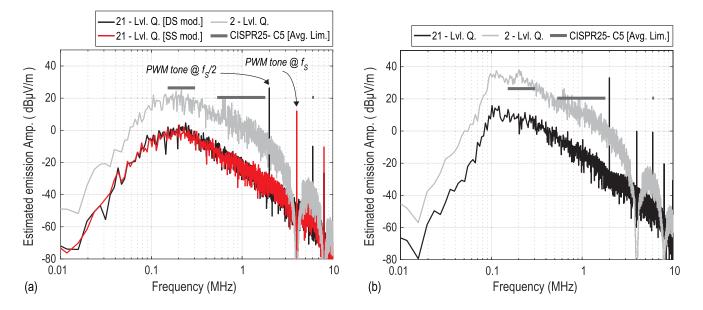

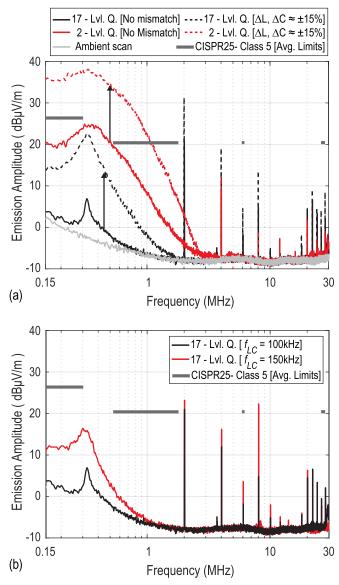

Fig. 4. Simulated estimates out-of-band emission. (a) Comparison of the various modulation schemes. (b) Effect of  $\pm 15\%$  LC mismatch on both the 21-level (DS) hybrid modulation and the conventional 2-level  $\Delta\Sigma M$ .

the same average value in one sample period. Consistently generating all the 1s (or 0s) first results in a single-sided (SS) uniformly sampled PWM (UPWM) signal at a carrier frequency  $f_{PWM} = f_S$  [14]. By alternately reversing the order of the bits, however, a double-sided (DS) signal can be generated, which halves  $f_{PWM}$ , together with the associated switching activity and switching losses. The resulting DS-UPWM signal, with the input sampled at twice the modulation frequency ( $f_S = 2 f_{PWM}$ ), is sometimes also referred to as asymmetric uniform-sampling [15]. In this design, to ensure some margin between the edge of the AM band and the PWM tone, while not incurring excessive switching losses,  $f_{PWM}$  is set to 2 MHz, and so  $f_S = 4$  MHz with DS modulation.

#### B. EMI, LC Filter Cutoff Frequency-f<sub>LC</sub> and Tolerance

Since EM emissions are mainly caused by common-mode (CM) signals, the H-bridge is driven by AD modulated signals [16], [17]. The transitions of each half bridge are in anti-phase, which maintains a constant CM voltage at the output nodes. However, mismatch and timing skews in the two halves lead to some differential mode (DM)-to-CM leakage. Moreover, the use of non-twisted differential cables will cause extra DM-to-CM EMI leakage.

Fig. 4(a) shows the simulated EMI spectrum for different modulation schemes with a relaxed *LC* filter cutoff frequency ( $f_{LC} = 100 \text{ kHz}$ ). A conventional 2-level  $\Delta \Sigma M$  generates a PDM output with a large amount of OOB noise. By increasing the number of quantization levels and using the hybrid modulation technique, the OOB noise is reduced and converted into PWM tones. In this design,  $f_{CLK} = 80$ -MHz clock results in 21 levels, which significantly reduces the OOB noise and positions the PWM tone at 2 MHz. Also, by using DS instead of SS modulation, the amplifier switches at half the frequency for the same OOB noise.

It is worth pointing out that while the 2-level  $\Delta \Sigma M$  appears to (just) satisfy the EMI requirements, this is not the case if LC filter tolerances (up to  $\pm 15\%$ ) are considered. As shown in Fig. 4(b), this results in significantly more DM-to-CM EMI leakage. Under the same conditions, however, the 21-level hybrid modulator still satisfies the EMI requirements with an acceptable margin. Furthermore,  $f_{\rm LC}$  can be made even higher, if tighter component tolerances can be guaranteed. While the amplifier's power supply connections also produce EMI, local supply decoupling is enough to reduce this to negligible levels.

Compared with [3] and [10], the increased switching frequency means that high in-band loop gain can be achieved even with a 3rd order loop filter. As a result, the 21-level modulator achieves an in-band SQNR of  $\sim$ 122 dB and a maximum stable amplitude (MSA) to  $\sim$ 97% FS, which are both significantly larger than the 1-bit case. The end result is a thermal-noise limited design with a high dynamic range.

#### C. Pulsewidth Limitation and Quantizer Non-Uniformity

The multilevel voltage and time quantization described above uniformly distribute 21 bipolar steps (0.1 FS each) across the full scale both in the voltage and time domain. The minimum pulsewidth (12.5 ns) is then determined by  $f_{\rm CLK} = 20 \cdot f_{\rm S} = 80$  MHz. In our design, however, the finite slew rate of the HV output stage and the propagation delay of the driving logic limit minimum pulsewidths to about 16 ns (typical), which worsens across PVT (Section IV). This can be accommodated by decreasing either N or  $f_{\rm S}$ , at the expense of more OOB noise.

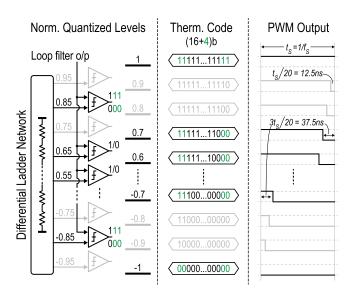

Since audio signals typically have a high crest factor (7–25 dB) [18], [19], they rarely reach FS levels. Therefore, a more pragmatic approach is to make the quantizer nonuniform at high input levels. This can be done by removing the quantization levels of  $\pm$ [0.8;0.9]FS, as illustrated in Fig. 5,

Fig. 5. Limiting the pulsewidth at extremely high modulation index by making the quantizer nonuniform.

Fig. 6. Simplified cross section of the HV N-well used for 1.8-V device isolation.

thus relaxing the minimum pulsewidth requirement by 3x to 37.5 ns. Removing these levels reduces the total number of levels from 20 to 16. To keep the same average output values, the outputs of the two extreme comparators of the flash quantizer are, therefore, 0/1 padded (indicated in green), maintaining a throughput of 20 bits for the  $20 \cdot f_S$  main clock. Although this tradeoff lowers the linear modulation range slightly (to ~93%), the increased OOB noise (due to the increased step size) is negligible for signals close to FS.

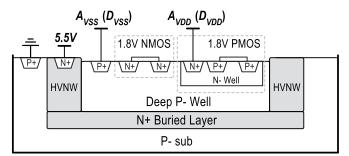

#### **III. LOW-VOLTAGE CIRCUITS**

The digital logic and analog circuits such as loop-filter integrators and quantizer are built using area and power efficient 1.8-V devices. However, due to bond-wire inductance, the high switching currents in the output stage can cause substantial substrate bounce (in the order of several volts). To prevent unwanted substrate coupling, sensitive low-voltage blocks are placed in high-voltage N-wells biased at 5.5 V. As shown in Fig. 6, deep P-wells within the N-wells serve as the local ground ( $A_{VSS}/D_{VSS}$ ) for their respective supply domains.

#### A. 17-Level Quantizer

As illustrated earlier [Fig. 5(b)], a flash ADC is wellsuited for implementing the quantizer. Since it directly outputs a thermometer code that can simply be transmitted to the output stage, the loop delay is kept minimum. Although it is much more power hungry than e.g. an SAR ADC, its power contribution is negligible compared with that of the power stage. Dual-difference comparators [20] were used to implement the quantizer. Non-linearity in the quantizer itself arises due to mismatch in the unit elements of the ladder and the individual offsets of the 16 comparators. Of these two, the ladder references have a  $3\sigma$  spread of ~400  $\mu$ V, while the offset spread is within  $\sim 40$  mV. The gain of the quantizer is optimized to limit the swing of the loop filter output and ensure high linearity, while having a sufficiently large LSB step size ( $V_{LSB} \sim 102 \text{ mV}$ ) to relax the offset requirements of the comparators. Extensive simulations confirm the absence of bubble errors over PVT. In the worst case, the loop gain preceding the quantizer is high enough to maintain an SQNR above 120 dB.

To compare the performance of the hybrid architecture with that of a 1-bit  $\Delta \Sigma M$  with the same loop filter, a 1-bit comparator was incorporated in parallel.

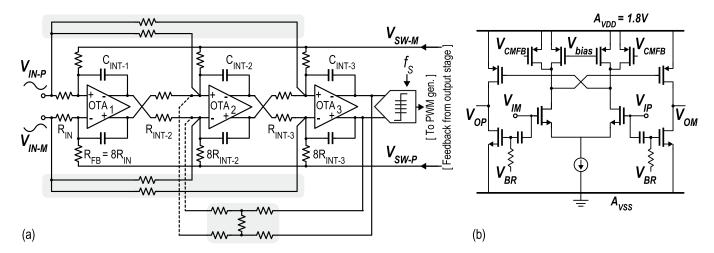

### B. Fully Differential 3rd Order Loop-Filter

As shown in Fig. 7(a), the modulator employs a 3rd order filter. An NTF with optimally placed zeros and an out-of-band gain of 1.8 results in high MSA, low OOB quantization noise, and high loop-gain across the entire audio band [20].

The loop filter is realized as a cascade of highly linear active-RC integrators in a feedback (CIFB) configuration. Direct input feed-ins to the first two integrator's output suppress the audio band component at their outputs and significantly relax their linearity requirements. Due to their low-voltage coefficients, p-poly resistors and high density MIM capacitors are used to realize the various RC time constants. The noise in the audio band is primarily dominated by the 1st integrator, with the input resistors  $R_{\rm IN}$ (=20 k $\Omega$ ) accounting for ~52% of the total noise, while OTA<sub>1</sub> and the feedback resistors  $R_{\rm FB}$  add another ~43%. The input resistance is a compromise between noise considerations and the requirements on the driving capability of a preceding DAC. The feedback resistors set a closed loop gain of  $8 \times (18 \text{ dB})$ . To compensate for RC process spread,  $(\sim 30\%)$ , the capacitors are made 2-bit trimmable that are trimmed manually (once) by observing the OOB-shaped noise content.

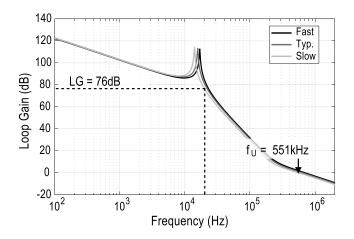

The OTAs [Fig. 7(b)] employ a 2-stage feedforward topology to provide the required gain. A capacitively coupled input feedforward path to the second stage ensures sufficient phase margin and high GBW [21]. Together, the three integrators draw 1.8 mA from the analog supply ( $A_{VDD} = 1.8$  V). After trimming, the filter's overall loop gain at 20 kHz is >76 dB across PVT, as shown in Fig. 8.

It is worth mentioning that the high loop gain also suppresses the adverse effects of clock jitter, which manifests itself in the output pulses as duty cycle errors and degrades audio performance [22]. In this design, up to 1 ns<sub>RMS</sub> clock jitter ( $f_{CLK} = 80$  MHz) can be tolerated to maintain 120-dB SQNR.

Fig. 7. (a) Simplified schematic of the fully differential loop filter. (b) Simplified schematic of the OTA.

Fig. 8. Loop gain of the loop filter across process after trimming.

#### IV. OUTPUT POWER STAGE

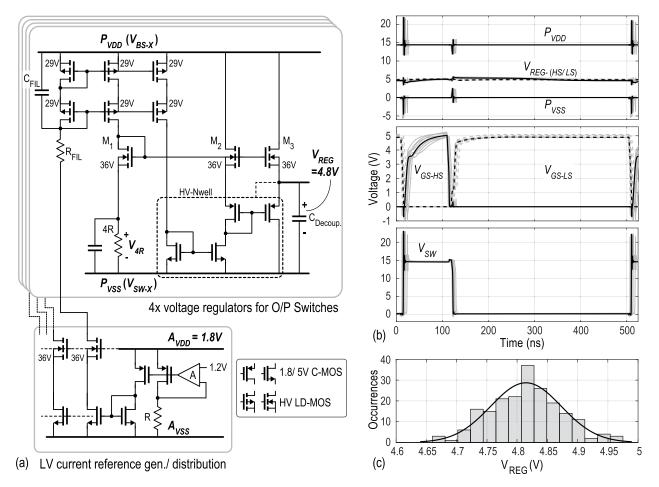

The output power stage consists of a fully differential H-bridge structure and is capable of driving a 4- $\Omega$  BTL, along with associated driving circuits. Fig. 9 shows the circuit with half of it depicted in detail. The primary output switches are laterally diffused 20-V NMOS (N-LDMOS) transistors. The output power stage is responsible for >95% of the total quiescent power consumed in the chip.

Several factors contribute to the overall power dissipation in the output power stage [19], [23]; the dominant ones include conduction loss due to the on resistance of the output transistors ( $R_{ON}$ ) and switching loss due to charging/discharging of gate capacitances ( $C_G$ ). At high power levels, conduction loss dominates due to large signal current. Therefore, all output transistors ( $M_{H/L}$ ) are sized for an  $R_{ON}$  of ~100 m $\Omega$  at 100 °C to obtain an efficiency ~90% close to FS. Meanwhile, the gate charge loss accounts for ~18% of the total losses. It is not worth increasing the output transistor size to further reduce  $R_{ON}$ , as this would result in a large die area and higher idle power consumption, which is dominated by switching loss.

While all the high-voltage LDMOS devices have a high  $V_{\text{DS,MAX}}$  rating, the sensitive nature of their gate oxides limits the maximum allowable  $V_{\text{GS}}$  to 5.5 V. To ensure that the gate

voltages will never exceed this limit, linear voltage regulators are used to generate a localized 4.8-V supply to power all the circuits associated with driving the output switches [24]. This also provides sufficient de-coupling from supply and ground bouncing.

#### A. Linear Voltage Regulators

Since  $R_{ON}$  is relatively insensitive to  $V_{GS}$  variations, provided it has sufficient overdrive (>~3 V), a closed-loop regulation for the gate-driver supply [24] is not required. A more area/power efficient solution, which avoids an HV error amplifier for every regulator, is to use an open-loop structure, as shown in Fig. 10(a). All the regulators share a common 1.2-V reference in the low-voltage section to derive a local 4.8-V reference using 1:1 current mirrors and scaled resistors (R, 4R).  $V_{4R}$  gets further reflected across an output decoupling capacitor ( $C_{\text{Decoup}}$ ) of 12 pF, by maintaining equal current densities across  $M_{1-3}$ , providing a regulated output voltage  $V_{\text{REG}} = V_{4R}$ . The push–pull source-follower architecture provides a low output impedance, which, together with a  $C_{\text{Decoup}}$ , result in a relatively clean  $V_{\text{REG}}$  by sinking/sourcing large transient currents during switching activities.

Fig. 10(b) shows the output waveforms of both the high/low side regulators ( $V_{\text{REG-HS/LS}}$ ) together with the  $V_{\text{GS}}$  of the high-/low-side output switches and the switching node  $V_{\text{SW}}$ . The typical case and variations across PVT are represented in black and gray, respectively.  $V_{\text{REGs}}$  exhibits a transient fluctuation within 250 mV across PVT, and thus guaranteeing safe operation of the output devices and associated circuits. Random mismatch in the resistors and current mirrors causes an additional variation of ~180 mV (3 $\sigma$ ) in  $V_{\text{REG}}$  [Fig. 10(c)], which results in a negligible  $R_{\text{ON}}$  spread of ~1 m $\Omega$ .

The low-side regulators are powered directly from the highvoltage rail ( $P_{VDD}$ ), while the boot-strapped voltages ( $V_{BS-X}$ ) are generated by using internal Schottky diodes ( $D_S$ ) and off-chip capacitors ( $C_{BS}$ ) to power the high-side regulators. All HV LDMOS devices are realized in large isolation N-wells to achieve their ratings, making them area inefficient for small aspect-ratio transistors. Hence, wherever appropriate

Fig. 9. Block diagram of the output power stage together with bonding wires.

Fig. 10. (a) Schematic of the linear voltage regulators for the gate-driving circuits. (b) Output waveforms of the regulated voltage,  $V_{GS}$  of the switches and the output switching node, across process and temperature. (c) Monte Carlo spread in  $V_{REG}$  due to component mismatch.

$(V_{\rm DS} < 5 \text{ V})$ , low-voltage (5 V) devices are used. These are clubbed together in a single floating HV N-well [indicated by the black-dashed boxes in Fig. 10(a)], with the deep P-well acting as the local reference ground.

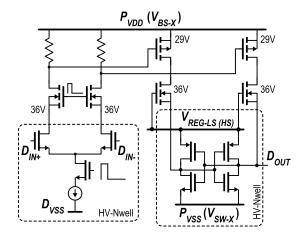

#### B. Level Shifters and Gate Drivers

Level shifters are used to transmit the signals from the digital domain ( $D_{VDD} = 1.8 \text{ V}$ ) to their respective high-voltage domains. High immunity from supply and ground bouncing

can be attained by using a two-step approach similar to [24]. As shown in Fig. 11, complimentary digital signals, initially referred to a relatively clean  $D_{VSS}$ , are first up-shifted to  $P_{VDD}(V_{BS})$  and then down-shifted to the output transistor's reference node  $P_{VSS}$  ( $V_{SW}$ ). The fully differential structure and large headroom between  $D_{VSS}$  and  $P_{VDD}(V_{BS})$  and between  $P_{VDD}(V_{BS})$  and  $P_{VSS}$  ( $V_{SW}$ ) makes this signal transmission robust to high common-mode ringing and prevents output latch errors. A pulsed constant bias current, with a typical

Fig. 11. Schematic of the two-step level shifter.

Fig. 12. (a) Schematic of the gate driver. (b) Associated gate driving signals and delays for turn-ON/OFF phases.

on duration of 15 ns, enables the level shifter shortly before a switching signal arrives at  $D_{IN+/-}$ , resulting in low average quiescent current (number).

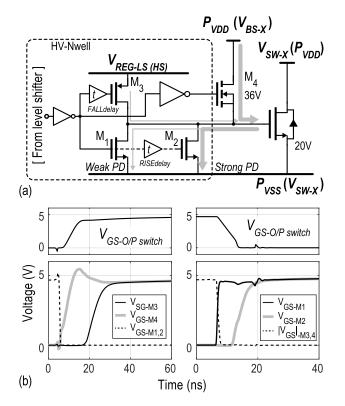

Gate drivers, as shown in Fig. 12(a), are required to reliably charge/discharge the gates of the output transistors. In general, the pull-down strength of a gate driver has to be sufficiently larger than the pull-up strength to avoid cross conduction [25]. However, simply using a strong pull-down would cause an excessive amount of ringing due to large di/dt in the parasitic inductances of the bonding wire. To avoid this situation, a weak pull-down ( $M_1$ ) first discharges the gate, after which, the stronger pull-down ( $M_2$ ) is activated. The associated gatedriving signals are illustrated in Fig. 12(b). For charging

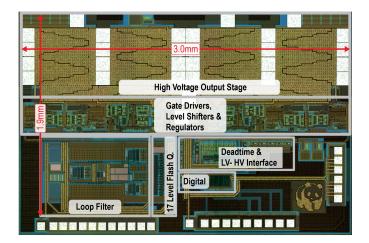

Fig. 13. Die micrograph.

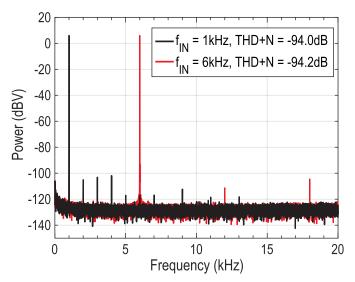

Fig. 14. FFT at 1-W output power across a 4- $\Omega$  load.

the gate, a pull-up using a 36-V N-LDMOS (M<sub>4</sub>) is first activated to charge to gate up to roughly  $V_{\text{REG}}$ - $V_{\text{T}}$  directly from P<sub>VDD</sub> ( $V_{\text{BS}}$ ). A PMOS (M<sub>3</sub>) is then turned on to supply the remaining charge from the regulator. This reduces the regulator loading, reducing the transients on its output voltage. A minimal dead time of 7 ns (with ~±15% variation across process and temperature) ensures no cross-conduction without causing a noticeable degradation in audio performance.

#### V. MEASUREMENT RESULTS

The prototype hybrid class-D amplifier is realized in a TSMC 180-nm BCD bulk process, as shown in Fig. 13. It occupies an active area of 4.8 mm<sup>2</sup>, with the high-voltage switches in the output power stage taking up 40% of the area, while the loop filter, whose area is dominated by the integration capacitors, takes up another 27%. The amplifier can drive a 4- $\Omega$  load and is powered from three separate supplies: A<sub>VDD</sub> / D<sub>VDD</sub> = 1.8 V, and P<sub>VDD</sub> = 14 V. The main external components are the supply de-coupling capacitors (2 × 100 uF) and the *LC* filter with a cutoff frequency  $f_{LC} = 100$  kHz ( $L = 2.2 \mu$ H,  $C = 1.15 \mu$ H).

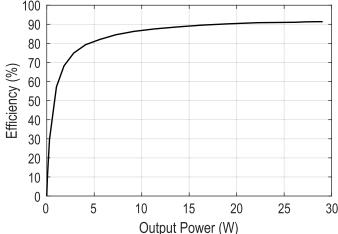

Fig. 16. Efficiency of the amplifier across output power.

During idle-channel operation, the amplifier draws 17 mA from  $P_{VDD}$ , which is primarily due to gate charging losses, and conduction losses due to the ripple current.

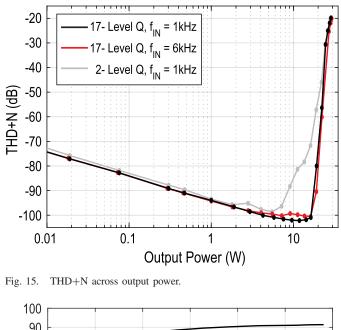

Audio measurements were done using an Audio Precision APX-555 in combination with an AES17 filter. Fig. 14 shows that the measured performance when a 4- $\Omega$  load is driven at 1 W. A noise-limited THD+N of -94.0 and -94.2 dB is achieved at input frequencies of 1 and 6 kHz, respectively. Across output power levels (Fig. 15), the amplifier achieves a peak THD+N of -102.2 and -100.5 dB, for input frequencies of 1 and 6 kHz, respectively, while maintaining a THD+N < -80 dB for output power levels as high as 20 W. When a 1-bit quantizer is used, the  $\Delta \Sigma$  modulator overloads at significantly lower power levels (>8 W). In the 17-level mode, the amplifier has an A-weighted output noise of 31- $\mu$ V<sub>RMS</sub> and a dynamic range of 110.6 dB (A-wt.).

Fig. 16 shows the measured efficiency of the amplifier across output power levels. It attains a peak efficiency of 91% at its full power of 28 W and maintains an efficiency of >90% beyond 20 W.

EMI measurements were carried as per the CISPR-Class 5 standard [2] using a 12-V battery supply and a 4- $\Omega$  load

3153

Fig. 17. Measured EMI of the class-D amplifier. (a) With and Without  $\pm 15\%$  mismatch in L and C and a mean  $f_{LC} = 100$  kHz. (b) Effect of further relaxing the *LC* cutoff frequency to  $f_{LC} = 150$  kHz (without mismatch).

connected to the amplifier using 1.5-m long unshielded and untwisted cables. Fig. 17(a) shows the average radiated emission in the 150-kHz–30-MHz frequency band for different modes and scenarios. In the absence of mismatch in off-chip *LC* components, both the multilevel and 2-level modes are able to satisfy the EMI limits. However, there's hardly any margin for the 2-level mode. To assess the effect of component tolerances and mismatch, additional series/parallel combination of Ls and Cs was used to induce a ±15% mismatch over a nominal  $f_{LC} = 100$  kHz. In this case, while the emission for the 2-level mode exceeds limits, the 17-level mode still maintains 6-dB margin. In the case of tighter component tolerances, the cutoff frequency may be relaxed further, as shown in Fig. 17(b), where an  $f_{LC}$  of 150 kHz without mismatch still maintains 10 dB of margin.

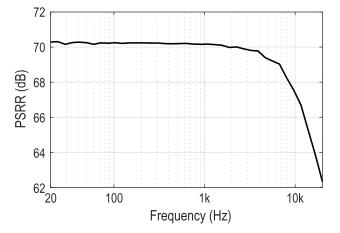

Fig. 18 shows the measured PSRR of the amplifier when its supply is perturbed by a 1  $V_{\text{RMS}}$  sine wave, swept across

| Parameter                                 | This work                         | [3]                       | [5]                      | [6]                      | [9]                  | [11]                | [26]                 |

|-------------------------------------------|-----------------------------------|---------------------------|--------------------------|--------------------------|----------------------|---------------------|----------------------|

| Modulation Scheme                         | Hybrid ∆∑-<br>PWM<br>(Analog In.) | PWM [MP]<br>(Digital In.) | PWM [ML]<br>(Analog In.) | PWM [ML]<br>(Analog In.) | PWM<br>(Digital In.) | ∆∑<br>(Analog In.)  | PWM<br>(Digital In.) |

| Supply                                    | 14.4V                             | 25V                       | 2.5-5V                   | 24V                      | 14.4V                | 12V                 | 8-20V                |

| Load                                      | 4Ω                                | 4Ω                        | 8Ω                       | 4Ω                       | 4Ω                   | 6Ω                  | 8Ω                   |

| THD+N<br>( $f_{IN} = 1kHz$ , $P_O = 1W$ ) | 0.002%                            | 0.004%                    | ~0.0025%                 | ~0.0095%                 | 0.02%                | ~0.0032%            | 0.0029%              |

| Peak THD+N<br>(f <sub>IN</sub> = 1kHz)    | 0.00078%                          | ~0.0037%                  | 0.0023%                  | 0.003%                   | ~0.015%              | ~0.0032%            | 0.0013%              |

| Output Noise (A wt.)                      | 31uVrms                           | 34uVrms                   | -                        | -                        | 42uVrms              | 50uVrms             | 20.5uVrms            |

| Ро-мах (10% ТНD)                          | 28W                               | 80W                       | 10W                      | 70W                      | 27W                  | 10W                 | 20 W                 |

| Efficiency                                | 91%                               | >90%                      | 91%                      | 90%                      | 86%                  | 88%                 | 90%                  |

| Switching Freq.                           | 2.0MHz                            | 0.4MHz                    | 0.7MHz                   | 0.165-0.6MHz             | 2.1MHz               | < 0.7MHz            | 0.4MHz               |

| Comp. Count [L, C]<br>/Values             | 2L, 2C<br>2.2μH, 1.1uF            | 4L, 2C                    |                          | -                        | 2L, 2C<br>3.3μH, 1uF | 2L, 2C<br>15μH, 1uF | 2L, 2C<br>_          |

| LC filter cutoff                          | 100kHz                            | ~40kHz                    | -                        |                          | 88kHz                | 41kHz               | -                    |

| Quiescent Current                         | 17mA                              | 12mA                      | 3.5mA                    | 2.9mA                    | ~40mA                |                     | 20.52mA              |

| PSRR (20-20kHz)                           | 70-62dB                           | ~100-60dB<br>(88dB@100Hz) | ~88dB<br>(@217Hz)        | -                        | ~75-57dB             | ~68-39dB            | 80-50dB              |

| Area/ Channel                             | 4.8mm <sup>2</sup>                | -                         | 6.4mm <sup>2</sup>       | 6.7mm <sup>2</sup>       | -                    | 10.1mm <sup>2</sup> | -                    |

| Process                                   | 180nm BCD                         | 140nm<br>BCD SOI          | 180nm<br>BCD             | 180nm BCD                | -                    | 600nm<br>BCD        | 180nm<br>BCD         |

TABLE I

Performance Summary and Comparison With Previous Works

Fig. 18. PSRR of the amplifier across supply perturbation frequency.

frequency. At low frequencies, the PSRR is 70 dB and is mainly limited by the matching of the resistors. Toward the edge of the audio band, a PSRR > 60 dB is maintained.

A comparison of the performance of this amplifier with other state-of-the-art designs is shown in Table I.

#### VI. CONCLUSION

A class-D amplifier incorporating a hybrid  $\Delta \Sigma$ M-PWM modulation scheme is presented. Multilevel quantization using

$\Delta \Sigma M$  followed by time-quantized PWM generation drastically reduces the out-of-band EM emission compared with a 1-bit  $\Delta \Sigma M$  class-D amplifier, allowing the use of a relaxed *LC* cutoff frequency with relaxed component tolerances. A high loop gain, enabled due to the high sample rate, together with a robust output stage that delivers well-defined quantized pulses, ensures high linearity of the amplifier across a wide output power range. Overall, the class-D amplifier achieves the stateof-the-art performance with a peak THD+N of -102.2 dB and a peak efficiency greater than 90%. In addition to [12], it is shown that the *LC* cutoff frequency can be pushed as high as 150 kHz to satisfy the CISPR-25 average EMI limit [150 kHz–30 MHz], while still maintaining some margin.

#### ACKNOWLEDGMENT

The authors would like to thank Z. Chang, L. Pakula, and R. van Puffelen from the Delft University of Technology, Delft, The Netherlands, and Q. Sandifort from NXP, Nijmegen, The Netherlands, for the help and assistance with PCB assembly, testing, and measurements.

#### REFERENCES

M. Berkhout and L. Dooper, "Class-D audio amplifiers in mobile applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 5, pp. 992–1002, May 2010.

- [2] Vehicles; Boats and Internal Combustion Engines—Radio Disturbance Characteristics- Limits and Methods of Measurement for the Protection of on-Board Receivers, document CISPR 25:2016, 4th ed. (or EN 55025:2017) Oct. 2016.

- [3] D. Schinkel *et al.*, "A multiphase class-D automotive audio amplifier with integrated low-latency ADCs for digitized feedback after the output filter," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3181–3193, Dec. 2017.

- [4] K. Nielsen, "Parallel phase-shifted carrier pulse-width modulation (PSCPWM)—A novel approach to switching power amplifier design," in *Proc. 102nd Conv. Audio Eng. Soc.*, Munich, Germany, Mar. 1997, Paper 4447.

- [5] J.-H. Lee *et al.*, "5.2 an 8Ω 10W 91%-power-efficiency 0.0023%-THD+N multilevel class-D audio amplifier with folded PWM," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2017, pp. 88–89.

- [6] M. Hoyerby, J. K. Jakobsen, J. Midtgaard, and T. H. Hansen, "A 2×70 w monolithic five-level class-D audio power amplifier in 180 nm BCD," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 2819–2829, Dec. 2016.

- [7] P. Siniscalchi and R. K. Hester, "A 20 W/channel class-D amplifier with near-zero common-mode radiated emissions," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3264–3271, Dec. 2009.

- [8] C. Cerutti, "Multilevel class-D amplifier," U.S. Patent 8558617 B2, Oct. 15, 2013.

- [9] Texas Instruments. (Oct. 2017). TAS6424-Q1 Datasheet. [Online]. Available: http://www.ti.com/lit/ds/symlink/tas6424-q1.pdf

- [10] M. Berkhout, "An integrated 200-w class-D audio amplifier," *IEEE J. Solid-State Circuits*, vol. 38, no. 7, pp. 1198–1206, Jul. 2003.

- [11] E. Gaalaas, B. Y. Liu, N. Nishimura, R. Adams, and K. Sweetland, "Integrated stereo ΔΣ class D amplifier," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2388–2397, Dec. 2005.

- [12] S. Karmakar *et al.*, "23.4 A 28 W -108.9 dB/-102.2 dB THD/THD+N hybrid ΔΣ-PWM class-D audio amplifier with 91% peak efficiency and reduced EMI emission," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2020, pp. 350–352.

- [13] A. Kalb, "Apparatus and method for converting analog signal to pulsewidth-modulated signal," U.S. Patent 6970503 B1, Nov. 5, 2005.

- [14] K. Nielsen, "A review and comparison of pulse width modulation (PWM) methods for analog and digital input switching power amplifiers," in *Proc. 102nd Conv. Audio Eng. Soc.*, Munich, Germany, Mar. 1997, pp. 1–57.

- [15] G. Franzo, M. Mazzucchelli, L. Puglisi, and G. Sciutto, "Analysis of PWM techniques using uniform sampling in variable-speed electrical drives with large speed range," *IEEE Trans. Ind. Appl.*, vol. IA-21, no. 4, pp. 966–974, Jul. 1985.

- [16] J. D. Martin, "Theoretical efficiencies of class-D power amplifiers," *Proc. Inst. Electr. Eng.*, vol. 117, no. 6, pp. 1089–1090, Jun. 1970.

- [17] T. Karaca and B. Deutschmann, "Electromagnetic evaluation of Class-D switching schemes," in *Proc. 11th Conf. Ph.D. Res. Microelectron. Electron. (PRIME)*, Jun. 2015, pp. 113–116.

- [18] R. van der Zee and A. J. M. van Tuijl, "Test signals for measuring the efficiency of audio amplifiers," in *Proc. 104th Conv. Audio Eng. Soc.*, Amsterdam, The Netherlands, May 1998.

- [19] N. E. Iversen, A. Knott, and M. A. E. Andersen, "Efficiency of switch mode power audio amplifiers—Test signals and measurement techniques," in *Proc. 140th Conv. Audio Eng. Soc.*, Paris, France, Jun. 2016.

- [20] R. Schreier and G. C. Temes, Understanding Delta-Sigma Data Converters, Piscataway, NJ, USA: Wiley, 2005.

- [21] C.-Y. Ho, C. Liu, C.-L. Lo, H.-C. Tsai, T.-C. Wang, and Y.-H. Lin, "A 4.5 mW CT self-coupled ΔΣ modulator with 2.2 MHz BW and 90.4 dB SNDR using residual ELD compensation," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 2870–2879, Dec. 2015.

- [22] M. Berkhout, "Clock jitter in class-D audio power amplifiers," in *Proc. ESSCIRC 33rd Eur. Solid-State Circuits Conf.*, Sep. 2007, pp. 444–447.

[23] H. Ma, R. van der Zee, and B. Nauta, "A high-voltage class-D

- [23] H. Ma, R. van der Zee, and B. Nauta, "A high-voltage class-D power amplifier with switching frequency regulation for improved highefficiency output power range," *IEEE J. Solid-State Circuits*, vol. 50, no. 6, pp. 1451–1462, Jun. 2015.

- [24] H. Ma, R. van der Zee, and B. Nauta, "Design and analysis of a highefficiency high-voltage class-D power output stage," *IEEE J. Solid-State Circuits*, vol. 49, no. 7, pp. 1514–1524, Jul. 2014.

- [25] M. Berkhout, "A class d output stage with zero dead time," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2003, pp. 134–135.

- [26] E. Cope et al., "A 2×20 W 0.0013% THD+N class-D audio amplifier with consistent performance up to maximum power level," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2018, pp. 56–57.

**Shoubhik Karmakar** (Graduate Student Member, IEEE) received the B.E. degree in electrical and electronics engineering from the Birla Institute of Technology and Science, Goa, India, in 2012, and the M.Sc. degree from the Delft University of Technology, Delft, The Netherlands, in 2017, where he is currently pursuing the Ph.D. degree.

His current research interests include energyefficient data converters and high-performance class-D amplifiers for audio applications.

Huajun Zhang (Graduate Student Member, IEEE) received the B.E. degree in electrical and computer engineering from Shanghai Jiao Tong University, Shanghai, China, in 2015, and the B.S.E. and M.S. degrees in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2015 and 2017, respectively. He is currently pursuing the Ph.D. degree with the Delft University of Technology, Delft, The Netherlands.

In summer 2016, he was an Analog/Mixed-Signal Design Intern with Analog Devices, Inc.,

Wilmington, MA. From May 2017 to February 2019, he was a Mixed-Signal Design Engineer with Analog Devices, Inc., Norwood, MA. He joined the Electronic Instrumentation Laboratory, Delft University of Technology, in March 2019. He holds one U.S. patent. His technical interests include precision analog circuits, class-D audio amplifiers, and ultralow-power data converters for sensor interfaces.

Mr. Zhang has served as a Reviewer for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: REGULAR PAPERS and the IEEE SENSORS JOURNAL.

**Robert van Veldhoven** (Senior Member, IEEE) was born in Eindhoven, The Netherlands, in 1972. He received the Ph.D. degree in electrical engineering from the University of Eindhoven, Eindhoven.

In 1996, he joined Philips Research, Nijmegen, The Netherlands, and joined to NXP Semiconductors, Eindhoven, in 2006, where he is currently a Data Converter Fellow and Architect leading a team of 15 engineers working on automotive grade data converters and sensor interfaces. He holds over 25 U.S. patents. He has (co-) authored more than 15 ISSCC/JSSC articles.

Lucien J. Breems (Fellow, IEEE) received the M.Sc. degree (*cum laude*) and the Ph.D. degree in electrical engineering from the Delft University of Technology, Delft, The Netherlands, in 1996 and 2001, respectively.

From 2000 to 2006, he was with Philips Research, Nijmegen, The Netherlands, and in 2007, he joined NXP Semiconductors, Eindhoven. Since 2011, he has been a Part-Time Professor with the Technical University of Eindhoven, Eindhoven, The Netherlands.

Dr. Breems is/has been a member of the Technical Program Committees of the International Solid-State Circuits Conference (ISSCC), European Solid-State Circuits Conference (ESSCIRC), the Symposium on VLSI Circuits, and the IEEE International Symposium on Low Power Electronics and Design (ISLPED). From 2009 to 2015, he served as an Associate Editor and in 2020 as a Guest Editor for the IEEE JOURNAL OF SOLID-SATE CIRCUITS, and he was a Guest Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II from 2008 to 2009. He received the ISSCC Jan van Vessem Outstanding European Paper Award in 2001, 2011, 2016, the RFIC Symposium Industry Best Paper award in 2016, and the IEEE JOURNAL OF SOLID-STATE CIRCUITS Best Paper Award in 2011, 2016. He has been the IEEE Distinguished Lecturer from 2012 to 2013.

**Marco Berkhout** (Member, IEEE) received the M.Sc. degree in electrical engineering and the Ph.D. degree from the University of Twente, Enschede, The Netherlands, in 1992 and 1996, respectively.

From 1996 to 2019, he was with Philips/NXP Semiconductors, Nijmegen, The Netherlands. He is currently a fellow with Goodix Technology, Nijmegen. His main interests are class-D amplifiers and integrated power electronics.

Dr. Berkhout has been a member of the Technical Program Committees of ESSCIRC, 2008–2018 and

ISSCC, 2013–2016, 2021. He received the 2002 ESSCIRC Best Paper Award and was plenary Invited Speaker on audio at low and high power at the 2008 ESSCIRC Conference.

**Qinwen Fan** (Senior Member, IEEE) received the B.Sc. degree in electronic science and technology from Nankai University, Tianjin, China, in 2006, and the M.Sc. degree (*cum laude*) and the Ph.D. degree in microelectronics from the Delft University of Technology, Delft, The Netherlands, in 2008 and 2013, respectively

From August 2007 to August 2008, she was an Intern with NXP Research Laboratories, Eindhoven, The Netherlands, where she designed a precision instrumentation amplifier for biomedical purposes.

From October 2012 to May 2015, she worked at Maxim Integrated Products, Delft. From June 2015 to January 2017, she worked at Mellanox, Delft. Since 2017, she rejoined the Delft University of Technology, where she is currently an Assistant Professor with the Electronics and Instrumentation Laboratory. Her current research interests include precision analog, class D audio amplifiers, dc–dc converters for energy harvesters, and current-sensing amplifiers.

Dr. Fan serves as a TPC Member for European Solid-State Circuits Conference and a Reviewer for the IEEE JOURNAL OF SOLID-STATE CIRCUITS.

Kofi A. A. Makinwa (Fellow, IEEE) received the B.Sc. and M.Sc. degrees from Obafemi Awolowo University, Ife, Nigeria, in 1985 and 1988, respectively, the M.E.E. degree from Philips International Institute, Eindhoven, The Netherlands, in 1989, and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2004.

From 1989 to 1999, he was a Research Scientist with Philips Research Laboratories, Eindhoven, where he worked on interactive displays and digital recording systems. In 1999, he joined the Delft

University of Technology, where he is currently an Antoni van Leeuwenhoek Professor and the Head of the Microelectronics Department. This has resulted in 16 books and over 250 technical articles. He holds over 30 patents. His research interests include the design of mixed-signal circuits, sensor interfaces, and smart sensors.

Dr. Makinwa is a member of the Royal Netherlands Academy of Arts and Sciences and the Editorial Board of the PROCEEDINGS OF THE IEEE. He is a co-recipient of 15 Best Paper Awards, including two from the IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC) and three from the International Solid-State Circuits Conference (ISSCC). At the 60th anniversary of ISSCC, he was recognized as a Top-Ten Contributor. He has been on the Program Committees of several IEEE conferences and has served the IEEE Solid-State Circuits Society as a Distinguished Lecturer and as an Elected member of its AdCom. He has also served as a Guest Editor for the IEEE JOURNAL OF SOLID-STATE CIRCUITS (JSSC). He is currently the Analog Subcommittee Chair of the ISSCC and a Co-Organizer for the Advances in Analog Circuit Design (AACD) Workshop and the Sensor Interfaces Meeting.