**Delft University of Technology**

# Spin-in of RISC-V Processors in Space Embedded Systems

Di Mascio, S.

DOI 10.4233/uuid:e515547e-62bc-4893-b299-87c1286b5d55

Publication date 2022

**Document Version** Final published version

Citation (APA) Di Mascio, S. (2022). Spin-in of RISC-V Processors in Space Embedded Systems. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:e515547e-62bc-4893-b299-87c1286b5d55

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

#### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# SPIN-IN OF RISC-V PROCESSORS IN SPACE EMBEDDED SYSTEMS

# SPIN-IN OF RISC-V PROCESSORS IN SPACE EMBEDDED SYSTEMS

# Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus prof.dr.ir. T.H.J.J. van der Hagen chair of the Board for Doctorates to be defended publicly on Monday 12 September 2022 at 15:00 o'clock

by

# Stefano DI MASCIO

Master of Science in Electronics Engineering, University of Rome "Tor Vergata", Rome, Italy, born in Rome, Italy. This dissertation has been approved by the promotors:

promotor: Prof. dr. E.K.A. Gill copromotor: Dr. A. Menicucci

Composition of the doctoral committee:

| Rector Magnificus,      | chairperson                                |

|-------------------------|--------------------------------------------|

| Prof. dr. E.K.A. Gill , | Delft University of Technology, promotor   |

| Dr. A. Menicucci,       | Delft University of Technology, copromotor |

## Independent Members:

| Prof. dr. O. Mutlu,     | ETH Zürich                     |

|-------------------------|--------------------------------|

| Prof. dr. H.P. Hofstee, | Delft University of Technology |

| Prof. dr. G. Setti,     | Politecnico di Torino          |

| Dr. S. Wong,            | Delft University of Technology |

| J. Andersson (MSc),     | Cobham Gaisler                 |

*Reserve Member:* Prof. dr. A.J. van der Delft University of Technology Veen,

This research was funded by Cobham Gaisler and the European Space Agency.

| Keywords:     | Satellite Data Systems, Processors, Fault Tolerance, Space Systems, Ar-  |  |

|---------------|--------------------------------------------------------------------------|--|

|               | tificial Intelligence, RISC-V, Application Specific Integrated Circuits, |  |

|               | Small Satellites                                                         |  |

| Printed by:   | Ipskamp printing                                                         |  |

| Front & Back: | Gustaf Wilhelm Palm, View of the Tuscolo theater (1852)                  |  |

Copyright © 2022 by Stefano Di Mascio

ISBN 978-94-6421-851-0

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

I suppose it is tempting, if the only tool you have is a hammer, to treat everything as if it were a nail.

Abraham Maslow, The Psychology of Science: A Reconnaissance (1966)

# **CONTENTS**

| Sı | imm     | ry                                                            | xi   |

|----|---------|---------------------------------------------------------------|------|

| Sa | ımen    | atting                                                        | xiii |

| Li | st of . | bbreviations                                                  | xvii |

| 1  | Intr    | duction                                                       | 1    |

|    | 1.1     | Background                                                    | 2    |

|    | 1.2     | Concepts of Computer Architecture.                            | 3    |

|    |         | 1.2.1 Parallelism                                             | 3    |

|    |         | 1.2.2 Speculation                                             | 8    |

|    |         | 1.2.3 Memory Subsystem                                        | 9    |

|    |         | 1.2.4 Measuring Performance                                   | 10   |

|    | 1.3     | Dependability of Processors for Space Applications            | 12   |

|    |         | 1.3.1 Faults due to radiation                                 | 12   |

|    |         | 1.3.2 Redundancy                                              | 17   |

|    |         | 1.3.3 Error Detection And Correction codes                    | 17   |

|    |         | 1.3.4 Hardware replication                                    | 20   |

|    | 1.4     | State of the Art of Space-Grade Processors                    | 21   |

|    |         | 1.4.1 Performance                                             | 22   |

|    |         | 1.4.2 Fault Tolerance                                         | 26   |

|    | 1.5     | Motivation                                                    | 26   |

|    |         | 1.5.1 Spin-in of developments for terrestrial applications    | 27   |

|    |         | 1.5.2 The RISC-V ISA                                          | 27   |

|    | 1.6     | Research Questions, Methodologies, and Thesis Structure       | 28   |

| 2  | Def     | efinition of RISC-V processors needed in space data systems 3 |      |

|    | 2.1     | Analysis of the RISC-V ISA                                    | 34   |

|    |         | 2.1.1 Modularity                                              | 34   |

|    |         | 2.1.2 Simplicity                                              | 35   |

|    |         | 2.1.3 Extendability                                           | 36   |

|    |         | 2.1.4 <b>Openness</b>                                         | 36   |

|    | 2.2     | Processors for Satellite Data Systems                         | 38   |

|    |         | 2.2.1 On-Board Computers                                      | 39   |

|    |         | 2.2.2 Microcontrollers                                        | 42   |

|    |         | 2.2.3 General-purpose processors                              | 46   |

|    |         | 2.2.4 Processors for On-Board Decision Making                 | 47   |

|    | 2.3     | RISC-V Roadmap for Space Applications                         | 52   |

|    |         | 2.3.1 RISC-V profiles                                         | 52   |

|    |         | 2.3.2 From the RISC-V ISA to Flight-Proven Processors         | 53   |

|   |     | Prioritization and synergies                                     | ) |

|---|-----|------------------------------------------------------------------|---|

|   | 2.5 | Summary                                                          | ) |

| 3 | Cos | t-Effective Redundancy to Mitigate the Effects of Soft Errors 63 | 3 |

|   |     | Introduction                                                     | 1 |

|   |     | Outline                                                          | 1 |

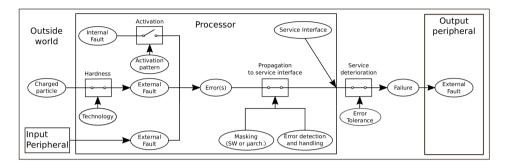

|   |     | Modelling Threats                                                | 5 |

|   |     | 3.3.1 Fault and Error Models                                     | 5 |

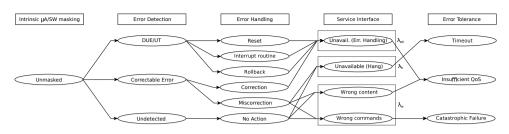

|   |     | 3.3.2 Error Propagation to the Service Interface                 | 3 |

|   |     | 3.3.3 Service Interface and Error Tolerance                      | 7 |

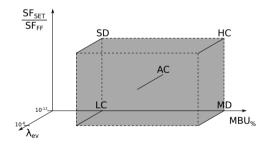

|   | 3.4 | Modelling the vulnerability of processors                        | 9 |

|   |     | 3.4.1 AVF decomposition                                          | 9 |

|   |     | 3.4.2 Impact of the Microarchitecture on the Failure Rate        | 2 |

|   |     | 3.4.3 Impact of other factors on the failure rate                | 7 |

|   |     | 3.4.4 Limitation of the model                                    | 9 |

|   | 3.5 | Evaluation of redundancy.81                                      | 1 |

|   |     | 3.5.1 Choice of redundancy for cache arrays                      | 3 |

|   |     | 3.5.2 Choosing the redundancy for the rest of the processor 85   | 5 |

|   | 3.6 | Expected in-orbit behavior and validation                        | ) |

|   |     | 3.6.1 Validation                                                 |   |

|   | 3.7 | Summary                                                          | 2 |

| 4 | Ana | lysis of Workloads for On-Board Decision Making 95               | 5 |

|   | 4.1 | Introduction                                                     | 3 |

|   |     | System-level impact                                              | 3 |

|   |     | 4.2.1 Downlink efficiency                                        | 7 |

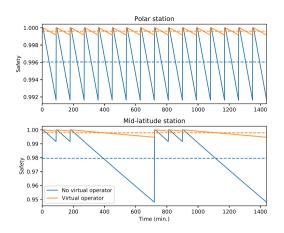

|   |     | 4.2.2 On-board Virtual operator                                  | 9 |

|   | 4.3 | Algorithms                                                       | 1 |

|   |     | 4.3.1 Supervised Learning                                        |   |

|   |     | 4.3.2 Unsupervised Learning                                      |   |

|   | 4.4 | Workloads                                                        |   |

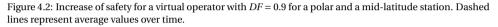

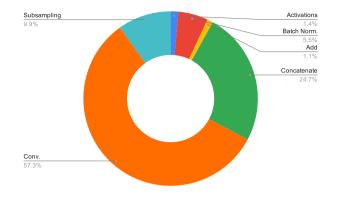

|   |     | 4.4.1 CloudNet                                                   |   |

|   |     | 4.4.2 Other layers in DNNs for image analysis                    |   |

|   |     | 4.4.3 Recurrent Neural Networks                                  |   |

|   |     | 4.4.4 Unsupervised Learning                                      |   |

|   | 4.5 | Summary                                                          | 3 |

| 5 | Ana | lysis of Potential and Challenges of Vector Processors 115       | 5 |

|   | 5.1 | Introduction                                                     | 3 |

|   |     | 5.1.1 Proposed Approach                                          |   |

|   |     | 5.1.2 Data-Parallel Instruction Set Architectures                |   |

|   |     | 5.1.3 Outline                                                    |   |

|   | 5.2 | The RISC-V Vector Extension                                      |   |

|   |     | 5.2.1 Vector registers                                           |   |

|   |     | 5.2.2 Configuration and Status Registers                         |   |

|   |     | 5.2.3 Operations                                                 |   |

|   |     | 5.2.4 Exceptions                                                 | 2 |

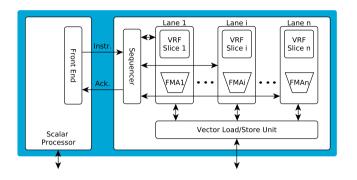

|            | 5.3     | Microarchitecture of Vector Processors                    |       |

|------------|---------|-----------------------------------------------------------|-------|

|            |         | 5.3.1 Vector register file                                |       |

|            |         | 5.3.2 Scalability                                         |       |

|            |         | 5.3.3 Dependability                                       |       |

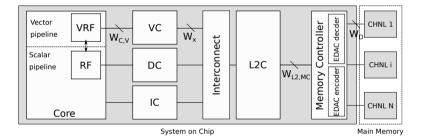

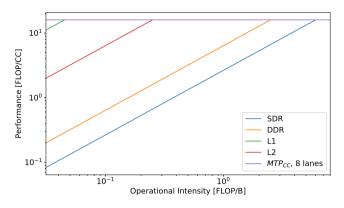

|            | 5.4     | Memory Hierarchy                                          |       |

|            |         | 5.4.1 Main Memory                                         |       |

|            |         | 5.4.2 L1 Vector Cache                                     |       |

|            | 5.5     | CloudNet Kernels for RISC-V Vector Processors             |       |

|            |         | 5.5.1Methodology.5.5.2Implementation of the Kernels.      |       |

|            | 5.6     | 5.5.2 Implementation of the Kernels                       |       |

|            |         |                                                           | . 155 |

| 6          |         | ign of a Vector Processor Based on the NOEL-V Platform    | 155   |

|            | 6.1     | Introduction                                              |       |

|            |         | 6.1.1 Goal, Methodology and Outline                       |       |

|            | 0.0     | 6.1.2 Requirements                                        |       |

|            | 6.2     | Implementation of the Vector Processing Unit              |       |

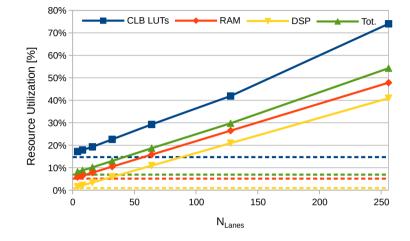

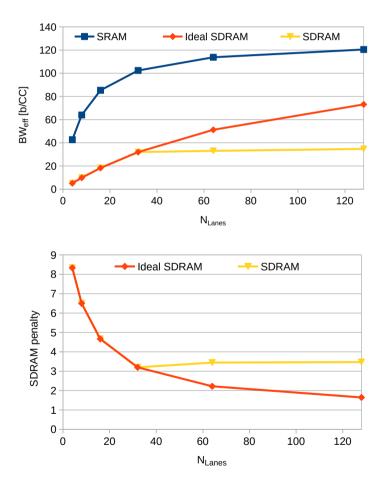

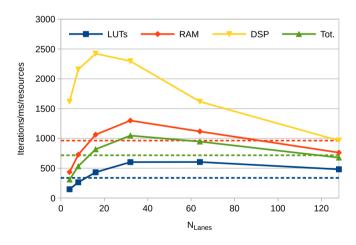

|            |         | 6.2.1 Resource Utilization         6.2.2 Memory Subsystem |       |

|            | 6.3     | 6.2.2 Memory Subsystem                                    |       |

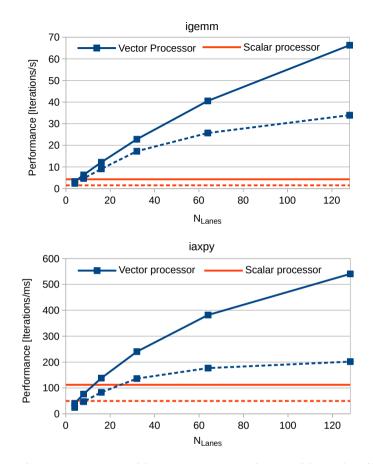

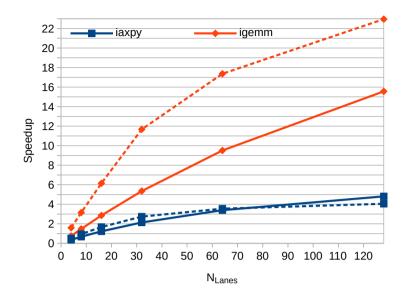

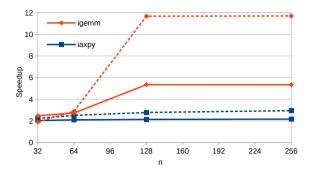

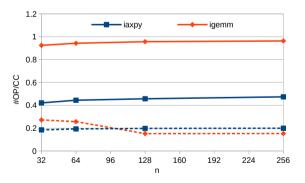

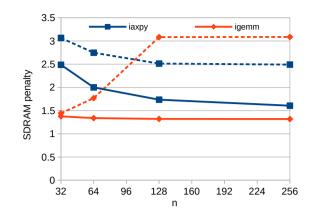

|            | 0.5     | 6.3.1 Results                                             |       |

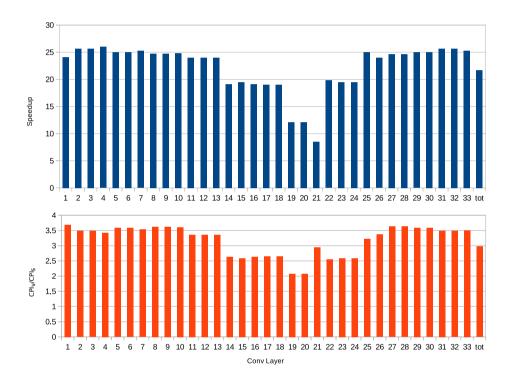

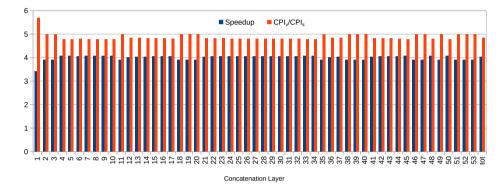

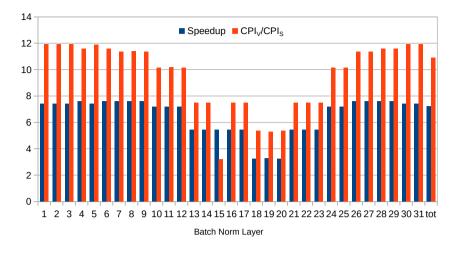

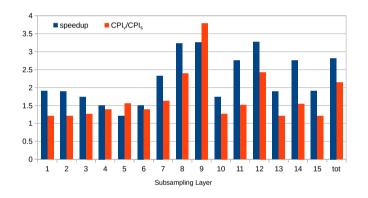

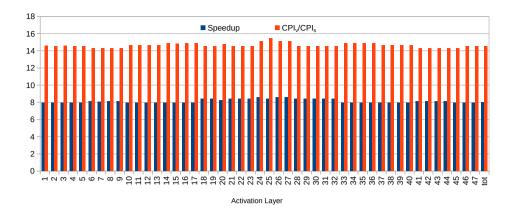

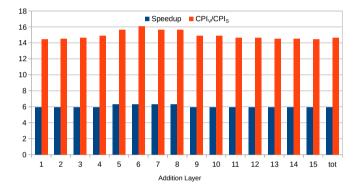

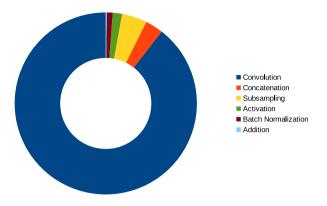

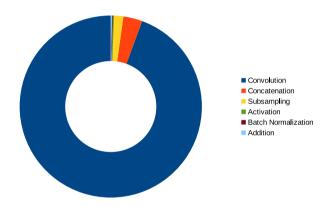

|            |         | 6.3.2 Performance Improvements for CloudNet kernels       |       |

|            | 6.4     | Requirements Verification                                 |       |

|            | 6.5     | Related Work                                              |       |

|            |         | 6.5.1 Comparison with other DLP processors                |       |

|            |         | 6.5.2 Benchmarking Methodology.                           |       |

|            | 6.6     | Summary                                                   | . 179 |

| 7          | Con     | clusion                                                   | 181   |

| •          | 7.1     | Summary                                                   |       |

|            | ••-     | Answers to Research Questions                             |       |

|            | 7.3     | Innovations and Contributions                             |       |

|            | 7.4     | Recommendations and Future Work                           |       |

| <b>D</b> - |         |                                                           |       |

| Re         | ferer   | ICes                                                      | 187   |

| Ac         | knov    | vledgements                                               | 219   |

| Cu         | ırricı  | ılum Vitæ                                                 | 221   |

| Li         | st of I | Publications                                              | 223   |

# **SUMMARY**

The usage of terrestrial processors in space applications is not straightforward, as processors in space face unique challenges due to the effects of the space environment, like ionizing radiation causing Single Event Effects (SEEs). In the nineties, the European Space Agency chose the Scalable Processor ARChitecture (SPARC) Instruction Set Architectures (ISA) for its processors, as it was the only solution available at that time providing both openness and available software support in terrestrial applications. Currently, a large part of the worldwide space community is using SPARC-based radiation-hardened (rad-hard) or radiation-tolerant (rad-tol) LEON processors in ongoing and planned missions, although SPARC processors virtually disappeared from terrestrial applications. Rad-hard and rad-tol processors for space applications typically lag more than a decade behind their commercial counterparts in terms of performance and the gap is widening every year. This is mainly due to the use of Rad-Hard-By-Design (RHBD) cells and older technology nodes. The larger vulnerability to SEEs of complex microarchitectures is not the only reason why simple microarchitectures with low parallelism are still the vast majority of processors employed in space. As a matter of fact, most of the tasks executed by processors in space data systems are non-compute-intensive workloads. The reason is that they are mainly employed for non-demanding control and housekeeping operations. Therefore, enabling demanding tasks, such as the execution of Artificial Intelligence (AI) algorithms in space embedded systems, requires a large leap in spacegrade processors, especially because space data systems in satellites are typically powerconstrained.

Recently, RISC-V, a novel free and open ISA, has risen in popularity in terrestrial applications, drawing the attention of several universities and companies. Given the similarity between SPARC and RISC-V, this dissertation starts by analyzing the advantages of using RISC-V in space applications. The openness of RISC-V already enabled a vast field of research activities for terrestrial applications, with many tools and models at different level of abstraction already available. Therefore, the space industry can spin-in developments from academia and industry, focusing efforts mainly on improvements concerning specific needs in space applications and without wasting efforts on other activities. In order to fully exploit modularity, the need of defining the types of processors required in space application was identified in this dissertation. The modularity of RISC-V was employed to identify several applications in space data systems and RISC-V processor profiles to address them. They were defined in this work by the ISA subset, Instruction-Level Parallelism (ILP), Data-Level Parallelism (DLP), Processor-Level Parallelism (PLP), reference implementation and expected performance. The processors profiles defined range from microcontrollers to general-purpose implementations to high-performance processors for AI. Finally, a roadmap to bring RISC-V IP cores for terrestrial applications to space level was defined, identifying the steps and models required.

After the thorough analysis of the state-of-the-art of RISC-V processors was completed, two different sets of activities were identified.

- 1. Increase the fault tolerance of microarchitectures of next-generation space processors: In order to do this, a literature study was carried out and a model to evaluate the vulnerability of microarchitectures to SEEs was developed. During the creation of this model, it was found that the most impacting factors on the SEE vulnerability are technology, environment and microarchitecture. The most vulnerable parts identified in both next-generation and state-of-the-art processors were caches, mainly because of the large area occupied. For this reason, addressing the upsets in caches reduces failure rate for state-of-the-art and next-generation processors by 96% and 93% respectively. Several redundancy techniques were introduced and their effect on microarchitectures similar to state-of-the art and nextgeneration space processors were evaluated with this model.

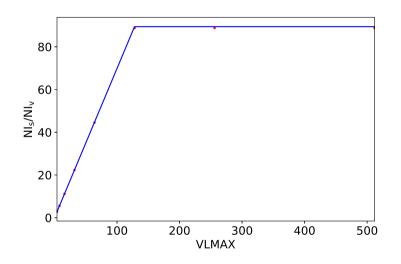

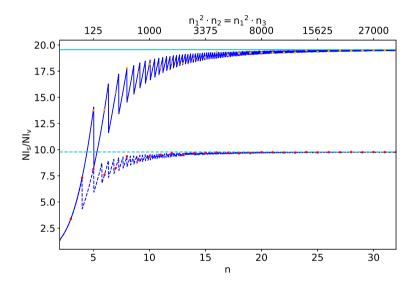

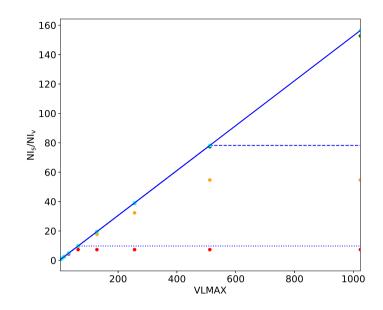

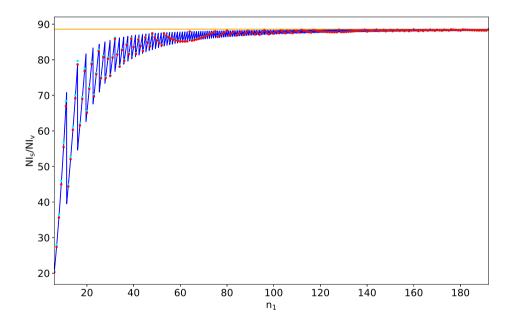

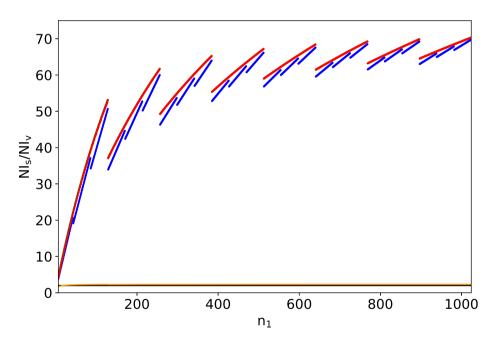

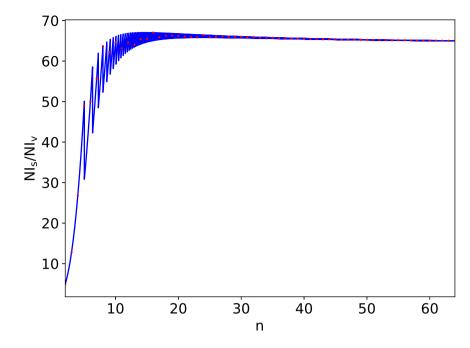

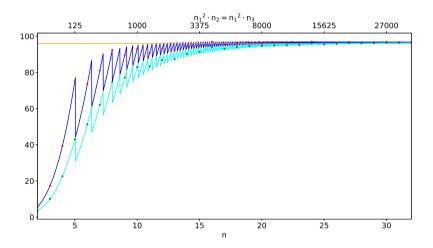

- 2. Increase performance of next-generation processors: Instead of focusing on the optimization of existing microarchitecures, the focus here was on identifying new types of applications for space processors for which performance can be dramatically improved by new microarchitectures, as state-of-the-art processors were not designed to execute them efficiently. An analysis of the requirements of processors to execute Deep Neural Networks (DNNs) was performed. Then, a study of compute-intensive workloads required for execution of DNNs was carried out, based on the case study of CloudNet, a DNN for cloud detection. Since it was found that the workload is largely composed by matrix operations, the RISC-V Vector Extension (RVVE) was proposed to speedup the execution of these matrix operations. The effect of employing vector instructions was investigated in detail using an ISA simulator and measuring the reduction in terms of number of instructions. In the case of matrix-multiplications between 128×128 matrices, vector processors are shown to provide a potential speedup up to 89×.

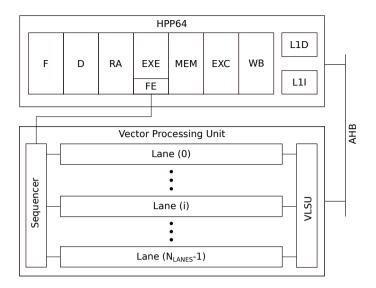

Finally, vector instructions were implemented in Very High Speed Integrated Circuit Hardware Description Language (VHDL) on a baseline NOEL-V processor from Cobham Gaisler and the obtained vector processor was employed to generate a hardware prototype on a Field Programmable Gate Array (FPGA) achieving Technology Readiness Level (TRL) 4. Furthermore, a detailed benchmarking with specific kernels including kernels from CloudNet was carried out, to show the benefits of implementing vector instructions. Several configurations were considered with high- and low-latency main memory, based respectively on a Synchronous Dynamic Random-Access Memory (SDRAM) and Synchronous Random-Access Memory (SRAM) memory. The presented prototype is capable of executing a DNN for cloud detection roughly 20× faster than the baseline processor.

# SAMENVATTING

Het gebruik van terrestrische processors in ruimtetoepassingen is niet eenvoudig, aangezien processors in de ruimte voor unieke uitdagingen staan vanwege de effecten van de ruimteomgeving, zoals ioniserende straling die Single Event Effects (SEE's) veroorzaakt. In de jaren negentig koos de European Space Agency voor de Scalable Processor ARChitecture (SPARC) Instruction Set Architectures (ISA) voor zijn processors, omdat dit de enige beschikbare oplossing was op dat moment die zowel openheid als diffuse softwareondersteuning in terrestrische toepassingen bood. Momenteel gebruikt een groot deel van de wereldwijde ruimtevaartgemeenschap SPARC-gebaseerde radiation-hardened (rad-hard) of radiation-tolerant (rad-tol) LEON-processors in alle lopende en geplande missies, hoewel SPARC-processors vrijwel verdwenen zijn uit terrestrische toepassingen. Rad-hard- en rad-tol-processors voor ruimtevaarttoepassingen lopen doorgaans meer dan tien jaar achter op hun commerciële tegenhangers in termen van prestaties en de kloof wordt elk jaar groter. Dit komt vooral door het gebruik van Rad-Hard-By-Design (RHBD)-cellen en grotere technology nodes. De grotere kwetsbaarheid voor SEE's van complexe microarchitecturen is niet de enige reden waarom eenvoudige microarchitecturen met een laag parallellisme nog steeds de overgrote meerderheid zijn van processors die in de ruimte worden gebruikt. In feite zijn de meeste taken die worden uitgevoerd door processors in ruimtegegevenssystemen niet-rekenintensieve werkbelastingen. De reden is dat ze voornamelijk worden ingezet voor niet-veeleisende controle- en housekeeping werkzaamheden. Om de uitvoering van Artificial Intelligence (AI)-algoritmen in space embedded systems mogelijk te maken, is daarom een grote sprong voorwaarts nodig in space-grade processors, vooral omdat ruimtegegevenssystemen in satellieten doorgaans power-constrained zijn.

Onlangs is RISC-V, een nieuwe free en open ISA, steeds populairder geworden in terrestrische toepassingen en heeft het de aandacht getrokken van verschillende universiteiten en bedrijven. Gezien de overeenkomst tussen SPARC en RISC-V, begint dit proefschrift met het analyseren van de voordelen van het gebruik van RISC-V in ruimtetoepassingen. De openheid van RISC-V maakte al een enorm veld van onderzoeksactiviteiten voor terrestrische toepassingen mogelijk, met veel tools en modellen op verschillende abstractieniveaus die al beschikbaar zijn. Daarom kan de ruimtevaartindustrie ontwikkelingen uit de academische wereld en de industrie hergebruiken, waarbij de inspanningen voornamelijk worden gericht op verbeteringen met betrekking tot specifieke behoeften op het gebied van ruimtetoepassingen en zonder inspanningen te verspillen aan andere activiteiten. Om de modulariteit volledig te benutten, werd in dit proefschrift de noodzaak geïdentificeerd van het definiëren van de typen processors die nodig zijn voor ruimtetoepassingen. De modulariteit van RISC-V werd gebruikt om verschillende toepassingen in ruimtegegevenssystemen en RISC-V-processorprofielen te identificeren om ze aan te pakken. Ze werden in dit werk gedefinieerd door de ISA-subset, Instruction-Level Parallelism (ILP), Data-Level Parallelism (DLP), Processor-Level Paral*lelism* (PLP), referentie-implementatie en verwachte prestaties. De gedefinieerde processorprofielen variëren van microcontrollers tot implementaties voor algemene doeleinden tot high-performance processors voor AI. Ten slotte werd een routekaart gedefinieerd om RISC-V IP-cores voor terrestrische toepassingen op ruimteniveau te brengen, waarbij de vereiste stappen en modellen werden geïdentificeerd.

Nadat de grondige analyse van de *state of the art* van RISC-V-processors was voltooid, werden twee verschillende sets van activiteiten geïdentificeerd.

- 1. Verhoog de *fault tolerance* van micro-architecturen van ruimteprocessors van de volgende generatie: Om dit te doen werd een literatuurstudie uitgevoerd en werd een model ontwikkeld om de kwetsbaarheid van microarchitecturen voor SEE's te evalueren. Tijdens het maken van dit model bleek dat de meest invloedrijke factoren op de SEE-kwetsbaarheid technologie, omgeving en microarchitectuur zijn. De meest kwetsbare onderdelen die werden geïdentificeerd in zowel de volgende generatie als de modernste processors waren caches, voornamelijk vanwege het grote bezette gebied. Om deze reden vermindert het aanpakken van de storingen in caches het uitvalpercentage voor state-of-the-art en next-generation processors met respectievelijk 96% en 93%. Verschillende redundantietechnieken werden geïntroduceerd en hun effect op micro-architecturen vergelijkbaar met *state-of-the-art* en next-generation ruimteprocessors geëvalueerd met dit model.

- 2. Verhoog de prestaties van de volgende generatie processors: In plaats van te focussen op de optimalisatie van bestaande micro-architecturen, lag de focus hier op het identificeren van nieuwe soorten toepassingen voor ruimteprocessors waarvoor de prestaties drastisch kunnen worden verbeterd door nieuwe microarchitecturen, aangezien state-of-the-art processors niet zijn ontworpen om ze efficiënt uit te voeren. Er is een analyse uitgevoerd van de vereisten van processors om Deep Neural Networks (DNN's) uit te voeren. Vervolgens werd een onderzoek uitgevoerd naar de rekenintensieve workloads die nodig zijn voor het uitvoeren van DNN's, op basis van de case study van CloudNet, een DNN voor clouddetectie. Omdat bleek dat de werklast grotendeels bestaat uit matrixbewerkingen, werd de RISC-V Vector Extension (RVVE) voorgesteld om de uitvoering van deze matrixbewerkingen te versnellen. Het effect van het gebruik van vectorinstructies is in detail onderzocht met behulp van een ISA-simulator en het meten van de vermindering van het aantal instructies. In het geval van matrixvermenigvuldigingen tussen 128×128 matrices, wordt aangetoond dat vectorprocessors een potentiële versnelling tot 89 keer bieden.

Ten slotte werden vectorinstructies geïmplementeerd in *Very High Speed Integrated Circuit Hardware Description Language* (VHDL) op een baseline NOEL-V-processor van Cobham Gaisler en de verkregen vectorprocessor die werd gebruikt om een hardwareprototype op *Field Programmable Gate Array* (FPGA) te genereren dat *Technology Readiness Level* (TRL) 4 bereikte. Verder is er een gedetailleerde benchmarking uitgevoerd met specifieke kernels, waaronder kernels van CloudNet, om de voordelen van het implementeren van vectorinstructies te laten zien. Er werden verschillende configuraties overwogen met hoofdgeheugen met hoge en lage latentie, respectievelijk gebaseerd op een *Synchronous Dynamic Random-Access Memory* (SDRAM) en *Synchronous Random-Access Memory* (SRAM) geheugen. Het gepresenteerde prototype kan een DNN voor clouddetectie ongeveer 20x sneller uitvoeren dan de baseline processor.

# **LIST OF ABBREVIATIONS**

| AC   | Average Criticality                       |

|------|-------------------------------------------|

| ACE  | Architecturally Correct Execution         |

| ADR  | Active Debris Removal                     |

| AHB  | AMBA High-performance Bus                 |

| AI   | Artificial Intelligence                   |

| ALU  | Arithmetic-Logic Unit                     |

| AMBA | Advanced Microcontroller Bus Architecture |

| AOCS | Attitude and Orbital Control System       |

| ASIC | Application-Specific Integrated Circuit   |

| AVF  | Architectural Vulnerability Factor        |

| AXI4 | Advanced eXtensible Interface 4           |

| BHT  | Branch History Table                      |

| BLAS | Basic Linear Algebra Subroutines          |

| BP   | Branch Prediction                         |

| BTB  | Branch Table Buffer                       |

| CC   | Clock Cycle                               |

| CI   | Cell Interleaving                         |

| CL   | Criticality Level                         |

| CMOS | Complementary Metal–Oxide Semiconductor   |

| CNN  | Convolutional Neural Network              |

| COTS | Commercial-Off-The-Shelf                  |

| CPI  | Cycles Per Instruction                    |

| CSR  | Control and Status Registers              |

| CU   | Constant Utilization                      |

| CVF  | Cache Vulnerability Factor                |

| CW   | Constant Workload                         |

| DC   | Data Cache                                |

| DDR2 | Double Data Rate 2                        |

| DDR3 | Double Data Rate 3                        |

| DDR4 | Double Data Rate 4                        |

| DL   | Deep Learning                             |

| DLP  | Depending on the context:                 |

|      | Data-Level Parallelism                    |

|      | Data-Level Parallel                       |

| DMR  | Double Modular Redundancy                 |

| DNN  | Deep Neural Network                       |

| DP   | Double Precision                          |

| DRAM | Dynamic Random-Access Memory              |

|      |                                           |

| cviii |               |

|-------|---------------|

|       |               |

| DSP   | Digital Signa |

| DUE   | Detected Ur   |

| חפת    | Digital Signal Processing                                      |

|--------|----------------------------------------------------------------|

| DSP    | Digital Signal Processing<br>Detected Uncorrectable Error      |

| DUE    |                                                                |

| ECC    | Error Correcting Code                                          |

| EDAC   | Error Detection And Correction                                 |

| EDC    | Error Detecting Code                                           |

| EXC    | Exception stage                                                |

| EXE    | Execution stage                                                |

| F      | Fetch stage                                                    |

| FC     | Fully Connected                                                |

| FD-SOI | Fully-Depleted Silicon-On-Insulator                            |

| FE     | Front End                                                      |

| FF     | Flip-Flop                                                      |

| FFT    | Fast Fourier Transform                                         |

| FI     | Fault Injection                                                |

| FinFET | Fin Field-Effect Transistor                                    |

| FMA    | Refers to both (specified when referring to just one of them): |

|        | Fused Multiply-Accumulate                                      |

|        | Fused Multiply-Add                                             |

| FPGA   | Field Programmable Gate Array                                  |

| FPU    | Floating Point Unit                                            |

| FRF    | Floating Register File                                         |

| FT     | Fault-Tolerant                                                 |

| GCR    | Galactic Cosmic Rays                                           |

| GE     | Gate Equivalents                                               |

| GEMM   | GEneral Matrix Multiply                                        |

| GEO    | Geostationary Orbit                                            |

| GP     | General Purpose                                                |

| GPR    | General-Purpose Register                                       |

| GPU    | Graphics Processing Unit                                       |

| GRU    | Gated Recurrent Unit                                           |

| HC     | High Criticality                                               |

| HDL    | Hardware Description Language                                  |

| HP     | Half Precision                                                 |

| HPC    | High-Performance Computing                                     |

| I/O    | Input/Output                                                   |

| IB     | Instruction Buffer                                             |

| IC     | Instruction Cache                                              |

| ID     | Interleaving Distance                                          |

| IF     | Instruction Fetch                                              |

| IFT    | Inverse Fourier Transform                                      |

| II     | Instruction Issue                                              |

| ILP    | Instruction-Level Parallelism                                  |

| IO     | In-Order                                                       |

| IOD    | In-Orbit Demonstration                                         |

| IoT    | Internet of Things                                             |

|        |                                                                |

| IP       | Intellectual Property              |

|----------|------------------------------------|

| IPC      | Instructions Per (clock) Cycle     |

| IPS      | Instructions Per Second            |

| IRF      | Integer Register File              |

| ISA      | Instruction Set Architecture       |

|          | Instruction Set Simulator          |

| ISS      |                                    |

| IU       | Integer Unit                       |

| L1       | Level1                             |

| L2C      | Level2 Cache                       |

| LC       | Low Criticality                    |

| LEO      | Low Earth Orbit                    |

| LET      | Linear Energy Transfer             |

| LLC      | Last-Level Cache                   |

| LSB      | Least Significant Bit              |

| LSTM     | Long Short-Term Memory             |

| LSU      | Load and Store Unit                |

| M/D      | Multiplier and Divider             |

| MAC      | Multiply-Accumulate                |

| MBU      | Multiple Bit Upset                 |

| MC       | ManyCore                           |

| MCon     | Memory Controller                  |

| MCU      | Multiple Cell Upset                |

| MD       | MBU Dominated                      |

| MEM      | Memory stage                       |

| MESI     | Modified Exclusive Shared Invalid  |

| MIMD     | Multiple Instruction Multiple Data |

| ML       | Machine Learning                   |

| MLP      | Memory Level Parallelism           |

| MM       | Mass Memory                        |

| MMU      | Memory Management Unit             |

| MPEG     | Moving Picture Experts Group       |

| MSB      | Most Significant Bit               |

| MTTE     | Mean Time To Event                 |

| MTTF     | Mean Time To Failure               |

| NLP      | Natural Language Processing        |

| OBC      | On-Board Computer                  |

| OBDM     | On-Board Decision Making           |

| OI       | Operational Intensity              |

| 000      | Out-of-Order                       |

| OS       | Operating System                   |

| QoS      | Quality of Service                 |

| RA       | Register Access stage              |

| Rad-hard | Radiation-hardened                 |

| Rad-tol  | Radiation-tolerant                 |

| RF       | (scalar) Register File             |

|          |                                    |

| RHBD   | Rad-Hard-By-Design                                 |

|--------|----------------------------------------------------|

| RNN    | Recurrent Neural Network                           |

| ROB    | ReOrder Buffer                                     |

| RQ     | Research Question                                  |

| RR     | Register Rename                                    |

| RS     | Reed-Solomon                                       |

| RTL    | Register Transfer Level                            |

| RTOS   | Real-Time Operating System                         |

| RTU    | Remote Terminal Unit                               |

| RVVE   | RISC-V Vector Extension                            |

| SAA    | South Atlantic Anomaly                             |

| SBF    | Single Bit Flip                                    |

| SBU    | Single Bit Upset                                   |

| SD     | SET Dominated                                      |

| SDR    | Single Data Rate                                   |

| SDR    | Synchronous Dynamic Random-Access Memory           |

| SECDED | Single Error Correction and Double Error Detection |

|        |                                                    |

| SED    | Single Error Detection                             |

| SEE    | Single Event Effect                                |

| SEFI   | Single Event Functional Interrupt                  |

| SEL    | Single Event Latchup                               |

| SER    | Soft Error Rate                                    |

| SET    | Single Event Transient                             |

| SEU    | Single Event Upset                                 |

| SIMD   | Single Instruction Multiple Data                   |

| SMP    | Symmetric MultiProcessing                          |

| SNR    | Signal-to-Noise Ratio                              |

| SoC    | System-on-Chip                                     |

| SOI    | Silicon-On-Insulator                               |

| SP     | Single Precision                                   |

| SPARC  | Scalable Processor ARChitecture                    |

| SpW    | SpaceWire                                          |

| SRAM   | Static Random-Access Memory                        |

| SSO    | Sun-Synchronous Orbit                              |

| SVE    | Scalable Vector Extension                          |

| T&C    | Telemetry and Command                              |

| TCP/IP | Transmission Control Protocol/Internet Protocol    |

| TID    | Total Ionizing Dose                                |

| TLB    | Translation Lookaside Buffer                       |

| TLP    | Thread-Level Parallelism                           |

| TMR    | Triple Modular Redundancy                          |

| TRL    | Technology Readiness Level                         |

| UT     | Unexpected Termination                             |

| VBN    | Vision-Based Navigation                            |

| VC     | Vector Cache                                       |

- VHDL Very High Speed Integrated Circuit Hardware Description Language

- VLA Vector-Length Agnostic

- VLSU Vector Load and Store Unit

- VP Vector Processor

- VRF Vector Register File

- WB Write-Back

- WCET Worst Case Execution Time

- WT Write-Through

# 1

# **INTRODUCTION**

Blott Sverige svenska krusbär har. Only Sweden has Swedish gooseberries.

Carl Jonas Love Almqvist, "Om svenska rim" (1838)

State-of-the-art space-grade processors lag behind their commercial counterparts because of their niched-size market (meaning smaller design teams and investments), their need for specific design solutions (e.g. tolerance against radiation effects), long qualification times and the importance of flight heritage in space applications. As a result, state-of-theart space-grade processors are based on outdated Instruction Set Architectures (ISAs) and simple microarchitectures. The recent availability of RISC-V, a free, open and modular ISA, ignited the development of an unprecedented amount of open-source implementations targeting terrestrial applications. Future space systems could benefit from many of these developments, provided that work is done to satisfy the specific needs of processors for space (spin-in), especially in terms of fault tolerance and Technology Readiness Level (TRL).

Parts of this chapter have been published in [1] and in [2].

# **1.1.** BACKGROUND

Artificial Intelligence (AI) has been identified in the last decades as one of the most promising enabling technologies of future space applications [3, 4]. Deploying AI on board satellites enables intelligent On-Board Decision Making (OBDM), which for instance can help to overcome typical bottlenecks of space systems like the downlink bandwidth. Link bandwidth is a problem especially for severely resource-limited spacecraft like small satellites (e.g. it can take hours to days to downlink an image to the ground) [5]. The capability of filtering out images that do not meet certain criteria (data reduction) can greatly increase the potential of CubeSats, a highly miniaturized standard based on a satellite form factor of  $10 \times 10 \times 10 \ cm^3$ , as improvements in sensors generate increasingly larger data volumes and storage space on CubeSats is typically very limited [5]. Furthermore, many proposed future missions are supposed to produce enormous volumes of data. In order to enable them, [6] suggests that either significant communication advancements or data reduction techniques are needed. However, advances in both capabilities would provide systems designers with a larger design space where better trade-offs are possible for missions producing large volumes of data. OBDM can enable also swarms [7], Active Debris Removal (ADR) by Vision-Based Navigation (VBN) [8] and in the future even cost-effective asteroid mining [9]. Furthermore, the capabilities of future scientific missions can be improved by OBDM too. For instance, the introduction of increasing degrees of OBDM capabilities to enable autonomous navigation and autonomous interpretation of data in the Mars rovers decreased the need of sending data to be processed and interpreted on Earth. Thus, the rovers were able to explore more on the surface of the planet instead of waiting for commands, overcoming also latency of operations commanded from ground [10].

Decisions can be made according to several degrees of "intelligence". In a first phase, systems were "smart" because they were provided with fixed rules defined by experts that worked for a specific application within certain expected boundary conditions. This approach is typically referred to as Digital Signal Processing (DSP). As an example, [8] describes several "tailored" algorithms for VBN. Today terrestrial applications are in a new phase where systems employ statistical learning to adapt their behavior to unexpected changes. This approach is typically referred to as Machine Learning (ML). More specifically, Deep Neural Networks (DNNs) are booming in terrestrial applications, generating a sub-field of AI known as Deep Learning (DL). This is possible thanks to the availability of large data sets from 'big data' and the availability of Graphics Processing Unit (GPU)-based hardware that enables processing of large amounts data in a reasonable timescale [11]. However, the situation in space embedded systems is quite different, as will be explained next.

The usage of terrestrial processors in space applications is not straightforward, as processors in space face unique challenges due to the effects of the space environment, like ionizing radiation causing Single Event Effects (SEEs)<sup>1</sup> and Total Ionizing Dose (TID) effects<sup>2</sup>. Radiation-hardened (rad-hard) processors for space applications typically lag more than a decade behind their commercial counterparts in terms of performance and the gap is widening every year (e.g. the commercial PowerPC-750 roadmap showed a

<sup>&</sup>lt;sup>1</sup>SEEs are events caused by one highly energetic particle [12].

<sup>&</sup>lt;sup>2</sup>TID effects are effects due to the accumulation of absorbed ionizing dose [13]

performance improvement of ~ 2400× from the early 1990s to 2005 [14], whereas the radhard version was improved by only ~  $300 \times [8]$ ). This was mainly due to lower frequencies and smaller caches, both due to older technology nodes (e.g. in [8] commercial processors were based on 28 nm technologies, while contemporary rad-hard processors on 65 nm technologies) and use of Rad-Hard-By-Design (RHBD) cells. Furthermore, processors used in space are typically slower than their terrestrial counterparts due to the long qualification process for space-grade components and to a risk-averse behavior of space industry that prefers components and technologies which already are flight-proven. As a result, state-of-the-art space-grade processors are typically one or two order of magnitude less performing than their Commercial-Off-The-Shelf (COTS) counterparts [8]. Therefore, enabling OBDM in space embedded systems requires a large leap in spacegrade processors to deal with algorithmic complexity, especially because satellites are typically power-constrained [8]. The analysis of state-of-the-art space-grade processors carried out with a literature review in Sec. 1.4 is the body of knowledge that will be improved in this dissertation. Before this analysis of terrestrial processors, Sec. 1.2 intro-

duces concepts required in order to analyze the microarchitecture of processors in terms of performance and Sec. 1.3 introduces concepts to analyze the fault tolerance of space-grade processors.

# **1.2.** CONCEPTS OF COMPUTER ARCHITECTURE

Comparisons of different processors are typically based on metrics involving performance. In order to understand the reasons behind differences in performance, in this section a simple model describing the performance of processors for a certain software program is presented. The time required to execute a program,  $T_{ex}$ , is given by:

$$T_{ex} = \frac{NI}{f_{clk}} \cdot CPI, \tag{1.1}$$

where *NI* is the number of instructions in the program,  $f_{clk}$  the clock frequency, and *CPI* is the average number of Cycles Per Instruction [15]. Sometimes performance is expressed in terms of Instructions Per Second (IPS), where  $IPS = f_{clk}/CPI$ , although this metric is incomplete as it does not take into account that different Instruction Set Architectures (ISAs) require different *NI* to execute the same program. Sometimes performance is expressed instead in terms of Instructions Per (clock) Cycle (IPC), where IPC = 1/CPI, which has the same limitation as IPS, and it does not take into account the improvement in terms of performance due to an higher  $f_{clk}$ .

The rest of this section shows how this execution time can be reduced for a given processor, employing parallelism, speculation and caching. The elements introduced in this section will allow a comparison of state-of-the-art processors for space applications with state-of-the-art general-purpose processors for terrestrial applications in Sec. 1.4.

## **1.2.1.** PARALLELISM

The execution time can be reduced by exploiting parallelism in several ways. In this case, the focus is typically on decreasing the average number of *CPI*, although increasing  $f_{clk}$  or decreasing *NI* is possible too.

1

#### **INSTRUCTION-LEVEL PARALLELISM**

One of the main tools to speedup the performance of a processor is to increase its level of Instruction-Level Parallelism (ILP), i.e. the number of instructions executed simultaneously. There are two main approaches:

• Pipelined execution: multiple instructions are overlapped in time, each of them in a different pipeline stage. Beside gains from overlapping execution of different instructions, another advantage of pipelining is the increase of the maximum allowed frequency, as the logic is broken down in shorter paths [16]:

$$f_{clk} = \frac{1}{(T/k) + T_S},$$

(1.2)

where *T* is the propagation time trough the logic before pipelining, *k* the number of pipeline stages and  $T_S$  is the overhead in terms of propagation time introduced by the inserted sequential elements. Assuming that  $T_S << T/k$ , the improvement in frequency is linear with the number of stages. However, the sub-operations of a given instruction are not uniform and instructions are dependent from each other (interinstruction dependency). Non-uniform sub-operations require balancing of the logic in the stages of the pipeline, as the maximum frequency will be determined by the slowest combinational path in the pipeline with a propagation time of  $T_{max}$ , where T/k is replaced by  $T_{max}$  in Eq. 1.2. To efficiently handle inter-instruction dependencies an increase of design complexity is required. On the other hand, a simple solution for inter-instruction dependency is stalling the pipeline until the dependencies are solved, causing large penalties in terms of performance [17] because of an increased CPI compared to an ideal pipeline without inter-instruction dependency. Inter-instruction dependency can be classified in two types:

- Data hazard: one of the instructions in the pipeline needs data from an instruction in later stages of the pipeline but that result isn't already available in the registers. A typical example is a load followed by an operation on the loaded value. In this case the loaded data can be directly forwarded as soon as they are ready from the previous instruction, thus minimizing the stall [15].

- 2. Control (or branch) hazard: when a branch instruction is fetched, it takes some Clock Cycles (CCs) before knowing the target address and whether the branch is taken or not. In this case speculation can increase performance (Sec. 1.2.2).

Another argument against pursuing an increase of performance by increasing  $f_{clk}$  with a very deep pipeline is that an enhancement in a subsystem of the processor provides a limited improvement to the performance of the processor as a whole, as that subsystem is used only a limited amount of time. This is expressed by the Amdahl's Law [15]:

$$Improved Execution Time = \frac{Affected Execution Time}{Improvement} + Unaffected Execution Time.$$

(1.3)

For instance, memories are typically slower than processors. Assuming that reading and writing to the memory takes 60% of the time and improving the clock frequency of the processor by  $10\times$ , the execution time will decrease only by 36% [17].

- Multiple issue: the lower boundary for CPI of a single-issue processor is one. Multipleissue processors deal with multiple instructions per stage, so that CPI can be less than one. There are two approaches for this:

- 1. Static: the compiler analyses the software and packages instructions to execute simultaneously, when possible. This solution requires the pipeline (or at least parts of it) to be replicated. The multiple instructions launched during the same CC can be seen as one large instruction with multiple operations in parallel. For this reason, the processors that employ this approach are called Very Long Instruction Word (VLIW) processors [15].

- 2. Dynamic (superscalar): in this case the processor decides during execution whether zero, one, or more instructions can be issued at a given CC [15]. A processor that can execute up to n instructions is usually called a n-way processor [15].

To utilize more efficiently the ILP of superscalar processors, sometimes dynamic pipeline scheduling is employed, i.e. using Out-of-Order (OoO) pipelines. Dynamic pipeline scheduling chooses which instructions to execute next, reordering them to minimize stalls [15].

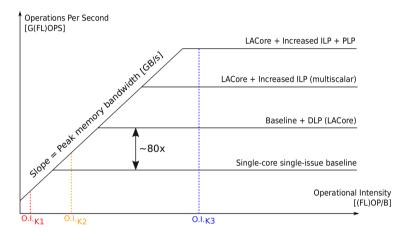

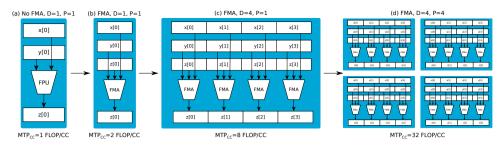

## DATA-LEVEL PARALLELISM

A processor with Data-Level Parallelism (DLP) can execute an instruction on more elements of an array. Therefore, a considerable improvement in terms of performance can be obtained, as Data-Level Parallel (DLP) instructions reduce the number of instructions NI in a program by dealing with larger chunks of data compared to non-DLP instructions. This improvement is larger for programs where many instructions operate on regular data structures, which can be treated as vectors. However, when implementing DLP the challenge is to keep the penalty on *CPI* and  $f_{clk}$  low. Two different approaches can be identified for DLP [18]:

- 1. Packed-Single Instruction Multiple Data (SIMD) DLP: a specific instruction is added to the ISA to exploit DLP provided by the hardware. The width is encoded in the assembly instruction. As a consequence, in order to increase performance and assure backward compatibility, also the number of instructions has to increase.

- 2. Vector DLP: this type of implementation can be seen as a more flexible version of packed-SIMD thanks to its time-multiplexed and Vector-Length Agnostic (VLA) approach. The VLA approach implies that the software is oblivious to the hardware vector length of a specific implementation and the same code executes using the largest parallelism possible on each platform [18–20]. This approach greatly simplifies software, especially because the width of the vectors is flexible and the ISA is independent from the level of parallelism provided by the platform.

As noted in [18], even if SIMD solutions have been successful on the consumer market, they are a suboptimal choice for an ISA. As a matter of fact, SIMD processors are usually

1

implemented replicating the Arithmetic-Logic Unit (ALU) and providing new opcodes<sup>3</sup> to the ISA in order to exploit this parallelism. This makes ISA instructions dependent on the implementation-specific degree of parallelism and new instructions must be added when a new level of DLP is required. When the architects of a packed-SIMD ISA wish to increase performance by widening the vectors, they must add a new set of instructions to process these vectors. For instance, Intel's newest AVX instructions are as long as 11 bytes [18]. Furthermore, application code compiled for previous versions cannot automatically leverage the widened vectors of new implementations. At the same time, code compiled for wider packed-SIMD registers fails to execute on older machines as the new instructions are not known to older implementations. Furthermore, in SIMD extra code is needed to handle fringe elements of strip mine loops [18].

#### THREAD-LEVEL PARALLELISM

Thread-Level Parallelism (TLP), also known as hardware multithreading, allows multiple threads<sup>4</sup> to share the functional units of a single processing core, switching thread when the running one is stalled. In order to do this, the processor must store the independent state of each thread. Hardware multithreading can be implemented in several ways:

- Coarse-grained: one thread runs until it is blocked by an event that creates a long latency stall (e.g. a cache miss). Hardware support for this type of multithreading is meant to allow quick switching between the threads, for instance storing the program visible state (e.g. general purpose registers and program counter) in the processing core [21].

- Fine-grained: the processor checks every cycle if the current thread is stalled or not. If stalled, a hardware scheduler will change execution to another thread that is ready to run [21]. Simpler fine-grained implementations, like the one described in [22], change thread every CC independently if the current one is stalled or not [23].

- Simultaneous: in this case a superscalar processor can issue instructions from either the same thread or from different threads [23]. The hardware thread scheduler has to chose the best instruction in order to maximize the utilization of the resources [21].

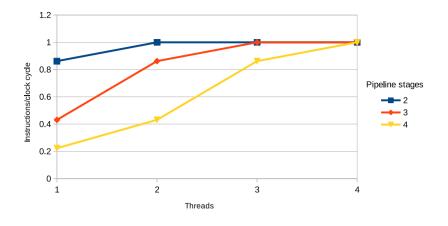

While coarse-grained multithreading is suited to avoid stalls due to a cache miss, finegrained and simultaneous multithreading can effectively circumvent penalties due to control and data hazards [21] and can avoid the need for branch prediction. In [22] several fine-grained processing cores with different numbers of pipeline stages and numbers of hardware (HW) threads are proposed. The data in [22] shows the average number of IPC as a metric for the utilization of the pipeline for several versions of the same finegrained implementation depending on the number of the software threads employed. It shows that even the simplest form of fine-grained implementation achieves full utilization (in this case IPC = 1) of its single-issue pipeline when the number of threads is

<sup>&</sup>lt;sup>3</sup>Abbreviated form of "operational code", i.e. a portion of machine language that specifies an operation to be performed.

<sup>&</sup>lt;sup>4</sup>From a software perspective, a thread of execution is the smallest sequence of programmed instructions that can be managed independently by a scheduler, which is typically a component of the operating system. A thread includes the program counter, the register state, and the stack [15].

greater than or equal to the number of pipeline stages. When the number of threads is smaller than the number of pipeline stages, the pipeline is underutilized.

#### PROCESSOR-LEVEL PARALLELISM (PLP)

In the last decade Moore's Law made it possible to include more processing cores in the same Application-Specific Integrated Circuit (ASIC) [24]. The most common approach to handle this parallelism is to provide a single physical address space that all the cores can share and to employ an Operating System (OS) scheduler to assign a thread to each core. This approach is called Symmetric MultiProcessing (SMP) [25]. Each processor works internally with virtual addresses that need to be translated to physical addresses. Processors communicate through shared variables in memory, with all processors capable of accessing any memory location via loads and stores [15].

General-purpose processors employ a Memory Management Unit (MMU) to translate page-based virtual addresses to physical addresses. The address table necessary for such translation is contained in the main memory and accessing it for each address is not an optimal solution. For this reason, Translation Lookaside Buffers (TLBs) are typically employed to reduce the average time per address translation in a similar manner as caches are employed to decrease the average access time to data and instructions in main memory (see Sec. 1.2.3).

SMP processors typically provide up to eight cores, as they are limited by the sequential model of the software and the use of shared resources (memories and interconnects). The impact of sequential tasks can be described applying Amdahl's Law (Eq. 1.3) to the parallelization problem [26], dividing a general problem in a parallelizable part (p) and a sequential part (s). The time required to execute the algorithm on a single core can be written as  $T_{ex,1} = (s + p)T_{ex,1}$ , where s + p = 1. Assuming that the size of the problem remains constant with the increase of PLP, with n processing cores the execution time becomes  $T_{ex,n} = (s + p/n)T_{ex,1}$ . Therefore, the speedup S due to the use of n cores is:

$$S = \frac{1}{s + p/n}.\tag{1.4}$$

In [26], it can be seen how, for an infinite amount of parallel processors, this leads to the theoretical maximum speedup of 1/s. This means that, under the assumption that the size of the problem remain constant, the speedup of a program using multiple cores in parallel is limited by the time needed for the sequential fraction of the program. In an SMP platform this means that the capability of the OS to parallelize the workload is the final bottleneck. Therefore, increasing the number of processors provides only marginal improvements from a certain number of processors onward, independently from how efficiently resource sharing problems (e.g. access to shared memories) are solved.

Gustafson in [26] objected the assumption that the size of the problem remains constant when PLP is increased. Instead, he assumed that it is the run-time that remains constant, thus increasing the amount of calculations included in the problem (assuming that the workload can scale with the number of processors). Assuming that the serial part remains constant and that the parallel part can be parallelized over the *n* processing cores, then  $T_{ex,n}^n = (s' + p')T_{ex,n}^n$  for a parallel system (also here s' + p' = 1). The time required by a single processor executing the workload scaled by *n* is  $T_{ex,1}^n = (s' + p'n)T_{ex,n}^n$ . 1

In this case the execution time of the sequential part of the software becomes more and more negligible when the number of processors is increased, giving a linear increase with the number of processing cores, as shown below:

$$S = s' + p' n.$$

(1.5)

Following this paradigm, several manycore<sup>5</sup> processors, providing higher degrees of PLP, have been released (for instance with 64 cores [27]). These processors typically employ replicas of simple processors, and to parallelize the workload, each of them executes the same instruction on different data. This paradigm is often referred to as Multiple Instruction Multiple Data (MIMD) [18].

#### **1.2.2.** Speculation

Another way to decrease CPI is to use speculative execution (speculation). Speculation consists in predicting the outcome of an operation and start working assuming that the guess is right. As soon as the actual result is available, it must be checked if the prediction was right. If that was not the case, then the effect of the instructions that were executed speculatively must be reversed. For this reason, the implementation of speculation adds complexity [15]. Speculation is typically employed when a conditional branch instruction creates a control hazard in a deep and wide pipeline. For instance, in ARM Cortex-A8 (a dual-issue 14 stages processor where the branch address is calculated at the 13th stage, hence *number of issues* = 2 and *stalling penalty* = 13 CCs) if the pipeline is stalled while waiting for the branch address, then the number of potentially wasted cycles are: *number of issues* × *stalling penalty* (that in this case gives 26 wasted CCs per branch). Considering a branch predictor which predicts correctly 80% of the times in average, only an average 5.2 CCs per branch are wasted.

Data from [28] show that control instructions have low impact on parallel implementations of algorithms (e.g. making up only around 2% of the executed instructions), while they have a considerable impact on sequential algorithms (e.g. making up from 16% to 25% of the executed instructions). Branch prediction is typically transparent to software (except for variable execution times, so it can be a problem for time-determinism), as typically it is fully addressed at hardware level. Two approaches are possible:

- Static branch prediction: the outcome of the branch is predicted before program execution. This approach is based on prediction heuristics from typical software [29] and achieves low efficiency, as it does not take into account the result of such predictions to improve them during software execution. The most popular example is the *always-taken* predictor. This technique can help with prediction of conditional branches in loops, which are more likely to be taken than not (usually more than one loop iteration is executed).

- 2. Dynamic branch prediction: these predictors achieve higher efficiency by learning on past behavior and exploiting temporal and/or spatial correlation. The typical

<sup>&</sup>lt;sup>5</sup>Eight cores can be considered as the boundary between multicore and manycore (typically still considered multicore).

solution is a Branch History Table (BHT), a small memory indexed by the lower portion of the address of the branch instruction. The memory contains a bit that indicates whether the branch was recently taken or not [15].

Branch prediction speculates on whether a conditional branch is taken or not, but cannot speculate on the address of the target. For this reason, other forms of prediction can be employed to avoid stallings due to the calculation of the target address. The two most popular approaches, often used simultaneously, are:

- 1. Branch Table Buffer (BTB): a memory indexed with the lowest bits of the address of a branch instruction and holding the destination instruction address of the last time a branch instruction with the same lowest bits of the address was resolved. BTBs work well in most cases but perform poorly at returns from functions, because a function can be called from several positions within a program [15].

- 2. Subroutine return stack: an effective way of predicting the branch target when returning from a subroutine is to push in a stack the call address when a function call is executed and pop the return address when the return instruction is decoded [15].

## **1.2.3.** MEMORY SUBSYSTEM

A corollary of Amdahl's law (Eq. 1.3) is the feasibility of improving performance by making the most common cases faster (i.e. a large part of the execution time will be affected by the improvement). The most striking example of this approach are cache memories. Caches store recently accessed data (temporal locality) and other contiguous memory locations (spatial locality), to reduce as much as possible the time spent accessing the main memory [15]. A block of data read from main memory is placed in a certain contiguous set of locations of the cache according to its associativity. The most common case is that of set-associative caches, i.e. there are a fixed number of locations where each block can be placed [15]. A set-associative cache with n possible locations for a block is called an n-way set-associative cache [15]. Increasing the number of ways decreases the probability of a block to be evicted, hence reducing cache misses, but on the other hand complicates the design, as more sets have to be inspected to check whether the data is present in the cache.

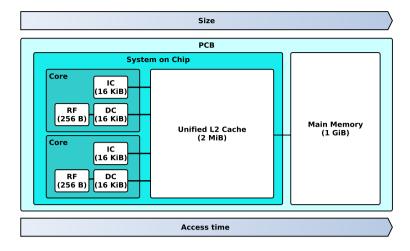

Memories in processors are organized in hierarchies, as shown in Fig. 1.1. A typical memory hierarchy has Register Files (RFs) in the core, the fastest and smallest memories. At the interface between the core and the interconnect, there are Level 1 (L1) caches, divided in Instruction Caches (ICs) and Data Caches (DCs). L1 caches are considerably larger than RFs and typically require a couple of CCs to access them. Between the cores and the main memory, even larger and slower levels of cache (typically shared between the cores and other masters) are placed to achieve the desired access time/miss penalty trade-off. It should be noted that caches and layered memory architectures increase performance for the average case, while access times for the worst case get longer and time-determinism is penalized. In fact, when a cache does not contain the data, it has to fetch it from higher levels, recursively up to the main memory.

Figure 1.1: Typical memory hierarchy and memory sizes for a dual-core general-purpose processor. A similar memory hierarchy can be found in the GR740 processor [30].

## CACHE COHERENCE

The increasing number of processing cores and the limited increase in memory bandwidth makes the memory bandwidth the bottleneck of a multicore system [31]. In a shared-memory multicore processor, data can be stored in several locations simultaneously, e.g. one copy might be residing in the main memory while other copies reside in several cache memories. When one copy of the data is modified by a processing core<sup>6</sup>, then the copies in other caches have to be updated or invalidated. When a processing core writes data to its local cache, two different strategies can be employed [32]:

- 1. Write-back: the main memory is written back only when the cache line is flushed [32]. This can result in discrepancies when the same data is updated in a different way by two different processors. This strategy result in less use of bandwidth but requires more advanced cache coherence protocols.

- 2. Write-through: when data is written in a local cache it is also written in the main memory [32]. This simplifies the coherence issue, although a cache coherence protocol is still needed to invalidate (write-invalidate) or update (write-update) other private caches.

# **1.2.4.** MEASURING PERFORMANCE

In principle, the software employed to select the best processor for a certain application should be a representative portion of the flight software. To have less-specific comparisons (and available before coding the flight software) between processors, they are typically compared using benchmarks, i.e. software intended to emulate the workload for a given type of application. The choice of the benchmark is critical, as it can unfairly favor

<sup>&</sup>lt;sup>6</sup>Although the focus in this work is on processors, in general this applies also to other type of masters (e.g. interface controllers).

one implementation over the other. The most common benchmark for embedded processors is CoreMark [33], while for processors targeting personal computers the SPEC suite is more popular [34].

Historically, performance of embedded processors were assessed measuring the time required to execute part of a "synthetic" program called Dhrystone [35]. In this case performance are typically expressed in "Dhrystone MIPS" (DMIPS)<sup>7</sup>, i.e. how many times the execution is faster compared to a reference processor (VAX 11/780) [36]. However, this program is so short that can fit in the L1 caches of many state-of-the-art processors, thus exercising only a small portion of the core infrastructure (i.e. integer unit). Furthermore, large portions of Dhrystone can be optimized by the compiler and library calls are made within the timed portion of Dhrystone. Since the library code is not part of the benchmark, it is difficult to compare results because different libraries can be used on different implementations. Using CoreMark instead of Dhrystone addresses these issues. For instance, CoreMark ensures that the compilers can not precompute the results, as every operation is based on a value that is not available at compile time. Furthermore, no library calls are made within the timed part.

The timed portion of CoreMark can be divided in three parts [33]:

- 1. Operations (e.g. reverse, search or sort) on linked lists<sup>8</sup>, based on the values of the data items in the list. Including this type of workload measures how fast the processor deals with pointers and non-serial memory access patterns.

- 2. Operations on an input matrix (e.g multiplication with a constant, a vector, or another matrix). Furthermore, also operations on subsets of bits from each matrix item are carried out. Matrix operations can be efficiently sped up by DLP (even if they are relatively small, i.e.  $12 \times 12$  [38]) and are based on (nested) loops.

- 3. Operations on strings (array of characters), with the goal of testing an input string to detect whether it is a number or not. Including this type of workload measures the performance of the processors when dealing with *irregular* conditional branches (i.e. different from loops).

Furthermore, the correctness of most operations is checked with a 16-bit Cyclic Redundancy Check (CRC). CRC is also included in the time measurement, as it is a common operation in software [33].

The score obtained after running CoreMark (usually for a large number of iterations) is the number of times CoreMark is executed per second. Often the CoreMark score is normalized to MHz (CoreMark/MHz), removing the dependence on clock frequency (hence on technology). However, measuring the performance in terms of CoreMark/MHz tends to penalize improvements due to the increase of the number of pipeline stages, because they increase performance mainly by increasing the maximum clock frequency (while they can even penalize the processor in terms of IPC).

<sup>&</sup>lt;sup>7</sup>Although the name can cause misunderstandings, DMIPS is a relative measure of  $T_{ex}$  and it is not the number of MIPS measured when executing Dhrystone.

<sup>&</sup>lt;sup>8</sup>Linked lists are dynamic data structures. Each element of the linked list contains an element to the next element plus data. These type of constructs are used when the number of elements to be represented are not known at compile time [37].

# **1.3.** DEPENDABILITY OF PROCESSORS FOR SPACE APPLICATIONS

Processors for critical applications are required to satisfy certain requirement in terms of dependability, i.e. "the ability to deliver service that can justifiably be trusted" [39]. Although in principle this definition also includes the effects of malicious threats (integrity, confidentiality), in space the focus is still on the effects of non-malicious faults, mainly due to radiation. However, regardless of the specific threats due to the space environment, processors in space have to be first of all robust against faults common to processors in terrestrial applications. For instance, simulations for a 32-nm ASIC technology show that the data propagation delay of Flip-Flops (FFs) increases less than 5% in 5 years of stress conditions due to aging [40]. This can be taken into account during design by applying larger margins on the maximum allowed frequency.

## **1.3.1.** FAULTS DUE TO RADIATION

Changes in the charge stored in nodes due to particle strikes are typical faults in space processors, and they are called soft errors as they can be removed simply overwriting them with the correct value [41]. This is not the case for hard errors [42], where the distinction between fault (e.g. defective gate) and error (e.g. wrong result of a calculation) is needed for correct recovery (e.g. to replace a defective unit with a spare unit).

Despite the possibility of hard errors, soft errors due to radiation typically dominate the failure rate of processors already in terrestrial environments. In [43] the ratio of soft errors to hard errors for Static Random-Access Memory (SRAM) arrays in processors ranges from 77 to 735, and in [44] 99.36% of the errors in a SRAM array are soft errors while 0.64% are hard errors. Soft errors in space are even more predominant, as in this case charged particle strikes are more common (outside the Earth atmosphere the flux of particles is higher) and different particles are present (heavy ions and protons instead of neutrons) [45].

Furthermore, the focus in this dissertation is on faults capable of generating functional errors while faults which generate electrical failures like Single Event Latchups [46] and increase of absorbed current due to TID effects [13] will not be investigated in detail. The reason is that those are typically not addressed at microarchitectural level but at technology and electrical level instead.

#### SINGLE EVENT UPSETS (SEUS)

A Single Event Upset (SEU) can lead to a single or multiple upset. In the first case, the term Single Bit Upset (SBU) is employed. In the second case, the term Multiple Bit Upset (MBU) can be used<sup>9</sup>. The upset rate  $\lambda_{ev}$  mainly depends on the radiation environment (including also shielding), the technology<sup>10</sup> and the choice of the sequential and combinational elements in the processor within the same technology. The upset rate can be either estimated with environmental models or measured on the field [48]. In the first

<sup>&</sup>lt;sup>9</sup>Sometimes the term Multiple Cell Upset (MCU) is employed instead, while MBU is reserved to cases where the multiple upsets are in the same Error Detection And Correction (EDAC)-protected word.

<sup>&</sup>lt;sup>10</sup>Several factors can be included in the technology. For instance, the error rate per bit on a specific technology depends on the voltage chosen (in [47] decreasing the voltage from 1.2 V to 0.8 V results in an increase of the error rate by a factor 1.5x up to 3x, depending on the radiation source). However, as shown in [47], this does not change the ratio between errors from combinational and sequential logic.

case, a standard approach is to carry out a radiation test composed of several test runs with particles with different Linear Energy Transfer (LET)<sup>11</sup> and measure the respective cross section<sup>12</sup>. Afterwards, tools like SPENVIS [50] are used to calculate the differential LET spectrum which can be obtained from the particle differential energy spectra in a certain orbit [49]. The upset rate can be then found with the following integral [49]:

$$\lambda_{ev} = \int_0^\infty \int_{-1}^1 \int_0^{2\pi} f(L,\theta,\phi) \,\sigma(L,\theta,\phi) \,d\phi \,d\cos(\theta) \,dL \tag{1.6}$$

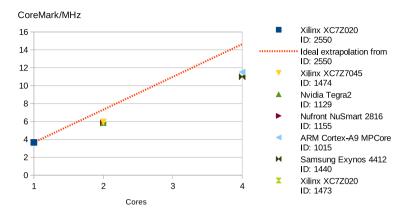

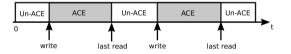

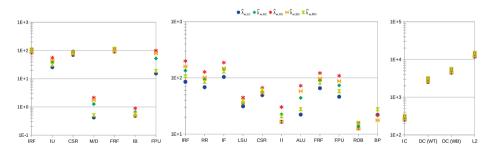

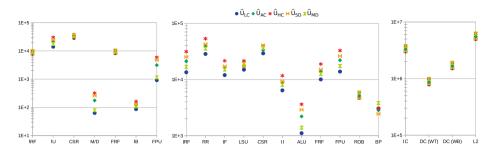

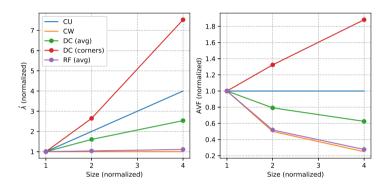

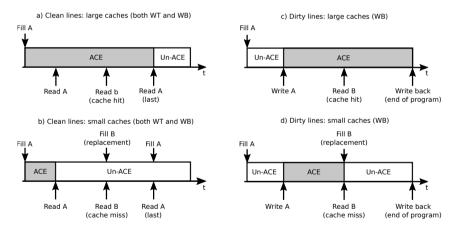

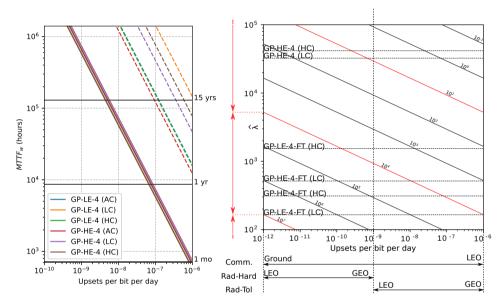

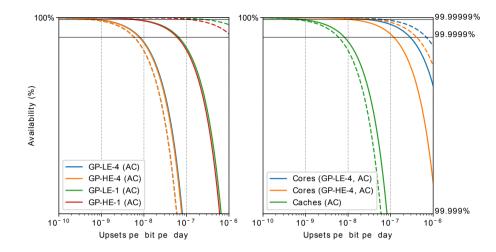

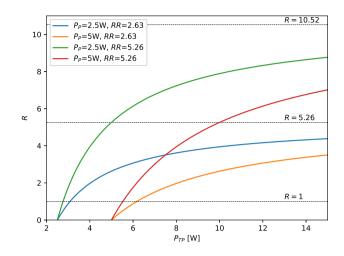

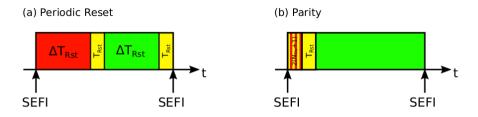

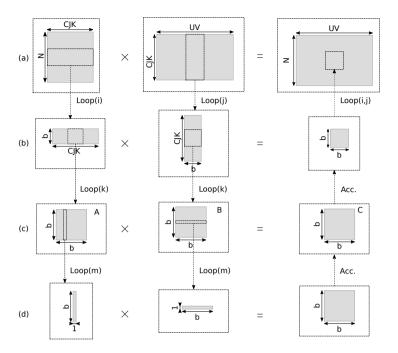

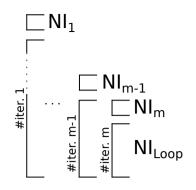

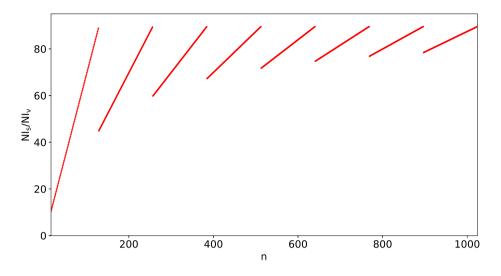

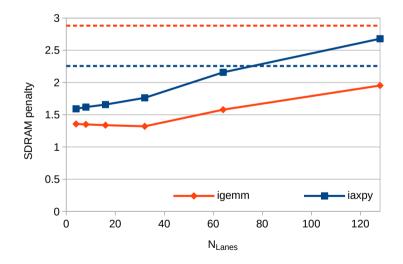

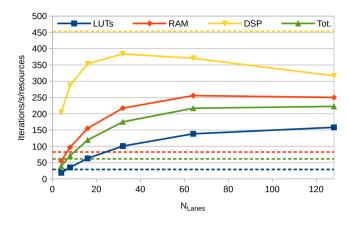

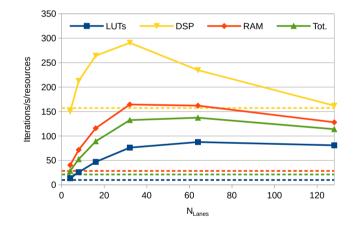

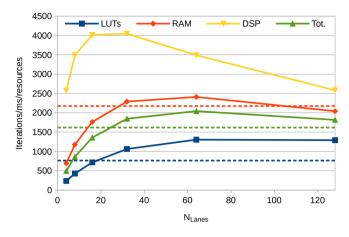

where the differential flux *f* and the cross section per bit  $\sigma$  depend on the LET *L* and the incidence and rotation angles ( $\theta$  and  $\phi$ ) [49].