### MFA-MTJ Model

## Magnetic-Field-Aware Compact Model of pMTJ for Robust STT-MRAM Design

Wu, Lizhou; Rao, Siddharth; Taouil, Mottagiallah; Marinissen, Erik Jan; Kar, Gouri Sankar; Hamdioui, Said

10.1109/TCAD.2021.3140157

**Publication date**

**Document Version** Final published version

Published in

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

Citation (APA)

Wu, L., Rao, S., Taouil, M., Marinissen, E. J., Kar, G. S., & Hamdioui, S. (2022). MFA-MTJ Model:

Opposit Model of pMTJ for Robust STT-MRAM Design. *IEEE Transactions* Magnetic-Field-Aware Compact Model of pMTJ for Robust STT-MRAM Design. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 41(11), 4991-5004. https://doi.org/10.1109/TCAD.2021.3140157

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# MFA-MTJ Model: Magnetic-Field-Aware Compact Model of pMTJ for Robust STT-MRAM Design

Lizhou Wu<sup>®</sup>, *Member, IEEE*, Siddharth Rao, Mottaqiallah Taouil<sup>®</sup>, *Member, IEEE*, Erik Jan Marinissen<sup>®</sup>, *Fellow, IEEE*, Gouri Sankar Kar, and Said Hamdioui<sup>®</sup>, *Senior Member, IEEE*

Abstract—The popularity of perpendicular magnetic tunnel junction (pMTJ)-based spin-transfer torque magnetic random access memories (STT-MRAMs) is growing very fast. The performance of such memories is very sensitive to magnetic fields, including both internal and external ones. This article presents a magnetic-field-aware compact model of pMTJ, named the MFAmagnetic tunnel junction (MTJ) model, for magnetic/electrical co-simulation of MTJ/CMOS circuits. Magnetic measurement data of MTJ devices, with diameters ranging from 35 to 175 nm, are used to calibrate an in-house magnetic coupling model. This model is subsequently integrated into our developed compact pMTJ model, which is implemented in Verilog-A. The superiority of the proposed MFA-MTJ model for device/circuit co-design of STT-MRAM is demonstrated by simulating a single pMTJ as well as STT-MRAM full circuits. The design space is explored under PVT variations and various configurations of magnetic fields.

*Index Terms*—Circuit simulation, magnetic tunnel junction (MTJ) model, spin-transfer torque magnetic random access memory (STT-MRAM).

#### I. INTRODUCTION

PIN-TRANSFER torque magnetic random access memory (STT-MRAM) is a next-generation nonvolatile memory technology for a variety of applications, such as enterprise SSD, industrial-grade MCU, automotive, and AIoT [1]. In recent years, its commercialization progress toward both discrete and embedded memories has accelerated with heavy investments from major semiconductor companies worldwide. For example, Everspin first commercialized discrete STT-MRAM (64 Mb) chips in 2015 and started shipping 1-Gb parts in 2019 [2]. SK hynix [3], Samsung [4], Globalfoundries [1], and TSMC [5] all revealed their STT-MRAM solutions in

Manuscript received 30 August 2021; revised 16 November 2021; accepted 15 December 2021. Date of publication 4 January 2022; date of current version 24 October 2022. This work was supported in part by the Natural Science Foundation of China under Grant 61832020; in part by the National Key Research and Development Program of China under Grant 2019YFB1804502; in part by the Guangdong Major Project of Basic and Applied Basic Research under Grant 2019B030302002; in part by the Natural Science Foundation of Guangdong Province under Grant 2018B030312002; and in part by the Key-Area Research and Development Program of Guangdong Province under Grant 2019B010107001. This article was recommended by Associate Editor W. Yu. (Corresponding author: Lizhou Wu.)

Lizhou Wu is with the School of Computer, National University of Defense Technology, Changsha 564211, China (e-mail: njuwulizhou@gmail.com).

Siddharth Rao, Erik Jan Marinissen, and Gouri Sankar Kar are with the Compute and Memory Department, IMEC, 3001 Leuven, Belgium (e-mail: siddharth.rao@imec.be; erik.jan.marinissen@imec.be; gouri.kar@imec.be).

Mottaqiallah Taouil and Said Hamdioui are with the Quantum and Computer Engineering Department, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: m.taouil@tudelft.nl; s.hamdioui@tudelft.nl).

Digital Object Identifier 10.1109/TCAD.2021.3140157

recent years and claimed they are production ready. Similar to the development process of all semiconductor products, STT-MRAM design, design automation, and test using commercial computer-aided design tools play a critical role. The data-storing elements in STT-MRAMs are magnetic tunnel junction (MTJ) devices, which are inserted between two adjacent metal layers in the back-end-of-line process [6]. MTJ devices are typically selected, programmed, and read out using CMOS-based circuits. Therefore, it is crucial to develop a SPICE-compatible compact MTJ model, which accurately captures both the *magnetic and electrical characteristics* of MTJ with reasonable simulation overhead for fast and robust STT-MRAM design.

Several MTJ models with different features and implementation methods have been introduced in [7]-[14]. Generally, they can be classified into four categories: models; 2) commercialized-tool-based 1) micromagnetic models; 3) macromodels; and 4) behavioral models [7]. Micromagnetic MTJ models are implemented using micromagnetic simulation tools such as OOMMF, which offers high simulation accuracy and is able for studying the switching dynamics of a single MTJ [8]. The commercialized-toolsbased models, such as Sentaurus Device, provide decent simulation accuracy of a single MTJ as well as small MTJ/CMOS circuits [9]. Macro MTJ models are composed of SPICE built-in circuit elements, such as resistors, capacitors, and voltage-/current-dependent voltage/current sources [10]; this type of MTJ model owns good compatibility with circuit simulators, but the number of circuit elements dramatically increases with the complexity of MTJ's dynamic characteristics. Behavioral MTJ models describe the analog behaviors of MTJ using a hardware description language such as Verilog-A; they gain popularity for circuit-level simulations due to several advantages, including: 1) good compatibility with circuit simulators; 2) fast simulation; 3) flexible configuration with input parameters; and 4) easiness of designing, sharing, and upgrading. In view of this, many Verilog-A MTJ models have been presented and improved over the past decade [11]-[15]. Nevertheless, these MTJ models were not capable of simulating magnetic coupling effects and external field disturbance on MTJ's performance, which poses a critical constraint for STT-MRAM designs as reported with silicon characterization data in [1], [16], and [17].

This article presents a versatile compact perpendicular MTJ (pMTJ) model: MFA-MTJ model, which is magnetic-field-aware for SPICE-based hybrid MTJ/CMOS circuit simulations. It is well recognized that MTJ retention and switching characteristics are very sensitive to all sources of magnetic fields, including internal intracell and intercell stray fields and external disturbance fields in the operating environment. Therefore, we have developed a physics-based analytical

1937-4151 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

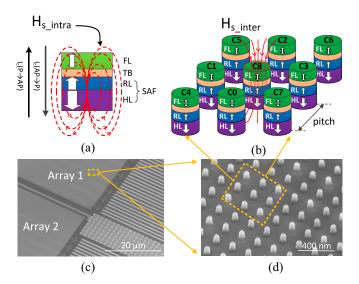

Fig. 1. (a) MTJ stack and the intracell stray fields from the RL and HL. (b)  $3\times 3$  MTJ array and the intercell stray fields from neighboring cells. (c) SEM image of the 0T1R wafer floorplan. (d) SEM image of MTJ array.

model for stray fields in STT-MRAMs [17]. Building on top of this work, we propose the MFA-MTJ model, which to our knowledge is the first work that enables *magnetic/electrical co-simulation* of MTJ-based spintronic circuits under various sources of magnetic fields. The main contributions are listed as follows.

- 1) Present magnetic characterization results of MTJ devices fabricated at IMEC with diameters from 35 to 175 nm.

- Integrate the above model into a Verilog-A compact MTJ model for SPICE-based circuit simulation, which is aware of device size, array pitch, and magnetic fields.

- 3) Use the proposed MFA-MTJ model to explore the design space of STT-MRAM with peripheral circuits under PVT variations and different magnetic configurations.

The remainder of this article is organized as follows. Section II provides a background on STT-MRAM technology. Section III presents magnetic characterization data. Section IV evaluates the impact of internal fields on MTJ's performance indicators, such as the switching current and time. Section V integrates the proposed model into our MFA-MTJ model and details its implementation. Section VI elaborates MTJ electrical characteristics by performing dc and transient simulations of the MFA-MTJ model. Section VII demonstrates electrical/magnetic co-simulation of STT-MRAM full circuits and explores its design space under various variation sources. Finally, Section IX concludes this article.

#### II. BACKGROUND

In this section, we first introduce the MTJ stack design and its working principles. Thereafter, we introduce three sources of magnetic fields, including intra and intercell stray fields internally from STT-MRAM arrays and external disturbance fields that may arise from the working environment.

#### A. MTJ Structure and Working Principles

MTJ devices are the data-storing elements in STT-MRAMs. Each MTJ device stores one-bit data in the form of binary magnetic configurations. Fig. 1(a) shows the MTJ stack, which essentially consists of four layers: FL/TB/RL/HL. The hard layer (HL) is composed of [Co/Pt]<sub>x</sub>, which is used to pin the

magnetization in the upper reference layer (RL). The RL is generally built up with a Co/spacer/CoFeB multilayer, which is anti-ferromagnetically coupled to the HL. These two layers form a synthetic anti-ferromagnetic (SAF) structure, providing a strong fixed reference magnetization in the RL. The tunnel barrier (TB) layer is made of dielectric MgO, typically  $\sim 1$  nm. The TB product is commonly used to evaluate the TB resistivity, as it depends on the TB thickness but not the device size. The CoFeB-based free layer (FL) is the data-storing layer where the magnetization can be switched by a spin-polarized current. Note that the magnetization is perpendicular to the FL of MTJ (i.e., pMTJ); pMTJ offers better scalability toward smaller sizes and less write power, as opposed to the counterpart with in-plane magnetization [6]. Therefore, we limit our discussions to pMTJ, which dominates today's STT-MRAM designs in industry.

To work properly as memory devices, MTJs need to provide read and write mechanisms, which are realized by the tunneling magneto-resistance (TMR) effect and the spintransfer-torque (STT) effect [18]. Due to the TMR effect, the MTJ's resistance is low  $(R_P)$  when the magnetization in the FL is parallel to that in the RL, while the resistance is high  $(R_{AP})$ when in the anti-parallel state (see Fig. 2). For STT-MRAM, the low resistance state (LRS) represents logic "0," while the high resistance state (HRS) represents logic "1." If the write current magnitude (with sufficiently long pulse width) is larger than the critical switching current  $I_c$ , the magnetization in the FL can switch to the opposite direction. It is a fundamental parameter to characterize the switching capability by current. The STT-induced switching behavior also depends on the current direction, as shown in Fig. 1(a).  $I_c(AP \rightarrow P)$  can be significantly different from  $I_c(P \rightarrow AP)$  due to the bias dependence of STT efficiency and external field disturbance [18]. In addition, the average switching time  $t_w$  [19] is another critical parameter, which is inversely correlated with the write current. In other words, the higher the write current over  $I_c$ , the less the time required for the magnetization in FL to flip. In practice,  $t_w(AP \rightarrow P)$  can also differ from  $t_w(P \rightarrow AP)$  depending on the write current magnitude and duration.

In addition, enough retention time is required for STT-MRAMs depending on the target application. Storage applications require >10 years typically, while cache applications only necessitate ms-scale retention time [20]. An STT-MRAM retention fault occurs when the magnetization in the FL of the MTJ flips spontaneously due to thermal fluctuation. Thus, the STT-MRAM retention time is generally characterized by the *thermal stability factor* ( $\Delta$ ) [18]. The higher the  $\Delta$ , the longer the retention time.

#### B. Three Sources of Magnetic Field Disturbance

STT-MRAM performance is vulnerable to magnetic fields, which may arise from the following three sources.

1) Intracell Stray Field  $H_{s\_intra}$ : To obtain high TMR and strong interfacial perpendicular magnetic anisotropy (iPMA), our MTJ devices were annealed at 375 °C for 30 min in a vacuum chamber under the perpendicular (out-of-plane) magnetic field of 20 kOe. Once the ferromagnetic layers (i.e., FL, RL, and HL) in the MTJ stack are magnetized, each of them inevitably generates a stray field in the space. Fig. 1(a) illustrates the intracell stray field  $H_{s\_intra}$  perceived at the FL, generated by the RL and HL together; its in-plane component

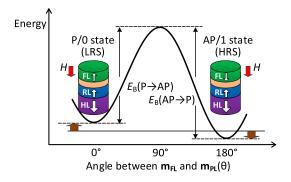

Fig. 2. Energy barrier  $E_B$  between AP and P states is bifurcated into  $E_B(P \rightarrow AP)$  and  $E_B(AP \rightarrow P)$  due to magnetic field H at the FL.

$H_{s\_intra}^{x-y}$  is marginal [21], while its out-of-plane component  $H_{s\_intra}^{x-y}$  at the FL has a significant influence on the energy barrier  $E_B$  between the P and AP states [22]. For example, if  $H_{s\_intra}^z$  has the same direction as the magnetization in FL in the AP state, it leads to an increase in  $E_b(AP \rightarrow P)$  and a decrease in  $E_b(P \rightarrow AP)$ , as illustrated in Fig. 2. The bifurcation of  $E_B$  along the two switching directions has a significant impact on the retention and the STT-switching characteristics of MTJ devices, as reported in [21] and [23]. In the extreme case where  $H_{s\_intra}^z$  exceeds the FL coercivity  $H_c$ , defined as the reverse field needed to drive the magnetization of a ferromagnet to zero, the bistable states disappear [24].

- 2) Intercell Stray Field  $H_{s\_inter}$ : As the density of STT-MRAMs increases, the spacing between neighboring MTJ devices becomes narrower (i.e., smaller pitch). This makes stray fields from neighboring cells not negligible any more [22], [25]. Fig. 1(b) shows a 3  $\times$  3 MTJ array, where the eight cells C0–C7 (aggressors) surrounding cell C8 (victim) in the center inevitably generate an intercell stray field  $H_{s\_inter}$  acting on the victim cell. Fig. 1(c) and (d) shows the scanning electron microscope (SEM) images of our 0T1R wafer floorplan and MTJ array, respectively.

- 3) External Disturbance Field  $H_{ext}$ : When being deployed in the field, STT-MRAM products may be subject to external magnetic fields unintentionally or maliciously in the operating environment. These unexpected disturbance fields further bifurcate  $E_B$  shown in Fig. 2, thus causing data retention and write errors when  $H_{ext}$  reaches a certain extent [16]. Lee  $et\ al.$  [26] observed with silicon measurements that the sensitivity of switching voltage  $V_c$  to  $H_{ext}$  was  $\sim 8\%/5000e$ ; with a 300- $\mu$ m thick shield at package level, the  $V_c$  sensitivity was reduced to  $\sim 3\%/5000e$ . Naik  $et\ al.$  [1] demonstrated STT-MRAM with 500 Oe magnetic immunity by boosting write voltage and adding 2-bit ECC.

#### III. CHARACTERIZATION OF INTRACELL STRAY FIELD

$H_{\rm s\_intra}^z$  can be extracted from R-H hysteresis loops. Fig. 3(a) shows a measured R-H hysteresis loop for a representative MTJ device with the HL/RL configuration shown in Fig. 1(a). During the measurement, an external field was applied perpendicularly to the device under test. It was ramped up from 0 to 3 kOe, and then it went backward to -3 kOe and finished at 0 Oe. In total, we measured 1000 field points, each of which was followed by a read operation to read out the device resistance with a voltage of 20 mV. The same measurement was repeated ten cycles and an example of a representative

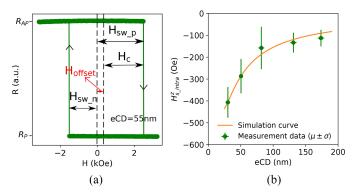

Fig. 3. (a) Measured R-H hysteresis loop. (b) Device size dependence of  $H_{\rm s.intra}^{z}$ : measured versus simulated.

R-H loop averaged over the measured ten cycles is shown in Fig. 1(a). It can be seen that the MTJ device switches from the AP state (high resistance) to P state (low resistance) when the field reaches at  $H_{sw_p}$ , and it switches back to the AP state at a negative field  $H_{sw_n}$ . The device coercivity can be obtained by  $H_c = (H_{sw_p} - H_{sw_n})/2$ . Due to the existence of stray fields at the FL, the loop is always offset to the positive side for the device configuration in Fig. 1(a). The offset field  $H_{\text{offset}}$  is equal to  $(H_{\text{sw\_p}} + H_{\text{sw\_n}})/2$ , as shown in the figure. Since  $H_{\text{offset}}$  is essentially equivalent to the extra external field applied to cancel out  $H_{s\_intra}$ , the relation of these two parameters is  $H_{\rm s~intra} = -H_{\rm offset}$ . Given the fact that the resistance-area (RA) product does not change with the device size, the electrical critical diameter (eCD) of each device can be derived by [27]:  $eCD = \sqrt{(4/\pi) \cdot (RA/R_P)}$ , where RA = 4.5  $\Omega \cdot \mu m^2$  (measured at blanket stage) for this wafer, and  $R_P$  can be extracted from the R-H loop [i.e., the lower horizontal line in Fig. 3(a)]. The calculated eCD for the device in Fig. 3(a) is 55 nm.

In this way, we can obtain  $H_{s \text{ intra}}^z$  and eCD for MTJ devices with different sizes on the same wafer. The measurement results are shown in Fig. 3(b). The error bars indicate the device-to-device variation in the measured values due to process variations (PVs) and the intrinsic switching stochasticity. Note that the switching stochasticity inevitably introduced measurement errors in the stray fields, thus amplifying its standard deviation as seen in the figure. This is because the intracell stray fields were calculated from the measured switching fields  $H_{sw_p}$  and  $H_{sw_n}$ , which have cycle-to-cycle variations due to the switching stochasticity. A key observation is that the smaller the device size (i.e., smaller eCD), the higher  $H_{\rm s~intra}^{\rm z}$ ; the trend even tends to grow exponentially for eCD<100 nm. This is because the stray fields generated by the ferromagnets below FL are approximately proportional to  $(1/eCD^2)$  when maintaining the same  $H_k$  and  $M_s$  at blanket level before etching. Similar results were shown using micromagnetic simulations in [23] and [24]. The solid curve in the figure represents simulation results, which will be explained in the next section.

## IV. IMPACT OF INTERNAL STRAY FIELDS ON MTJ PERFORMANCE

In this section, we first briefly discuss our stray field model proposed in [17]. Thereafter, we use the proposed model to evaluate the impact of internal stray fields on the critical switching current  $I_c$  and the average switching time  $t_w$ . We also investigate the impact on the thermal stability factor  $\Delta$  in a similar way. Simulation results for MTJ devices with eCD = 35 nm are presented as an example.

#### A. Internal Stray Field Modeling

To analyze and quantify the effects of magnetic fields on the MTJ's performance, we need to first develop an accurate model to cover all the three sources of magnetic field disturbance as mentioned in Section II-B.  $H_{\rm ext}$  originates from the external surroundings, thus independent on any STT-MRAM design; it can be directly fed into a Verilog-A MTJ model as an input parameter. In contrast,  $H_{\rm s\_intra}$  and  $H_{\rm s\_inter}$  both depend on STT-MRAM designs, thus requiring an accurate stray field model. To this end, we first modeled and calibrated  $H_{\rm s\_intra}$  for isolated MTJ devices using the bound current theory and Biot–Savart law. Thereafter, we extrapolated this model to derive  $H_{\rm s\_inter}$  for an memory array with various pitches. The modeling details can be found in our prior work [17].

It is worth noting that our stray field model is able to take into account the initial angle  $\theta_0$  between the magnetization  $(m_{FL})$  of the FL and the z-axis. Due to the thermal fluctuation effect, the direction of  $m_{FL}$  may deviate from the z-axis with an initial angle  $\theta_0$ , which we model using the following equation [28], [29]:

$$\theta_0 = \sqrt{\frac{k_B T}{\mu_0 M_s V H_k}} \tag{1}$$

where  $\mu_0$  is the vacuum permeability, T is the temperature,  $k_B$  is the Boltzmann constant,  $M_s$  is the saturation magnetization, V is the volume of the FL, and  $H_k$  is the magnetic anisotropy field. Since  $\theta_0$  is induced by the thermal fluctuation, its value is intrinsically random. Therefore, we assigned a Gaussian distribution to it. We then took it into account in our stray field simulations by tilting the bound current loop representing  $m_{\rm FL}$  by an angle away from the z-axis.

#### B. Impact on the Critical Switching Current

Under the influence of stray field,  $I_c$  can be expressed as follows [18]:

$$I_c(H_{\text{stray}}^z) = \frac{1}{\eta} \frac{2\alpha e}{\hbar} M_s \cdot V \cdot H_k \cdot \left(1 \pm \frac{H_{\text{stray}}^z}{H_k}\right)$$

(2)

where  $\eta$  is the STT efficiency,  $\alpha$  is the magnetic damping constant, e the elementary charge,  $\hbar$  is the reduced Planck constant,  $M_s$  is the saturation magnetization, V is the volume of the FL, and  $H_k$  is the magnetic anisotropy field. The sign in the parentheses is "+" for  $I_c(P \rightarrow AP)$  and "-" for  $I_c(AP \rightarrow P)$ , given the definition of coordinates in this article. In (2),  $H_{\text{stray}}^z = H_{\text{s_intra}}^z + H_{\text{s_inter}}^z$  can be calculated with our proposed magnetic coupling model taking into account both intracell and intercell stray fields, while  $H_k$  needs to be extracted from measurement data. The other parameters in the equation are measured at blanket stage before etch. Since the switching points [i.e.,  $H_{\text{sw_p}}$  and  $H_{\text{sw_n}}$  in Fig. 3(a)] are intrinsically stochastic, we measured the R-H loop of the same device for 1000 cycles to obtain a statistical result of the switching probability at varying fields. With the technique

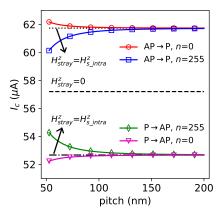

Fig. 4.  $I_c$  versus pitch under the circumstance of different stray fields.

proposed in [30], we are able to extract  $H_k$  and  $\Delta_0$  by performing curve fitting.  $\Delta_0$  is the intrinsic thermal stability factor without any stray field at the FL; it will be used in the next subsection. By doing this for a large number of devices, we obtained  $\Delta_0 = 45.5$  and  $H_k = 4646.8$  Oe (both in median) for devices with eCD = 35 nm.

Fig. 4 shows the critical switching current  $I_c$  for C8 (for both  $P \rightarrow AP$  switching and  $AP \rightarrow P$  switching) at different pitches with respect to various stray fields. For isolated devices without any stray field (i.e., ideal case,  $H_{\text{stray}}^z = 0$ ), the intrinsic  $I_c$  for the two switching directions is supposed to show no difference;  $I_c = 57.2 \,\mu\text{A}$ . When taking into account the intracell stray field (i.e.,  $H_{\text{stray}}^z = H_{\text{s\_intra}}^z$ ), a static shift in  $I_c$  is introduced, making  $I_c(\text{AP} \rightarrow \text{P}) = 61.7 \,\mu\text{A}$  (i.e., 7% above the intrinsic  $I_c$ ) and  $I_c(P \rightarrow AP) = 52.8 \,\mu\text{A}$  (i.e., 7% below). When considering both intracell and intercell stray fields (i.e.,  $H_{\rm stray}^z = H_{\rm s\_intra}^z + H_{\rm s\_inter}^z$ ) for different neighborhood patterns NP<sub>8</sub>, the impact on  $I_c$  shows a clear dependence on the array pitch.  $I_c(AP \rightarrow P)$  becomes larger at smaller pitches when  $NP_8 = 0$ , while it shows an opposite trend when  $NP_8 = 255$ . This indicates that the variation in  $I_c(AP \rightarrow P)$  between different neighborhood patterns increases as the pitch goes down. It can be seen that at pitch  $\approx 80$  nm (corresponding to  $\Psi = 2\%$ ), the variation is marginal. Similar observations can be seen on the  $P \rightarrow AP$  switching direction.

#### C. Impact on the Average Switching Time

The average switching time  $t_w$  in the presence of  $H_{\text{stray}}^z$  in the precessional regime (namely, switched by the STT-effect) can be estimated using Sun's model [31] as follows:

$$t_{w}\left(H_{\text{stray}}^{z}\right) = \left(\frac{2}{C + \ln\left(\frac{\pi^{2}\Delta}{4}\right)} \cdot \frac{\mu_{B}P}{em(1 + P^{2})} \cdot I_{m}\right)^{-1}$$

(3)

$$I_{m} = I_{\text{MTJ}} - I_{c}\left(H_{\text{stray}}^{z}\right).$$

(4)

Here,  $C \approx 0.577$  is Euler's constant,  $\mu_B$  is the Bohr magneton, P is the spin polarization, e is the elementary charge, and m is the FL magnetization.  $I_{\text{MTJ}}$  is the current flowing through the MTJ device. Note that we assume the STT switching statistics obey a normal distribution, as shown with silicon data and simulation results in [32] and [33]; the variance increases with  $t_w$ . Therefore, we consider the impact of stray fields  $H_{\text{stray}}^2$  on

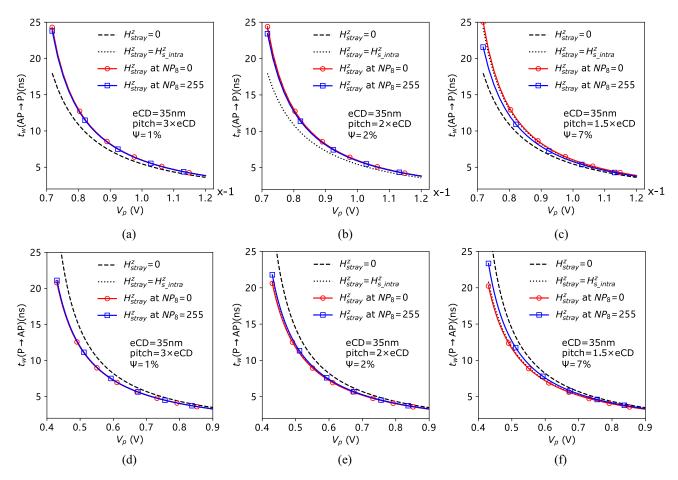

Fig. 5. Impact of internal stray fields on the voltage dependence of  $t_w$  with eCD = 35 nm at various pitches. (a)  $3 \times \text{eCD}$ ,  $AP \rightarrow P$  switching. (b)  $2 \times \text{eCD}$ ,  $AP \rightarrow P$  switching. (c)  $1.5 \times \text{eCD}$ ,  $AP \rightarrow P$  switching. (d)  $3 \times \text{eCD}$ ,  $AP \rightarrow AP$  switching. (e)  $2 \times \text{eCD}$ ,  $AP \rightarrow AP$  switching. (f)  $AP \rightarrow AP$  switching. (e)  $AP \rightarrow AP$  switching. (e)  $AP \rightarrow AP$  switching. (f)  $AP \rightarrow AP$  switching.

the switching stochasticity by incorporating  $H_{\text{stray}}^z$  into  $t_w$  and keeping the same dependence of the variance on  $t_w$ .

Fig. 5(a)-(c) shows the voltage dependence of the average switching time from AP state to P state  $(t_w(AP \rightarrow P))$  for MTJs with eCD = 35 nm at pitch =  $3 \times \text{eCD}$ ,  $2 \times \text{eCD}$ , and 1.5  $\times$  eCD, respectively. It can be seen that  $t_w(AP \rightarrow P)$ becomes larger for MTJ devices in the presence of internal stray field  $H_{\text{stray}}^{z}$  (solid lines), comparing to devices without any internal stray field (dashed lines). It is worth noting that the larger the voltage, the smaller the impact of  $H_{\text{stray}}^z$  on  $t_w(AP \rightarrow P)$ . However, an increase in the switching voltage  $V_{\rm MTJ}$  also results in more power consumption and a higher vulnerability to breakdown. In addition, when the pitch goes from 3  $\times$  eCD [Fig. 5(a)] to 2  $\times$  eCD [Fig. 5(b)], the intercell magnetic coupling factor Ψ increases from 1% to 2% and the change in  $t_w(AP \rightarrow P)$  is negligible. However, when the pitch goes down to 1.5  $\times$  eCD [Fig. 5(c)],  $\Psi$  increases to 7% and the variation in  $t_w(AP \rightarrow P)$  between different NPs (i.e.,  $H_{s \text{ inter}}^{z}$ ) becomes very visible. For example, at a voltage of 0.72 V,  $t_w(AP \rightarrow P)$  under  $NP_8 = 0$  is  $\sim 4$  ns slower than NP<sub>8</sub> = 255, as shown in Fig. 5(c). This indicates that a larger write margin (e.g., a longer pulse) is required to avoid write failure in the worst case (i.e.,  $NP_8 = 0$ ). Similarly, Fig. 5(d)–(f) shows the simulation results of the other switching direction:  $P \rightarrow AP$ , under the same Python simulation setup. It is clear that  $H_{\text{stray}}^{z}$  exerts an inverse influence on  $t_{w}(P \rightarrow AP)$ , in comparison to  $t_w(AP \rightarrow P)$ . When pitch = 1.5 × eCD [see Fig. 5(f)],  $NP_8 = 0$  facilitates  $P \rightarrow AP$  switching to the highest extent,

whereas the same data pattern impedes  $AP \rightarrow P$  switching the most [see Fig. 5(c)].

#### D. Impact on the Thermal Stability Factor

The intrinsic thermal stability factor  $\Delta_0$  (without any stray field at the FL) of the MTJ device is given by [18]:  $\Delta_0 = [(H_k M_s V)/(2k_B T)]$ , where  $k_B$  is the Boltzmann constant and T is the absolute temperature. However, in the presence of stray fields, the thermal stability factor in the AP state deviates from that in the P state, i.e.,  $\Delta_{AP} \neq \Delta_P$ . The  $\Delta$  value in the presence of  $H_{\text{stray}}^z$  is given by [18]

$$\Delta \left( H_{\text{stray}}^{z} \right) = \Delta_0 \left( 1 \pm \frac{H_{\text{stray}}^{z}}{H_k} \right)^2 \tag{5}$$

where the sign in the parentheses is "+" for  $\Delta_P$  and "-" for  $\Delta_{AP}$  for the devices considered in this article.  $H^z_{\text{stray}}$  can be calculated with our proposed magnetic coupling model, while  $H_k$  and  $\Delta_0$  are extracted from measurement data, as explained previously.

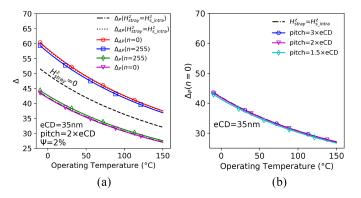

Fig. 6(a) shows the thermal stability factor  $\Delta$  at varying temperature for eCD = 35 nm and pitch = 2 × eCD, corresponding to  $\Psi$  = 2%. It can be seen that the intracell stray field  $H_{\rm s\ intra}^z$  introduces a static shift in  $\Delta_{\rm AP}$  and  $\Delta_P$ ;  $\Delta_{\rm AP}$  is ~30% smaller than  $\Delta_P$  comparing the dash-dotted line to the dotted one. The solid lines represent the thermal stability factors considering both intracell and intercell magnetic coupling. It can be seen that the MTJ device has the smallest

Impact of magnetic coupling on  $\Delta$  with eCD = 35 nm at: (a) pitch =  $2 \times \text{eCD}$  and (b) worst case  $\Delta$  for pitch =  $3 \times \text{eCD}$ ,  $2 \times \text{eCD}$ ,

$\Delta$  (highest vulnerability to a retention fault) when the victim cell is in P state and all neighboring cells are also in P state (i.e.,  $NP_8 = 0$ ). Note that we think it is more important to identify the worst case  $\Delta$  instead of its maximum variation, under the influence of array pitch and data pattern in the neighborhood. As long as  $\Delta_P(NP_8 = 0)$  (worst case here) meets the minimum requirement of retention time for a specific application, the other cases should also be acceptable. Fig. 6(b) compares the curve of  $\Delta_P(NP_8 = 0)$  versus temperature at pitch =  $3 \times \text{eCD}$ ,  $2 \times \text{eCD}$ , and  $1.5 \times \text{eCD}$ . One can observe that  $\Delta_P(NP_8 = 0)$  shows a marginal degradation when the array pitch goes down to  $1.5 \times eCD$ , in comparison to pitch =  $2 \times eCD$ .

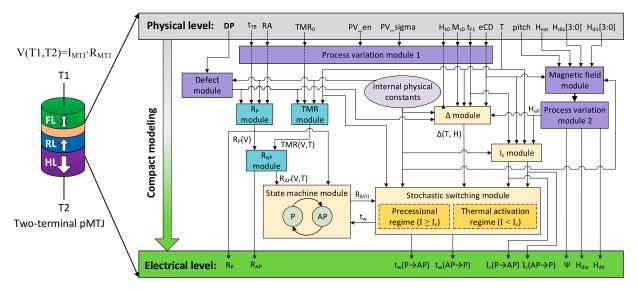

#### V. IMPLEMENTATION OF MFA-MTJ MODEL

Robust and fast STT-MRAM design requires an accurate MTJ model for efficient circuit simulations. After verifying the proposed physics-based model of internal stray fields and its impact on MTJ performance in Python, we integrated this model into our Verilog-A pMTJ model; we name the resultant magnetic-field-aware pMTJ model as the MFA-MTJ model. In this section, we first overview the block diagram of the MFA-MTJ model. Thereafter, we delve into each internal functional module and elaborate its functions and modeling principles.

#### A. Overview of MFA-MTJ Model

Fig. 7 illustrates the block diagram of our MFA-MTJ model. This model has two terminals and meets Ohm's law: i.e.,  $V(T1, T2) = I_{\text{MTJ}} \cdot R_{\text{MTJ}}$ . The MTJ resistance  $R_{\text{MTJ}}$  depends on the magnetic state AP or P, the bias voltage V(T1, T2), and the ambient temperature T;  $R_{\text{MTJ}}$  can also be switched between  $R_P$  and  $R_{AP}$ , depending on the current  $I_{MTJ}$  and its duration. In essence, the compact MTJ model describes the complex relationships between these three electrical variables. It abstracts an MTJ device from physical level to electrical level via compact behavioral modeling, described in an analog circuit description language: Verilog-A. In other words, the inputs of the MFA-MTJ model are physical and technology parameters (e.g., eCD and RA) and the outputs are MTJ's electrical parameters (e.g.,  $R_P$  and  $I_c$ ); the mapping relationships from the inputs to the outputs are analytically described by physical equations such as (2).

The internal implementation of the MFA-MTJ model consists of different functional modules, as shown in Fig. 7.

We divide them into three groups. First, the  $R_P$ , TMR, and  $R_{\rm AP}$  modules are all concerned with the modeling of MTJ resistance. Second, the  $\Delta$ ,  $I_c$ , stochastic switching, and state machine modules are related to the modeling of MTJ switching behavior. Third, MTJ devices are never fabricated perfectly in practice. The MTJ resistance and switching behavior are significantly influenced by several factors, such as magnetic fields, PVs, and manufacturing defects. These factors have a large impact on MTJ performance, thus requiring special attention. Next, we elaborate these three groups of functional modules in detail.

#### B. Modeling of MTJ Resistance

1) R<sub>P</sub> Module: The physical model of MTJ's TMR originates from [34], where it indicates that the resistance is mainly determined by the TB thickness and the interfacial effects between TB and adjacent CoFeB layers. The resistance in P state  $R_P$  decreases slightly with bias voltage V and it can be approximately considered independent on temperature [35]. We adopted the following two equations to model  $R_P$  at varying bias voltage and fitted the modeling results to our measurement data in [14]:

$$R_{P}(V) = \frac{R_{0}}{1 + s \cdot |V|}$$

$$R_{0} = \frac{t_{\text{ox}}}{F \cdot \sqrt{\bar{\varphi}} \cdot A} \exp\left(\operatorname{coef} \cdot t_{\text{TB}} \cdot \sqrt{\bar{\varphi}}\right).$$

(6)

$$R_0 = \frac{t_{\text{ox}}}{F \cdot \sqrt{\bar{\varphi}} \cdot A} \exp\left(\text{coef} \cdot t_{\text{TB}} \cdot \sqrt{\bar{\varphi}}\right). \tag{7}$$

$t_{\rm TB}$  is the TB thickness,  $\bar{\varphi}$  is the potential barrier height of MgO, and  $A = (1/4) \cdot eCD^2$  is the horizontal cross section of the MTJ device. F, coef, and s are fitting coefficients depending on the RA product as well as the material composition of the MTJ layers.

2) TMR Module: The TMR ratio plays a critical role in determining the difficulty of distinguishing  $R_P$  and  $R_{AP}$  in read operations. Thus, a high TMR ratio, preferably above 180%, is expected in practice for commercially feasible STT-MRAM products. A recent study [36] reported that TMR = 249%was achieved, which represents a key step toward the commercialization of STT-MRAM. The experimental results have showed that TMR ratio decreases with both temperature T and bias voltage V [37]. We model the dependence of TMR ratio on V and T as follows [14], [35]:

$$TMR(T) = \frac{TMR_0 + 1}{1 + 2Q \cdot \beta_{AP} \cdot \ln\left(\frac{k_B T}{E_r}\right)} - 1$$

(8)

$$TMR(T) = \frac{TMR_0 + 1}{1 + 2Q \cdot \beta_{AP} \cdot \ln\left(\frac{k_B T}{E_c}\right)} - 1$$

$$TMR(T, V) = TMR(T) \cdot \left(1 + \frac{V^2}{V_h^2} + b \cdot V^{\frac{4}{3}}\right)^{-1}.$$

(9)

In the above equations,  $TMR_0$  is the TMR ratio at T = 0 K and V = 0 V. Q describes the probability of a magnon involved in the tunneling process.  $\beta_{AP} = Sk_BT/E_m$ , where S is the spin parameter,  $k_B$  is the Boltzmann constant, and  $E_m$  is related to the Curie temperature  $T_c$  of the ferromagnetic materials:  $E_m = 3k_BT_c/S + 1$ .  $E_c$  is the magnon cutoff energy.  $V_{\rm h}$  and b are both fitting parameters.

3)  $R_{AP}$  Module: Based on (6)–(9),  $R_{AP}$  at certain T and V can be derived accordingly

$$R_{AP}(T, V) = R_P(V) \cdot (1 + TMR(T, V)).$$

(10)

Fig. 7. Block diagram of the proposed MFA-MTJ model for simulations of hybrid MTJ/CMOS circuits.

#### C. Modeling of MTJ Switching Behavior

1)  $\triangle$  Module: The thermal stability factor  $\triangle$  is a figure of merit for MTJs.  $\Delta$  directly determines the retention time of data stored in an MTJ and it also has an impact on the switching behavior between AP and P states. Under the macrospin assumption (i.e., the magnetization in the FL switches uniformly as a whole),  $\Delta$  can be expressed as [18] and [35]

$$\Delta = \frac{E_B}{k_B T} = \frac{\mu_0 \cdot t_{\text{FL}} \cdot M_s(T) \cdot A \cdot H_k(T)}{2k_B T}$$

(11)

$$\Delta = \frac{E_B}{k_B T} = \frac{\mu_0 \cdot t_{\text{FL}} \cdot M_s(T) \cdot A \cdot H_k(T)}{2k_B T}$$

$$M_s(T) = M_{s0} \cdot \left(1 - \frac{T}{T^*}\right)^{\frac{3}{2}}$$

(12)

$$H_k(T) = f_1 \cdot T + f_2. \tag{13}$$

In (11),  $\mu_0$  is the vacuum permeability and the other physical parameters have been introduced previously. Note that  $M_s$ and  $H_k$  are both dependent on T, as suggested by the experimental and modeling results in [38]. From the same paper, we extracted (12) and (13) for modeling the temperature dependence of  $M_s$  and  $H_k$  in our MFA-MTJ model.  $M_{s0}$  is the saturation magnetization of the FL at 0 K;  $T^*$ ,  $f_1$ , and  $f_2$  are all fitting parameters.

- 2) I<sub>c</sub> Module: The magnetization dynamics in the STT switching process is typically described by the Landau-Lifshitz-Gilbert (LLG) equation with the addition of STTrelated terms, under the assumption of macrospin approximation [14], [18]. Solving the LLG equation results in (2) for the critical switching current  $I_c$ .

- 3) Stochastic Switching Module: The switching behavior between AP and P states is a complex process, which is intrinsically stochastic and dependent on the applied pulse width  $t_p$ . Depending on the mechanism that dominates the switching behavior, the entire switching spectrum can be divided into two regimes: 1) precessional regime and 2) thermal activation regime. In the precessional regime where  $t_p < \sim 40$  ns, the STT effect is the main driving force that flips the magnetization of FL. In this regime, the average switching time  $t_w$  can be estimated using Sun's model, namely, (3) and (4). The actual switching time varies from one pulse to another (i.e., switching stochasticity). The root cause can be attributed

to the variation of incubation time after the pulse onset, due to thermal fluctuation. We model the switching stochasticity by assigning a normal distribution to  $t_w$ , which has a fair agreement with measurement data [33], [35]. In the thermal activation regime where the pulse width increases above 40 ns, observed in our devices, a small current less than  $I_c$  is able to flip the magnetization due to the increased thermal fluctuation. The thermal fluctuation plays a main role in determining the switching behavior. In this regime, the Neel-Brown model can be used to describe the average switching time  $t_w$  [14]

$$t_w = \tau_0 \exp\left(\Delta \left(1 - \frac{I_{\text{MTJ}}}{I_c}\right)\right) \tag{14}$$

where  $\tau_0$  is the attempt period ( $\sim 1$  ns). The actual switching time in this regime is modeled as an exponential distribution with its mean value at the calculated  $t_w$  in (14) [13], [39]. As a result, the switching probability  $Pr(t_p)$  under a long pulse with current  $I_{\text{MTJ}}$  and width  $t_p$  is [40]

$$\Pr(t_p) = 1 - \exp\left(-\frac{t_p}{t_w}\right). \tag{15}$$

Equations (14) and (15) are commonly used to estimate the read disturb rate, as the read current shares the same path and direction with the write current in w0 operations [19].

4) State Machine Module: The state machine controls the transition between P and AP states at runtime. It outputs the MTJ resistance  $R_{\text{MTJ}} \in \{R_P, R_{\text{AP}}\}\$  to the stochastic switching module for calculating  $I_{\text{MTJ}}$  under the voltage bias V(T1,T2) applied across the MTJ device. Meanwhile, the stochastic switching module sends  $t_w$  to the state machine to activate a transition between P and AP states when meeting all switching conditions.

#### D. Modeling of Other Key Characteristics

1) Magnetic Field Module: Analog circuit simulators, such as Cadence Spectre and HSPICE, are intended for simulations of electrical circuits. With the emergence and fast development of spintronics, there is a need of simulating hybrid MTJ/CMOS circuits, such as STT-MRAM, magnetic flip-flop,

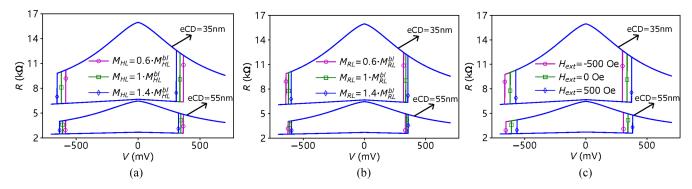

Fig. 8. DC simulation results of R-V loops for MTJs with eCD = 35 and 55 nm, with respect to different configurations of magnetic fields at the FL.

and magnetic full adder. Unlike MOSFETs where only electrical properties matter, MTJ devices own both electrical and magnetic properties. These two types of properties are typically interacted exploiting the spin and charge properties of electron, and they are very sensitive to magnetic fields, as mentioned in the previous sections. Therefore, it is paramount to consider and evaluate the effects of magnetic fields when simulating and designing MTJ-based circuits. As a solution, we implemented our magnetic field module presented in the previous sections using Verilog-A and then integrated it into our MFA-MTJ model. The magnetic field module takes into account three sources of magnetic fields

$$H_{\text{all}} = H_{\text{s intra}}^{z} + H_{\text{s inter}}^{z} + H_{\text{ext}}^{z}.$$

(16)

In the above equation,  $H_{s\_intra}^z$ ,  $H_{s\_inter}^z$ , and  $H_{ext}^z$  are the out-of-plane components of intracell stray field, intercell stray field, and external stray field, respectively.  $H_{s\_intra}^z$  is calculated internally in the MFA-MTJ model, depending on eCD and pitch.  $H_{s_{inter}}^{z}$  consists of  $H_{dir}[3:0]$  and  $H_{dia}[3:0]$ , standing for the intercell stray fields from four direct and four diagonal neighbors. Note that  $H_{\text{dir}}[3:0]$ ,  $H_{\text{dia}}[3:0]$ , and  $H_{\text{ext}}^z$ are all defined as electrical input ports, which connect to other MTJ devices or circuit elements. Together, these three magnetic fields result in a net overall field  $H_{all}$  acting on a specific MTJ device in an STT-MRAM array. The magnetic field module is connected to a PV module, which can introduce a Gaussian distribution to the calculated stray fields.  $H_{\rm all}$ is then fed into the  $\Delta$ ,  $I_c$ , and stochastic switching modules, as described by (2)–(5). The PV module for the magnetic field module also outputs  $\Psi$ ,  $H_{dir}$ , and  $H_{dia}$  at runtime (depending eCD, pitch, and MTJ state) via three electrical ports of the MFA-MTJ model in the form of voltage.

- 2) Defect Module: MTJ devices are typically fabricated and integrated between two adjacent metal layers (e.g., M4 and M5) in the BEOL of CMOS process; this process is unique to STT-MRAM and is susceptible to manufacturing defects [19]. We have successfully designed and integrated models for MTJ-internal defects, such as pinhole [6], SAF layer flip [33], and intermediate state [41] into our MFA-MTJ model. The effects of these defects are first incorporated into the physical parameters of MTJ and thereafter into the electrical parameters; these defect models were also corroborated and calibrated by silicon data of defective MTJ devices fabricated at IMEC.

- 3) Process Variation Module: PV is inevitable when fabricating integrated circuits. The impact of PV on the performance and reliability of integrated circuits becomes increasingly pronounced as the CMOS technology node scales

down. To design robust STT-MRAM circuits, PV related to MTJ devices should also be taken into account. The PV module is implemented by assigning normal distributions to key MTJ dimension parameters such as eCD,  $t_{\rm FL}$ , and  $t_{\rm TB}$ , as well as key physical parameters, such as RA and TMR<sub>0</sub>. "PV\_en" and "PV\_sigma" are two input parameters of the compact MTJ model, controlling the internal PV module.

# VI. MTJ ELECTRICAL CHARACTERISTICS UNDER VARIOUS MAGNETIC CONFIGURATIONS

After obtaining the MFA-MTJ model, we verified it with Cadence Spectre, a commercial analog circuit simulator. In this section, we first present dc simulation results of the model. Thereafter, we present transient simulation results in the form of write error rate (WER) statistics.

#### A. DC Simulations: R-V Loops

Measuring R-V loops is a common practice to characterize the voltage dependence of MTJ resistance at P and AP states. We have calibrated the dc simulation results of R-V loops of our compact model with silicon data, as can be found in [14]. Fig. 8(a) shows the dc simulation results of R-V loops for MTJs with eCD = 35 and 55 nm. For each size, we simulated three configurations of HL by modifying its saturation magnetization  $M_{\rm HL}$ ; the change of  $M_{\rm HL}$  resulted in different stray fields at the FL.  $M_{\rm HL}^{\rm bl}$  means the baseline  $M_{\rm HL}$  from experimental results. It can be seen in Fig. 8(a) that both  $R_P$ and  $R_{AP}$  increase significantly as eCD decreases. A change in  $M_{\rm HL}$  has no impact on MTJ resistance, but it affects the switching voltage  $V_c$ . Reducing  $M_{\rm HL}$  by 40% of  $M_{\rm HL}^{\rm bl}$  leads to an increase in  $V_c$  for  $P \rightarrow AP$  switching and a decrease in  $V_c$  for AP $\rightarrow$ P switching. In contrast, increasing  $M_{\rm HL}$  by 40% of  $M_{\rm HL}^{\rm bl}$  results in an opposite effect on  $V_c$ , as shown in the figure. Similarly, we also simulated three values of saturation magnetization of RL  $(M_{RL})$  and three values of the external magnetic field at FL ( $H_{\text{ext}}$ ). The simulation results are shown in Fig. 8(b) and (c), respectively.

In addition to changing  $M_{HL}$  and  $M_{RL}$ , another common method in the community to tune the stray field at the FL is to change the cycle numbers of CoPt multilayers in the RL and HL [24], [42]. This represents the change of layer thickness of the RL and HL. In our stray field model [17], the magnetic moment of a ferromagnet is expressed as  $\mathbf{m} = M_s \cdot A \cdot t$ , where A is the cross sectional area of the ferromagnet and t is its thickness. Considering the bound current  $I_b$ ,  $\mathbf{m}$  can also be written as  $I_b \cdot A \cdot \hat{\mathbf{n}}$ , where  $\hat{\mathbf{n}}$  is the unit vector along the direction of  $M_s$ . Therefore, one can easily derive  $I_b = M_s \cdot t$ .

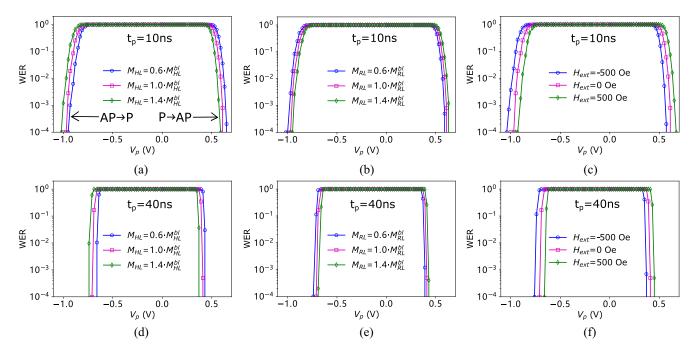

Fig. 9. Transient simulation results of WER versus bias voltage  $V_p$  for MTJs with eCD = 35 nm at pulse width  $t_p = 10$  and 40 ns. Note that negative  $V_p$  leads to AP $\rightarrow$ P switching operations while positive  $V_p$  leads to P $\rightarrow$ AP switching operations, as illustrated with the two arrows.

This suggests that changing the layer thickness t has a similar effect as  $M_s$  on the bound current and thus, on the stray field it generates in the near space.

#### B. Transient Simulations: WER Statistics

The MTJ switching behavior is intrinsically stochastic and is significantly dependent on the applied pulse width  $t_p$ and amplitude  $V_p$ . This characteristic directly affects STT-MRAM circuit designs, such as cell selector and write driver. Therefore, it is very important to experimentally characterize WER versus  $V_p$  at varying  $t_p$ , meanwhile providing a capability of simulating this characteristic to facilitate and verify circuit designs. Fig. 9(a)-(c) presents the simulation results of WER versus  $V_p$  at  $t_p = 10$  ns with respect to different magnetic configurations, using our MFA-MTJ model with eCD = 35 nm. It is clear that increasing the  $V_p$  magnitude is very effective in reducing WER for both switching directions; note that here a negative  $V_p$  results in AP $\rightarrow$ P switching whereas a positive  $V_p$  results in  $P \rightarrow AP$  switching. For the original MTJ design where  $M_{\rm HL}=M_{\rm HL}^{\rm bl},\,M_{\rm RL}=M_{\rm RL}^{\rm bl},$  and  $H_{\text{ext}} = 0 \text{ Oe}$ , the WER curve is asymmetric;  $|V_p(AP \rightarrow P)|$  is much larger than  $|V_p(P \rightarrow AP)|$  for a given WER value. By reducing  $M_{\rm HL}^{\rm bl}$  by 40%, the WER curve in Fig. 9(a) shifts to the right-hand side, indicating approximately one order of magnitude decrease in WER at a fixed  $V_p$  for AP $\rightarrow$ P switching and an opposite effect on  $P \rightarrow AP$  switching. Fig. 9(b) and (c) depicts how the WER curve is affected when modifying  $M_{RL}$ and  $H_{\text{ext}}$ , respectively. Fig. 9(d)–(f) presents similar simulation results, but at  $t_p = 40$  ns. It is worth noting that the slope of WER curve when  $t_p = 40$  ns is much larger than that when  $t_p = 10$  ns. This is because the switching variation is smaller at longer pulses, which is consistent with the measurement data of our devices [33] and others' devices [43], [44].

In summary, the above dc and transient simulation results suggest that our MFA-MTJ model is qualified for emulating MTJ devices for SPICE-based circuit simulations. By

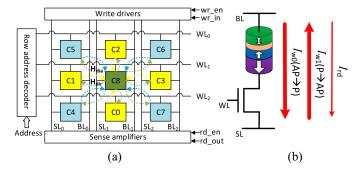

Fig. 10. (a)  $3\times 3$  STT-MRAM array with peripheral circuits. (b) 1T-1MTJ memory cell and the associated cell operations.

manipulating stray fields at the FL, which is achieved by adjusting the SAF design of the MTJ device, we can adjust the WER curve to the position that we desire when designing STT-MRAM cell and peripheral circuits. Hence, our MFA-MTJ model can be used for device/circuit co-design for STT-MRAM.

#### VII. ROBUSTNESS ANALYSIS OF STT-MRAM DESIGNS

Apart from a single MTJ device, we also simulated a  $3 \times 3$  STT-MRAM array with peripheral circuits, such as write driver and sense amplifier, as shown in Fig. 10(a). Each STT-MRAM cell consists of an MTJ device and an NMOS as a selector; Fig. 10(b) shows the memory cell and three basic operations [19]. The details of simulation circuits can be found in [6]; all transistors in the netlist were built with the 45-nm predictive technology model (PTM). In this section, we first present transient simulation results of the STT-MRAM full circuit under different eCDs and pitches. Thereafter, we explore the design space under PVT variations and different magnetic configurations.

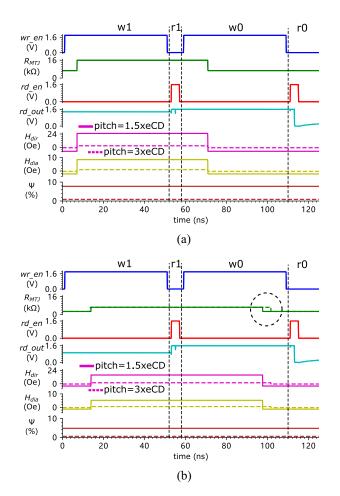

Fig. 11. Waveforms of key signals during the transient simulation of operation sequence: 0w1r1w0r0, under four different combinations of eCD and pitch. (a) eCD = 35 nm. (b) eCD = 55 nm. The dotted circle highlights the difference in 1w0 switching time under different pitch settings.

#### A. Transient Simulations Under Different eCDs and Pitches

To demonstrate the capability of our MFA-MTJ model for electrical/magnetic co-simulation under the SPICE-based circuit simulation environment, we simulated the STT-MRAM full circuit in Fig. 10 with two eCDs (35 and 55 nm) and two pitches (3 × eCD and 1.5 × eCD). During the simulations, we set the data background in C0–C7 at 255 (i.e., NP<sub>8</sub> = 255) and applied the operation sequence: 0 w1r1w0r0 to the central cell C8 as a case study.

Fig. 11(a) shows the simulation waveforms of seven key signals related to C8 when eCD = 35 nm. It can be seen that C8 is initialized to 0; it outputs  $H_{\rm dir} = -7.06$  Oe to its direct neighbors C0–C3 and  $H_{\rm dia} = -2.17$  Oe to its diagonal neighbors C4–C7 at pitch = 1.5 × eCD.  $\Psi$  is 7.8% at this pitch value. In contrast,  $H_{\rm dir}$ ,  $H_{\rm dia}$ , and  $\Psi$  are all close to 0 at pitch = 3 × eCD. During the w1 operation, the state of C8 transitions to 1 (see  $R_{\rm MTJ}$ );  $H_{\rm dir}$  and  $H_{\rm dia}$  are changed to 24.27 and 8.16 Oe, respectively, when at pitch = 1.5 × eCD. Following the w1 operation, r1 is applied, which outputs 1 on the signal rd\_out. Similar observations can be seen for the following w0 and r0 operations.

Fig. 11(b) shows the simulation waveforms when eCD = 55 nm. The following three differences from Fig. 11(a) are worth noting: 1) the switching time in both w1 and w0 operations becomes longer, as larger MTJ devices require larger

switching current; 2)  $H_{\rm dir}$ ,  $H_{\rm dia}$ , and  $\Psi$  are different due to the change of eCD; 3) when the pitch changes from 3 × eCD to 1.5 × eCD, the switching time during the w1 operation is larger while it becomes smaller in the w0 operation (see the circled part), due to the intercell magnetic coupling effect.

#### B. Design Space With Various Variation Sources

It is well known that STT-MRAM designs are significantly influenced by the following sources of variations: 1) PV (device-to-device variation); 2) supply voltage variation; 3) operating temperature variation; 4) MTJ switching stochasticity (cycle-to-cycle variation); and 5) magnetic field variation. We explored the design space considering the aforementioned five variation sources in our circuit simulations. The PV was modeled by assigning normal distributions to key parameters of both transistors and MTJs. For transistors, it was lumped into the variation in the threshold voltage  $V_{th}$  with 10% away from its nominal value at  $3\sigma$  corners. For MTJs, we assigned the same normal distribution to key input parameters shown in Fig. 7. In terms of supply voltage  $V_{\rm DD}$  variation, we assigned a uniform distribution to  $V_{DD}$  with its minimum at 1.5 V and maximum at 1.7 V. The typical industrial standard of operating temperature  $T \in [-40, 125]$  °C [1]. The MTJ switching stochasticity was implemented in our MFA-MTJ model and it can be enabled or disabled as required. The magnetic field variation includes  $H_{s\_intra}$ ,  $H_{s\_inter}$ , and  $H_{ext}$ as mentioned in the previous sections.

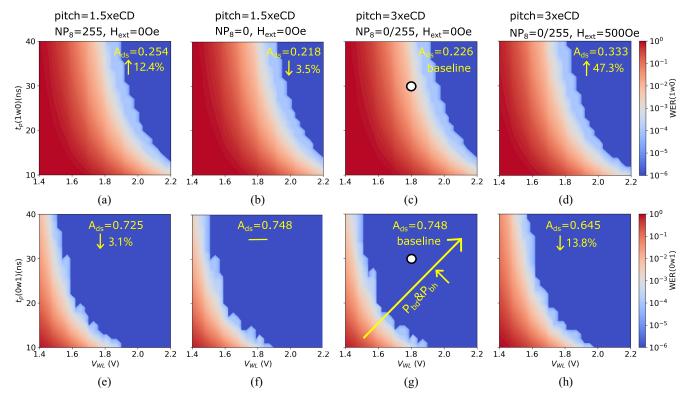

We performed 10k-cycle Monte Carlo simulations of 0w1 and 1w0 operations while sweeping two variables: 1) pulse width  $t_p$  and 2) voltage on the WL  $V_{WL}$ . This is based on the fact that boosting V<sub>WL</sub> is required to deliver sufficient switching current going through MTJ devices due to the source degeneration issue [19]; this has been a common practice in industry. Fig. 12(a) shows a contour plot of WER of 1w0 operation with respect to  $t_p$  and  $V_{WL}$ , when eCD = 35 nm, pitch = 1.5  $\times$  eCD, NP<sub>8</sub> = 255, and  $H_{\text{ext}} = 0$  Oe at room temperature T = 27 °C. It can be seen that WER(1w0) gradually decreases from the lower left corner to the upper right corner. When the 1w0 operations were all successful among the 10k Monte Carlo simulations, we marked the WER value at  $10^{-6}$  (i.e., the deep blue area). We define the area of design space  $A_{ds}$  as the normalized area where WER =  $10^{-6}$  with respect to the entire area of the contour plot. In Fig. 12(a),  $A_{\rm ds} = 0.254$ . This is 12.4% larger than the baseline  $A_{\rm ds}$ value in Fig. 12(c) where pitch =  $3 \times \text{eCD}$  and NP<sub>8</sub> has no influence. Fig. 12(b) shows the simulation results when pitch = 1.5 × eCD, NP<sub>8</sub> = 0, and  $H_{\text{ext}} = 0$  Oe;  $A_{\text{ds}}$  decreases by 3.5% in comparison to the baseline setup, due to the intercell magnetic coupling effect. In addition, we also studied the impact of  $H_{\text{ext}}$  on  $A_{\text{ds}}$ ; the result is shown in Fig. 12(d). When the STT-MRAM design is subject to an external magnetic field of 500 Oe,  $A_{ds}(1w0)$  increases by 47.3%.

Similarly, the simulation results for 0w1 operations are shown in Fig. 12(e)–(h). It is clear that  $A_{\rm ds}(0{\rm w}1)$  is much larger than  $A_{\rm ds}(1{\rm w}0)$  under the same simulation conditions, which suggests a critical design challenge facing STT-MRAM: write asymmetry. For example, when fixing  $t_p=30$  ns and  $V_{\rm WL}=1.8$  V, the resultant WER(0w1) has already reached the center of the deep blue area in Fig. 12(g) (see the white circle). In contrast, WER(0w1) has not entered into the deep blue area [see the white circle in Fig. 12(c)]. Worse still, the deeper

Fig. 12. WER at different combinations of  $t_p$  and  $V_{WL}$  for 1w0 and 0w1 operations under different simulation setups about pitch, NP<sub>8</sub>, and  $H_{\text{ext}}$ . The two white circles present the w0 and w1 operating points with fixed write pulse  $t_p = 30 \, \text{ns}$  and  $V_{WL} = 1.8 \, \text{V}$ .

Fig. 13. STT-MRAM write design space  $A_{\rm ds}$  versus (a) external magnetic field  $H_{\rm ext}$  and (b) operating temperature T.

the white circle enters into the deep blue area, the probability of breakdown ( $P_{\rm bd}$ ) or back-hopping ( $P_{\rm bh}$ ) becomes larger, as illustrated with the yellow arrow in Fig. 12(g). Moreover, the effects of NP<sub>8</sub> and  $H_{\rm ext}$  are always opposite for 0w1 operations, compared to 1w0 operations. This implies that the write asymmetry can be adjusted by manipulating magnetic fields. For example, applying  $H_{\rm ext} = 500$  Oe increases  $A_{\rm ds}(1\text{w0})$  by 47.3% [see Fig. 12(d)], whereas it reduces  $A_{\rm ds}(0\text{w1})$  by 13.8% [see Fig. 12(h)].

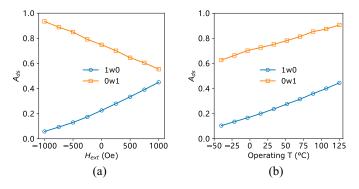

Fig. 13(a) shows the dependence of  $A_{\rm ds}$  on  $H_{\rm ext}$ . It can be observed that  $A_{\rm ds}(0 {\rm w1})$  significantly decreases with  $H_{\rm ext}$  whereas  $A_{\rm ds}(1 {\rm w0})$  shows an opposite trend. When  $H_{\rm ext} = \sim 1.1$  kOe, a symmetric design space for 0w1 and 1w0 operations is achieved. On the one hand, this suggests that we can design the SAF layer to generate the desired stray field at the FL (same effect as  $H_{\rm ext}$ ), meeting the requirements of circuit-level designs. On the other hand, we need to pay

attention to external magnetic disturbance, requiring packagelevel magnetic shield or other measures to enhance magnetic immunity [5].

Fig. 13(a) shows the dependence of  $A_{\rm ds}$  on the operating temperature T. It can be observed that  $A_{\rm ds}$  for both 1w0 and 1w0 significantly increases with T. Although high temperature is in favor of STT-MRAM write operations, it also brings side effects: 1) retention time reduction; 2) degraded read reliability due to TMR drop; and 3) increased vulnerability to breakdown and backhopping. For an industrial standard  $T \in [-40, 125]$  °C,  $A_{\rm ds}$  variation can reach up to 0.25. This implies the importance of having a field-programmable/self-adaptive write scheme for STT-MRAM, in order to select the optimal operating point for various working environments.

#### VIII. DISCUSSION AND FUTURE WORK

In this section, we briefly compare our proposed MTJ model with other models in the literature. Thereafter, we discuss the magnetic fields from current-carrying metal lines and how to use our model and its limitations.

#### A. Comparison With Other MTJ Model

We compared the proposed MFA-MTJ model in this work with other MTJ models in the literature using eight metrics, as shown in Table I.

Micromagnetic MTJ models based on OOMMF and mumax<sup>3</sup> obviously provide high simulation accuracy with high simulation overhead; they are suitable for studying switching dynamics and interactions of physical phenomena for a single MTJ. Commercialized-tool-based MTJ models offer medium simulation accuracy and overhead, and they are compatible

| Model Type                         | MTJ Model                                  | Sim.<br>Accuracy | Sim.<br>Overhead | Circuit Sim.<br>Compatibility | Flexibility | Scalability | Magnetic/Electrical<br>Co-Simulation | Defect Injection<br>&Fault Analysis | Silicon Data<br>Validation |

|------------------------------------|--------------------------------------------|------------------|------------------|-------------------------------|-------------|-------------|--------------------------------------|-------------------------------------|----------------------------|

| Micromagnetic model                | OOMMF [8]                                  | High             | High             | No                            | Low         | No          | No                                   | No                                  | Yes (First-hand)           |

|                                    | mumax <sup>3</sup> [45]                    | High             | High             | No                            | Low         | No          | No                                   | No                                  | No                         |

| Commercialized-tool<br>based model | Synopsis<br>Sentaurus Device [9]           | Medium           | Medium           | Yes                           | Low         | Low         | No                                   | No                                  | No                         |

| Macro model                        | SPICE-inbuit circuit<br>element model [10] | Medium           | Medium           | Yes                           | Medium      | Medium      | No                                   | No                                  | Yes (Second-hand)          |

| Behavioral model                   | Verilog-A model [13]                       | Medium           | Low              | Yes                           | High        | High        | No                                   | No                                  | Yes (Second-hand)          |

|                                    | This work                                  | Medium           | Low              | Yes                           | High        | High        | Yes                                  | Yes                                 | Yes (First-hand)           |

TABLE I COMPARISON BETWEEN DIFFERENT MTJ MODELS

with circuit simulations. But they are flawed with low flexibility and scalability, which limit their use in simulating a large STT-MRAM array with different device configurations. Macro MTJ models have a good balance and provide medium performance at many aspects; but the inbuit circuit elements increase dramatically and simulation overheads are very high when simulating a large STT-MRAM array. Behavioral MTJ models are considered as new circuit elements and provide better flexibility and scalability than macromodels.

MFA-MTJ model owns the advantages of traditional behavioral models. In addition, it has the following new features.

- 1) Magnetic/Electrical Co-Simulation of MTJ/CMOS Circuits: Since the performance of MTJ devices is very sensitive to magnetic fields, this feature is crucial for spintronic circuit design; this work is the first introducing this feature in the EDA community.

- 2) Device Defect Injection and Fault Analysis: MTJ devices require unique manufacturing steps and are subject to new defects and failure mechanisms [19]. Thus, this new feature enables a device-aware test [46] to analyze realistic fault models and to develop high-quality yet cost-efficient tests for STT-MRAMs.

- 3) Comprehensive Silicon Data Validation: We have validated our MTJ model, including the magnetic field module in this work, resistance modules [14], switching modules [6], and defect modules [33], using first-hand silicon data collected at IMEC.

#### B. Magnetic Fields From Current-Carrying Metal Lines

As we emphasize many times in this article, the performance of STT-MRAM is very sensitive to any sources of magnetic fields. Thus, we have taken into account internal stray fields and external disturbance fields and studied their impact on the STT-MRAM performance in this work. For future work on this topic, it is crucial to analyze, model, and evaluate the magnetic fields generated by current-carrying metal lines, such as the BL, SL, and WL. The impact of the fields from these metal lines are strongly dependent on specific STT-MRAM cell designs (e.g., physical cell structure and cell layout). In [47], TSMC presents the vertical STT-MRAM cell structure with logic compatible metal layers; it shows that the BL is located at M5 and M6, right on top of MTJ devices, which sit above M4. In contrast, WL and SL are located at different metal layers, which are slightly farther from MTJ devices; this indicates that the magnetic fields from WL and SL lines probably have no or marginal impact on STT-MRAM devices. Similarly, Intel revealed their STT-MRAM cell layout in [48], which also suggests that BLs are very close to STT-MRAM cells; thus, the magnetic fields from BLs might need to be considered.

In summary, magnetic fields from current-carrying metal lines and their impact on STT-MRAM performance can be very interesting to study in future work; the design constraints in terms of magnetic coupling also need to be determined when design STT-MRAMs.

#### C. Model Usage and Limitations

The proposed MFA-MTJ model can be used for spintronic circuit design and validation, especially for STT-MRAMs. Although we demonstrated the usage of this model for circuit simulations and analysis of a single STT-MRAM device and  $3 \times 3$  STT-MRAM full circuits in this article, we can also instantiate more cells to scale up to a large memory array. The simulation of a single cell takes 415 ms, and a  $3 \times 3$  array takes 823 ms and a  $16 \times 16$  array takes 1.7 s. Note that the simulation time varies with the simulation configurations, such as the time step of transient simulation, switching stochasticity options, and defect injection. To facilitate circuit simulations and analyses, we have wrapped the circuit netlist with a highlevel controller written in Python3; configuration parameters are passed from the end users to the Python controller, which creates the desired netlist, controls the simulation process, and analyzes the measured data. Therefore, the simulation platform is quite user friendly; the end users only need to learn what simulation parameters and what simulation analyses the Python controller provides. The simulation parameters are all independent and can be easily configured.

We also provide Python code to run the simulations in a Cluster to speed up the simulation process by exploiting task-level parallelism. We observed that Monte Carlo (MC) simulations are very time consuming. For example, a 10-cycle MC simulation of the  $3 \times 3$  array takes 5.7 s, 100 cycles take 55.6 s, 1k cycles take 537 s, and 10k cycles take  $\sim$ 23 min. The simulation time becomes prohibitive if we would like to sweep several key parameters (e.g.,  $t_p$  and  $V_{WL}$  in Fig. 12). Therefore, we provide another Python controller version, which distributes parallel simulation tasks onto different compute nodes in a cluster. Our experiments show that running our Spectre circuit simulations (MC + parameter sweep) on the cluster in our department with eight compute nodes provides ~100× speedup. Still, the excessive amount of computation resources and time is a big barrier for the study of design space considering different variation sources. To further speed up such circuit simulations, the worst case corner method [35] can be a good alternative to the MC simulation method.

#### IX. CONCLUSION

In this article, we have proposed a magnetic-field-aware compact model of pMTJ, named as MFA-MTJ model. This model has been implemented in Verilog-A and calibrated with silicon data. It features high configurability and awareness of internal intra and intercell stray fields and external disturbance fields. Based on the MFA-MTJ model, magnetic/electrical cosimulations of STT-MRAM designs have been demonstrated. This model also enables us to explore STT-MRAM design space under PVT variations and various configurations of magnetic fields.

#### REFERENCES

- [1] V. B. Naik et al., "Manufacturable 22nm FD-SOI embedded MRAM technology for industrial-grade MCU and IOT applications," in Proc. Int. Electron Devices Meeting, 2019, pp. 2.3.1–2.3.4, doi: 10.1109/IEDM19573.2019.8993454.

- [2] S. Ikegawa, F. B. Mancoff, J. Janesky, and S. Aggarwal, "Magnetoresistive random access memory: Present and future," *IEEE Trans. Electron Devices*, vol. 67, no. 4, pp. 1407–1419, Apr. 2020, doi: 10.1109/TED.2020.2965403.

- [3] S.-W. Chung et al., "4Gbit density STT-MRAM using perpendicular MTJ realized with compact cell structure," in Proc. Int. Electron Devices Meeting, 2016, pp. 2.3.1–2.3.4, doi: 10.1109/IEDM.2016.7838490.

- [4] K. Lee et al., "1Gbit high density embedded STT-MRAM in 28nm FDSOI technology," in Proc. Int. Electron Devices Meeting, 2019, pp. 2.2.1–2.2.4, doi: 10.1109/IEDM19573.2019.8993551.

- [5] W. J. Gallagher et al., "22nm STT-MRAM for reflow and automotive uses with high yield, reliability, and magnetic immunity and with performance and shielding options," in Proc. Int. Electron Devices Meeting, 2019, pp. 2.7.1–2.7.4, doi: 10.1109/IEDM19573.2019.8993469.

- [6] L. Wu et al., "Defect and fault modeling framework for STT-MRAM testing," *IEEE Trans. Emerg. Topics Comput.*, vol. 9, no. 2, pp. 707–723, Apr.-Jun. 2021, doi: 10.1109/TETC.2019.2960375.

- [7] H. Lim, S. Lee, and H. Shin, "A survey on the modeling of magnetic tunnel junctions for circuit simulation," *Act. Passive Electron. Compon.*, vol. 2016, pp. 1–12, May 2016, doi: 10.1155/2016/3858621.

- [8] M. Frankowski, M. Czapkiewicz, W. Skowroński, and T. Stobiecki, "Micromagnetic model for studies on magnetic tunnel junction switching dynamics, including local current density," *Physica B Condensed Matter*, vol. 435, pp. 105–108, Feb. 2014, doi: 10.1016/j.physb.2013.08.051.

- [9] F. O. Heinz and L. Smith, "Fast simulation of spin transfer torque devices in a general purpose TCAD device simulator," in *Proc. Int. Conf. Simulat. Semicond. Process. Devices*, 2013, pp. 127–130, doi: 10.1109/SISPAD.2013.6650591.

- [10] G. D. Panagopoulos, C. Augustine, and K. Roy, "Physics-based SPICE-compatible compact model for simulating hybrid MTJ/CMOS circuits," *IEEE Trans. Electron Devices*, vol. 60, no. 9, pp. 2808–2814, Sep. 2013, doi: 10.1109/TED.2013.2275082.

- [11] Y. Zhang et al., "Compact modeling of perpendicularanisotropy CoFeB/MgO magnetic tunnel junctions," *IEEE Trans. Electron Devices*, vol. 59, no. 3, pp. 819–826, Mar. 2012, doi: 10.1109/TED.2011.2178416.

- [12] Y. Wang, H. Cai, L. Naviner, Y. Zhang, J.-O. Klein, and W. S. Zhao, "Compact thermal modeling of spin transfer torque magnetic tunnel junction," *Microelectron. Rel.*, vol. 55, nos. 9–10, pp. 1649–1653, 2015, doi: 10.1016/j.microrel.2015.06.029.

- [13] R. De Rose et al., "A compact model with spin-polarization asymmetry for nanoscaled perpendicular MTJs," IEEE Trans. Electron Devices, vol. 64, no. 10, pp. 4346–4353, Oct. 2017, doi: 10.1109/TED.2017.2734967.

- [14] L. Wu et al., "Pinhole defect characterization and fault modeling for STT-MRAM testing," in Proc. Eur. Test Symp., 2019, pp. 1–6, doi: 10.1109/ETS.2019.8791518.

- [15] Y. Wang et al., "Compact model of dielectric breakdown in spin-transfer torque magnetic tunnel junction," *IEEE Trans. Electron Devices*, vol. 63, no. 4, pp. 1762–1767, Apr. 2016, doi: 10.1109/TED.2016.2533438.

[16] C.-Y. Wang et al., "Impact of external magnetic field on embed-

- [16] C.-Y. Wang et al., "Impact of external magnetic field on embedded perpendicular STT-MRAM technology qualified for solder reflow," in *Proc. Int. Electron Devices Meeting*, 2017, pp. 21.1.1–21.1.4, doi: 10.1109/IEDM.2017.8268432.

- [17] L. Wu, S. Rao, M. Taouil, E. J. Marinissen, G. S. Kar, and S. Hamdioui, "Impact of magnetic coupling and density on STT-MRAM performance," in *Proc. Design Autom. Test Europe Conf.*, 2020, pp. 1211–1216, doi: 10.23919/DATE48585.2020.9116444.

- [18] A. V. Khvalkovskiy et al., "Basic principles of STT-MRAM cell operation in memory arrays," J. Phys. D Appl. Phys, vol. 46, no. 7, 2013, Art. no. 074001, doi: 10.1088/0022-3727/46/13/139601.

- [19] L. Wu, M. Taouil, S. Rao, E. J. Marinissen, and S. Hamdioui, "Electrical modeling of STT-MRAM defects," in *Proc. Int. Test Conf.*, 2018, pp. 1–10, doi: 10.1109/TEST.2018.8624749.

- [20] A. Jog et al., "Cache revive: Architecting volatile STT-RAM caches for enhanced performance in CMPs," in *Proc. Design Autom. Conf.*, 2012, pp. 243–252, doi: 10.1145/2228360.2228406.

- [21] Y.-H. Wang et al., "Impact of stray field on the switching properties of perpendicular MTJ for scaled MRAM," in Proc. Int. Electron Devices Meeting, 2012, pp. 29.2.1–29.2.4, doi: 10.1109/IEDM.2012.6479127.

- [22] X. Fong, Y. Kim, R. Venkatesan, S. H. Choday, A. Raghunathan, and K. Roy, "Spin-transfer torque memories: Devices, circuits, and systems," *Proc. IEEE*, vol. 104, no. 7, pp. 1449–1488, Jul. 2016, doi: 10.1109/JPROC.2016.2521712.

- [23] H. Jiancheng, S. C. Hin, V. B. Naik, M. Tran, L. S. Ter, and H. Guchang, "Effect of the stray field profile on the switching characteristics of the free layer in a perpendicular magnetic tunnel junction," *J. Appl. Phys.*, vol. 117, no. 17, 2015, Art. no. 17B721, doi: 10.1063/1.4916037.

- [24] G. Han et al., "Control of offset field and pinning stability in perpendicular magnetic tunnelling junctions with synthetic antiferromagnetic coupling multilayer," J. Appl. Phys., vol. 117, no. 17, 2015, Art. no. 17B515, doi: 10.1063/1.4913942.

- [25] C. Augustine, A. Raychowdhury, D. Somasekhar, J. Tschanz, K. Roy, and V. K. De, "Numerical analysis of typical STT-MTJ stacks for 1T-1R memory arrays," in *Proc. Int. Electron Devices Meeting*, 2010, pp. 22.7.1–22.7.4, doi: 10.1109/IEDM.2010.5703416.

- [26] K. Lee et al., "22-nm FD-SOI embedded MRAM with full solder reflow compatibility and enhanced magnetic immunity," in Proc. IEEE Symp. VLSI Technol., 2018, pp. 183–184, doi: 10.1109/VLSIT.2018.8510655.

- [27] Y. C. Wu et al., "Impact of operating temperature on the electrical and magnetic properties of the bottom-pinned perpendicular magnetic tunnel junctions," Appl. Phys. Lett., vol. 113, no. 14, 2018, Art. no. 142405, doi: 10.1063/1.5042028.

- [28] W. Zhao, J. Duval, J.-O. Klein, and C. Chappert, "A compact model for magnetic tunnel junction (MTJ) switched by thermally assisted spin transfer torque (TAS + STT)," *Nanoscale Res. Lett.*, vol. 6, pp. 1–4, Apr. 2011, doi: 10.1186/1556-276X-6-368.

- [29] A. Vatankhahghadim, "Modelling and circuit design for STT-MRAM," Ph.D. dissertation, Elect. Comput. Eng., Univ. Toronto, Toronto, ON, Canada, 2015.

- [30] L. Thomas et al., "Perpendicular spin transfer torque magnetic random access memories with high spin torque efficiency and thermal stability for embedded applications," J. Appl. Phys., vol. 115, no. 17, 2014, Art. no. 172615, doi: 10.1063/1.4870917.

- [31] D. C. Worledge et al., "Spin torque switching of perpendicular Ta/CoFeB/MgO-based magnetic tunnel junctions," Appl. Phys. Lett, vol. 98, no. 2, pp. 93–96, 2011, doi: 10.1063/1.3536482.

- [32] Y. Zhang, X. Wang, Y. Li, A. K. Jones, and Y. Chen, "Asymmetry of MTJ switching and its implication to STT-RAM designs," in *Proc. Design Autom. Test Europe Conf.*, 2012, pp. 1313–1318, doi: 10.1109/DATE.2012.6176695.

- [33] L. Wu, S. Rao, M. Taouil, E. J. Marinissen, G. S. Kar, and S. Hamdioui, "Characterization, modeling and test of synthetic anti-ferromagnet flip defect in STT-MRAMs," in *Proc. Int. Test Conf.*, 2020, pp. 1–10, doi: 10.1109/ITC44778.2020.9325258.

- [34] W. F. Brinkman, R. C. Dynes, and J. M. Rowell, "Tunneling conductance of asymmetrical barriers," *J. Appl. Phys.*, vol. 41, no. 5, pp. 1915–1921, 1970, doi: 10.1063/1.1659141.

- [35] Y. Wang, "Reliability analysis of spintronic device based logic and memory circuits," Ph.D. dissertation, Télécom ParisTech, Universitt'e Paris-Saclay, Paris, France, 2017.

- [36] M. Wang et al., "Current-induced magnetization switching in atom-thick tungsten engineered perpendicular magnetic tunnel junctions with large tunnel magnetoresistance," Nat. Commun., vol. 9, pp. 1–7, Feb. 2018, doi: 10.1038/s41467-018-03140-z.

- [37] V. Drewello, J. Schmalhorst, A. Thomas, and G. Reiss, "Evidence for strong magnon contribution to the TMR temperature dependence in MgO based tunnel junctions," *Phys. Rev. B*, vol. 77, Jan. 2008, Art. no. 014440, doi: 10.1103/PhysRevB.77.014440.

- [38] J. G. Alzate *et al.*, "Temperature dependence of the voltage-controlled perpendicular anisotropy in nanoscale MgO|CoFeB|Ta magnetic tunnel junctions," *Appl. Phys. Lett.*, vol. 104, no. 11, 2014, Art. no. 112410, doi: 10.1063/1.4869152.

- [39] L.-B. Faber, W. Zhao, J.-O. Klein, T. Devolder, and C. Chappert, "Dynamic compact model of spin-transfer torque based magnetic tunnel junction (MTJ)," in *Proc. Int. Conf. Design Tech. Integr. Syst. Nanoscale Era*, 2009, pp. 130–135, doi: 10.1109/DTIS.2009.4938040.

- [40] L. Wu, M. Taouil, S. Rao, E. J. Marinissen, and S. Hamdioui, "Survey on STT-MRAM testing: Failure mechanisms, fault models, and tests," pp. 1–24, 2020, arXiv:2001.05463.

- [41] L. Wu, S. Rao, M. Taouil, E. J. Marinissen, G. S. Kar, and S. Hamdioui:, "Characterization and fault modeling of intermediate state defects in STT-MRAM," in *Proc. Design, Autom. Test Europe Conf.*, 2021, pp. 1717–1722, doi: 10.23919/DATE51398.2021.9473999.

- [42] C. Yoshida et al., "Demonstration of zero-offset-field operation for top-pinned MTJ with synthetic antiferromagnetic free layer," in Proc. Int. Electron Devices Meeting, 2013, pp. 3.4.1–3.4.4, doi: 10.1109/IEDM.2013.6724552.

- [43] C. Park et al., "Low RA magnetic tunnel junction arrays in conjunction with low switching current and high breakdown voltage for STT-MRAM at 10 nm and beyond," in *Proc. Symp. VLSI Technol.*, 2018, pp. 185–186, doi: 10.1109/VLSIT.2018.8510653.

- [44] G. Hu *et al.*, "Spin-transfer torque MRAM with reliable 2 ns writing for last level cache applications," in *Proc. Int. Electron Devices Meeting*, 2019, pp. 2.6.1–2.6.4, doi: 10.1109/IEDM19573.2019.8993604.

- [45] X. Zhang et al., "Skyrmions in magnetic tunnel junctions," ACS Appl. Mater. Interfaces, vol. 10, pp. 16887–16892, Apr. 2018, doi: 10.1021/acsami.8b03812.

- [46] M. Fieback et al., "Device-aware test: A new test approach towards DPPB," in Proc. IEEE Int. Test Conf., Nov. 2019, pp. 1–10, doi: 10.1109/ITC44170.2019.9000134.

- [47] Y.-C. Shih et al., "A reflow-capable, embedded 8Mb STT-MRAM macro with 9ns read access time in 16nm FinFET logic CMOS process," in Proc. Int. Electron Devices Meeting, 2020, pp. 11.4.1–11.4.4, doi: 10.1109/IEDM13553.2020.9372115.

- [48] O. Golonzka et al., "MRAM as embedded non-volatile memory solution for 22FFL FinFET technology," in *Proc. Int. Electron Devices Meeting*, 2018, pp. 18.1.1–18.1.4, doi: 10.1109/IEDM.2018.8614620.