Delft University of Technology

# A 121.4-dB DR Capacitively Coupled Chopper Class-D Audio Amplifier

Zhang, Huajun; Berkhout, Marco; Makinwa, Kofi A.A.; Fan, Qinwen

DOI 10.1109/JSSC.2022.3207907

Publication date 2022 **Document Version** Final published version

Published in IEEE Journal of Solid-State Circuits

# Citation (APA)

Zhang, H., Berkhout, M., Makinwa, K. A. A., & Fan, Q. (2022). A 121.4-dB DR Capacitively Coupled Chopper Class-D Audio Amplifier. *IEEE Journal of Solid-State Circuits*, *57*(12), 3736-3745. https://doi.org/10.1109/JSSC.2022.3207907

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

# 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A 121.4-dB DR Capacitively Coupled Chopper Class-D Audio Amplifier

Huajun Zhang<sup>®</sup>, *Graduate Student Member, IEEE*, Marco Berkhout<sup>®</sup>, *Member, IEEE*, Kofi A. A. Makinwa<sup>®</sup>, *Fellow, IEEE*, and Qinwen Fan, *Member, IEEE*

Abstract—This article presents a class-D amplifier (CDA) with high dynamic range (DR). To eliminate the typically dominant noise contribution of a resistive feedback network, the input and feedback signals are chopped and applied to a capacitive feedback network. However, this leads to high-voltage (HV) transients at the input of the loop filter, which, due to timing and impedance mismatch in the chopped feedback network, could degrade linearity and even overstress low-voltage (LV) core devices. Robust processing of the HV chopped feedback signal is guaranteed with chopper timing skew correction, chopper impedance matching, and deadbanding. The prototype, implemented in a 180-nm bipolar-CMOS-DMOS (BCD) process, achieves 121.4 dB of DR, 5.9 dB higher than state-of-the-art closed-loop CDAs, and  $8-\mu V_{RMS}$  output-referred noise (A-weighted). It also achieves a peak total harmonic distortion (THD) + N of -109.8 dB and a peak efficiency of 93%/88% while driving 15 W/26 W into an 8-/4- $\Omega$  load.

*Index Terms*—Audio power amplifier, capacitively coupled chopper amplifier, class-D amplifier (CDA), dynamic range (DR), noise.

# I. INTRODUCTION

**C**LASS-D amplifiers' (CDAs) ability to achieve high power efficiency has led to their wide adoption in audio applications. In high-end applications, audio digital-to-analog converters (DACs) with a dynamic range (DR) of above 130 dB are commercially available [1], [2], [3], [4], matching that of the human ear. However, the DR of typical monolithic class-D audio amplifiers is much lower, only around 110 dB for analog-input designs [5], [6], [7], [8], [9], [10] and up to about 115 dB for digital-input designs [11], [12], [13], [14].

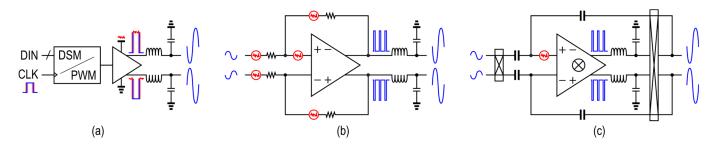

In [15], a CDA with 120 dB of DR is reported. It employs an open-loop architecture, in which a digital input is first deltasigma-modulated and then directly used to control the duty cycle of an output stage. As such, its noise performance is limited by supply noise and clock jitter, as shown in Fig. 1(a). To achieve the reported 120-dB DR, an integrated clock jitter of less than 2 ps (rms) is required [15], which increases

Manuscript received 15 May 2022; revised 26 July 2022 and 12 September 2022; accepted 15 September 2022. Date of publication 30 September 2022; date of current version 28 November 2022. This article was approved by Associate Editor Jens Anders. (*Corresponding author: Qinwen Fan.*)

Huajun Zhang, Kofi A. A. Makinwa, and Qinwen Fan are with the Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS), Department of Microelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: q.fan@tudelft.nl).

Marco Berkhout is with Goodix Technologies, 6537 TL Nijmegen, The Netherlands.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2022.3207907.

Digital Object Identifier 10.1109/JSSC.2022.3207907

the system's cost. The open-loop architecture also leads to significant distortion at high power levels and to poor power supply rejection. In [16], the supply voltage is adaptively reduced at low power levels to reduce jitter sensitivity, while feedback is employed at high power levels to reduce distortion and improve supply rejection. However, the additional dc–dc converter required for supply scaling reduces power efficiency, whereas the amplitude-dependent use of resistive feedback causes significant noise floor modulation.

Most CDAs employ a closed-loop architecture to suppress output stage distortion and improve their immunity to supply noise and clock jitter. In this case, their noise floor is typically limited by the thermal noise generated by the resistors that set the CDA's closed-loop gain (or by the resistive or current DAC in a digital-input architecture) and by the amplifier in the first stage of the loop filter, as shown in Fig. 1(b). The contribution of the latter is usually low since a welldesigned active-RC integrator typically satisfies  $g_m R_{\rm IN} \gg 1$ , where  $R_{IN}$  is the integrator's input resistance and  $g_m$  is the amplifier's transconductance [17]. Furthermore, in addition to the resistor's thermal noise, the amplifier's 1/f noise is also often significant. However, reducing resistor noise is more difficult, as this comes at the expense of reducing the CDA's input impedance and increasing the power consumed in its feedback network, especially for high-voltage (HV) CDAs.

For low-noise closed-loop amplification, the capacitively coupled chopper amplifier is a good choice [18], [19], [20]. Its capacitive feedback network does not contribute any noise, nor does it consume static power. This enables high energy efficiency, making it popular in biomedical and instrumentation applications. The amplifier's 1/f noise is mitigated by chopping, making its thermal noise the dominant contributor [see Fig. 1(c)].

This work presents a capacitively coupled chopper CDA that achieves 121.4-dB DR [21]. Unlike conventional chopper amplifiers, which process small input and output signals [18], [19] or are used in discrete-time switched-capacitor circuits [20], the proposed audio amplifier must process large continuous-time signals at both its low-voltage (LV) input  $(\pm 1.8 \text{ V})$  and HV output  $(\pm 14.4 \text{ V})$ . Since the loop filter of the CDA operates in the LV domain, the HV transients coupled into the loop filter via a capacitive feedback network will degrade loop filter linearity and may even damage thin-oxide core devices. To prevent this, a feedback-after-*LC* architecture is used to remove HV edges in the CDA output, while the timing and impedance of the switches in the chopped feedback

0018-9200 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 1. Major noise sources in different CDA architectures: (a) open-loop, (b) closed-loop with resistive feedback, and (c) proposed closed-loop with capacitive feedback.

Fig. 2. Architecture of the proposed capacitively coupled CDA.

network have been carefully optimized. Residual chopping glitches are blocked by a deadband, so high CDA linearity is maintained.

The rest of this article is organized as follows. Section II introduces the capacitively coupled chopper CDA architecture. Section III describes the circuit implementation and mitigation techniques to overcome HV transients. Section IV presents the measurement results, and Section V concludes this article.

# II. CAPACITIVELY COUPLED CHOPPER CDA Architecture

#### A. Overview

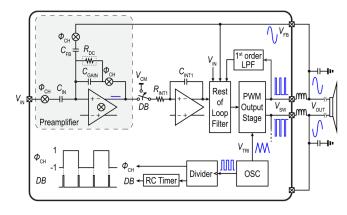

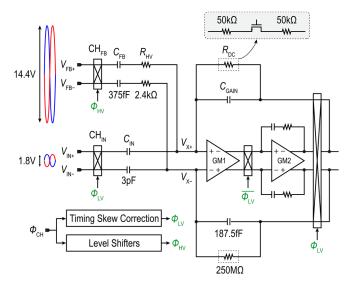

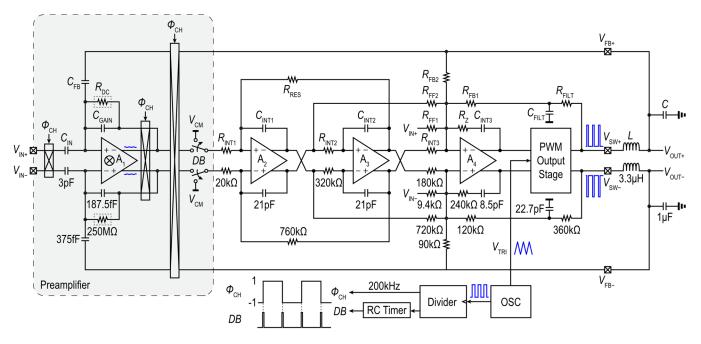

To achieve low noise, this work employs a capacitively coupled preamplifier in the loop filter [22]. Fig. 2 shows an overview of the proposed capacitively coupled chopper CDA. The ratio between the input capacitor  $C_{\rm IN}$  and the global feedback capacitor  $C_{\rm FB}$  sets an overall closed-loop gain of 8. The preamplifier itself has a gain of 16×, which suppresses the noise contribution of the noisy active-*RC* integrators that comprise the succeeding stages of the loop. The output stage employs three-level fixed-frequency pulsewidth modulation (PWM) with a switching frequency  $f_{\rm SW} = 4.2$  MHz and a 14.4-V supply [23].

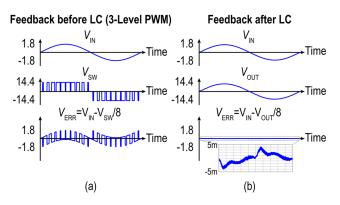

Incorporating the *LC* into the feedback loop [7], [12], [24] is necessary for the proposed capacitive feedback scheme.<sup>1</sup> Since the output stage generates [6], [8], [9], [10], [11]

Fig. 3. Error signal waveform for (a) feedback-before-LC and (b) feedback-after-LC CDAs. The closed-loop gain is 8 with a  $\pm 1.8$ -V differential input swing.

high-frequency switching signals at  $V_{SW}$ , taking feedback from these nodes would result in a residual error signal  $(V_{\rm IN} - V_{\rm OUT}/8)$  that would saturate  $A_1$ , as shown in Fig. 3(a). In contrast, due to the LC filter's suppression of the highfrequency components, the error signal is now in the order of millivolts [see Fig. 3(b)]. To mitigate 1/f noise, the input stage of  $A_1$  is chopped. Beneficially, chopping also allows the use of a much smaller resistance to set the dc bias at  $A_1$ 's virtual ground ( $R_{dc}$  in Fig. 2), which is more robust to leakage, especially under process and temperature variations. This is because the value of  $R_{dc}$  would have to be much larger to push the preamplifier's high-pass corner below 20 Hz, instead of below  $f_{CH}$  in the case of chopping. Furthermore, chopping relaxes the matching constraint on  $C_{\rm FB}$  and  $C_{\rm IN}$ pairs, thereby improving the common-mode rejection of the preamp and, therefore, power supply rejection ratio (PSRR) of the CDA [26].

However, chopping inevitably also introduces nonlinear glitches due to the large-signal nonlinearity of chopper switches and the amplifier, limiting the total harmonic distortion (THD) of conventional capacitively coupled amplifiers (e.g., to -76 dB in [19]). In signal acquisition applications, the subsequent ADC's sampling time can be carefully chosen to avoid the chopping glitches [18], [20]. This is not possible in an audio amplifier. Therefore, a deadband switch is introduced at the output of  $A_1$  to prevent these glitches and the corresponding settling transients of the preamplifier from introducing distortion.

Chopping is performed at  $f_{CH} = 200$  kHz, an odd subharmonic of  $f_{SW}$ , to avoid the chopping-induced intermodulation distortion (IMD) [27] due to PWM sidebands around  $f_{SW}$  [26].

<sup>&</sup>lt;sup>1</sup>The *LC* filter is required anyway for applications with high output power (>10 W) or when the speaker cable is longer than a few tens of centimeters, to suppress the electromagnetic interference (EMI) generated by the CDA's output stage [25].

Fig. 4. Simplified block diagram of the proposed CDA.

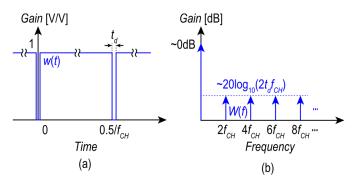

Fig. 5. (a) Time-domain waveform the periodic deadband window w(t) and (b) first few terms of its frequency-domain representation W(f).

A lower chopping frequency would require a lower 1/f corner for  $A_1$ , increasing its input capacitance, and thus its area and power, whereas a higher chopping frequency increases IMD due to PWM sidebands around even multiples of  $f_{SW}$  and the deadband's noise folding gain. These considerations will be analyzed in Section II-B.

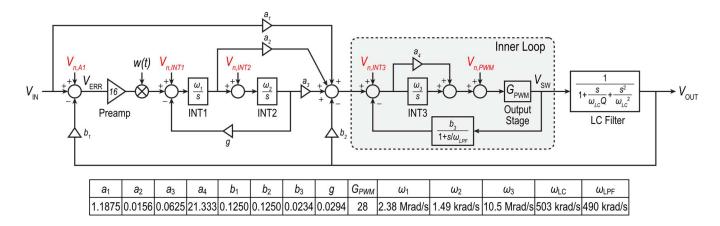

Fig. 4 shows the block diagram corresponding to the proposed CDA. The deadband is modeled as a multiplication by a periodic window w(t). The *LC* filter's 180° phase shift is addressed with a lead compensator, implemented using an inner loop that feeds back the switching node  $V_{SW}$  through a first-order low-pass filter [7]. The outer loop consists of the preamplifier and a resonator, and the latter built with two integrators and local feedback to place their two poles optimally in the audio band for maximal loop gain.

# B. Noise

The main sources of thermal noise in the proposed CDA are also shown in Fig. 4. Due to the  $16 \times$  gain from the preamplifier, audio band noise from later loop filter stages is suppressed by 24 dB, and therefore, the CDA's in-band noise floor is mainly determined by the preamplifier. However, the noise of the later stages is not sufficiently suppressed at high frequencies, and periodic windowing introduced by the deadband partially folds the wideband thermal noise at the preamplifier's output to the audio band. These will be analyzed in the following.

As shown in Fig. 5(a), the deadband window can be expressed as

$$w(t;t_{d},T) \stackrel{\text{def}}{=} \begin{cases} 0, & |t| < \frac{t_{d}}{2} \\ 1, & \frac{t_{d}}{2} \le |t| < \frac{T-t_{d}}{2} \\ w(t-kT), & \text{otherwise} \end{cases}$$

(1)

where  $t_d$  is the deadband's duration, T is its period (equal to  $0.5/f_{\text{CH}}$ ), and k is a nonzero integer. The Fourier transform of w(t) is given by

$$W(f) = \left[\underbrace{\left(1 - \frac{t_d}{T}\right)}_{a_0} + \sum_{\substack{n = -\infty \\ n \neq 0}}^{\infty} - \underbrace{\frac{t_d}{T}\operatorname{sinc}\left(\frac{n\pi t_d}{T}\right)}_{a_n}\right] \delta\left(f - \frac{n}{T}\right)$$

(2)

whose first few terms are sketched in Fig. 5(b).

According to (2), the deadband marginally attenuates inband noise by a factor of  $a_0$  but folds frequency components around even multiples of the chopping frequency with a scaling factor of  $a_n$ , the magnitude of which is largely determined by the duty cycle of the deadband  $(t_d/T)$ .

The wideband thermal noise at the preamplifier output includes noise generated by  $A_1$  and the noise present in the feedback signal. Since  $A_1$  is a wideband gain stage, its output noise at different time instants can be assumed uncorrelated. Therefore, the deadband attenuates its noise by a factor of  $(1 - t_d/T)$ , which can be verified by summing over all noise folding terms

$$V_{n,A_1,\text{fold}}^2 = \sum_{n=-\infty}^{\infty} |a_n|^2 V_{n,A_1}^2 = \frac{1}{T} \int_{-T/2}^{T/2} w^2(t) V_{n,A_1}^2 dt$$

$$= \left(1 - \frac{t_d}{T}\right) V_{n,A_1}^2.$$

(3)

As long as  $t_d \ll T$ , the noise folding changes the noise contribution of  $A_1$  by a negligible amount.

On the other hand, the wideband noise present in the feedback signal includes noise contributed by the later stages of the loop filter and the output stage, shaped by their respective

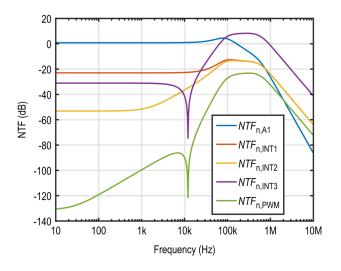

Fig. 6. NTFs (normalized to closed-loop gain) of each noise source highlighted in Fig. 4.

Fig. 7. Simulated noise PSD of the CDA output, with the first two bands subjected to noise folding highlighted.

noise transfer functions (NTFs), which are shown in Fig. 6. Except for that from  $A_1$ , these sources of noise are suppressed in the audio band by the gain of the preceding stages and eventually roll off beyond the unity-gain frequency of the outer loop. However, between 100 kHz and 1 MHz, they appear at the output with much less attenuation.

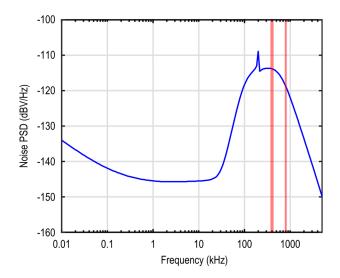

Fig. 7 plots the simulated noise spectral density (NSD) at the output, showing the aforementioned out-of-band noise bump. [The residual 1/f noise is mostly contributed by the feedback chopper, which is implemented with laterally diffused MOSFET (LDMOS) transistors (Section III-A).] The most significant sources of folded noise are around  $2 f_{\rm CH}$  and  $4 f_{\rm CH}$ , i.e., 400 and 800 kHz, respectively. For these two cases

$$|a_n| \approx \frac{t_d}{T}, \quad n = 1, 2. \tag{4}$$

Reducing the out-of-band noise would require increasing the integrator area as in conventional resistive CDAs. To avoid a

Fig. 8. Schematic of the capacitively coupled chopper preamplifier.

Fig. 9. Circuit implementation of amplifier  $A_1$ .

significant noise penalty, the deadband's duty cycle is chosen to be 1% ( $t_d/T = 0.01$ ), thus attenuating the folded noise by 40 dB, corresponding to a deadband duration of 25 ns. The preamplifier is designed to settle sufficiently within this duration. For a higher  $f_{\rm CH}$ , the reduced NSD of alias bands is compromised by the increase in  $|a_n|$ .

In addition, the deadband may also fold back the out-ofband quantization noise of the (typically  $\Delta\Sigma$ ) audio DAC that drives the CDA. If the DAC has a white out-of-band noise spectrum, sampling 10% of the frequency range per octave (400 kHz ± 20 kHz, 800 kHz ± 20 kHz, and so on) will result in the folding down of approximately -10 dB of the out-of-band noise. For a total out-of-band noise in the order of -40 dBFS [28], [29] and given the aforementioned 40-dB attenuation of folded noise by the deadband, the additional filtering required to keep the folded input noise below -130 dBFS is about

$$-40 \text{ dBFS} - 40 \text{ dB} - 10 \text{ dB} - (-130 \text{ dBFS}) = 40 \text{ dB}.$$

This can be achieved by a second-order low-pass filter. Alternatively, quantization noise folding may be avoided by co-designing a DAC to operate at a sampling frequency

Fig. 10. HV chopper (CH\_{FB}) and its switching transient during a chopping transition.

Fig. 11. Schematic of the floating regulator and level shifter [26]. A replica of this circuit is used for timing skew correction.

of  $2 f_{CH}$ , which places the alias bands at the nulls of the DAC's output spectrum [22].

#### **III. CIRCUIT IMPLEMENTATION**

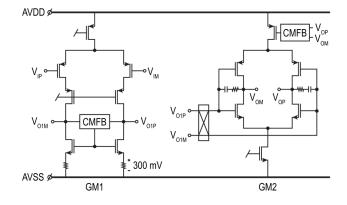

#### A. Capacitively Coupled Chopper Preamplifier

Fig. 8 shows a schematic of the capacitively coupled chopper preamplifier.<sup>2</sup> The input capacitance is chosen to be 3 pF to minimize the attenuation by the parasitic capacitance ( $\sim$ 1 pF) at the summing node  $V_X$  such that the noise performance is not compromised by the reduced feedback factor due to the parasitics. The Monte Carlo simulation indicates a 1- $\sigma$  mismatch of 0.12% for  $C_{\text{FB}}$ . Without chopping, this would limit the typical PSRR to 58 dB.

<sup>2</sup>There was a typo in the callout for  $R_{dc}$  in Fig. 2 of the conference paper [21], which had the resistor in the middle of two nMOS switches. This is corrected in Fig. 8 of this article.

Fig. 12. Chopper clock and virtual ground waveform with (a) no timing skew and impedance compensation, (b) impedance compensation only, (c) timing skew correction only, and (d) both timing skew correction and impedance compensation.

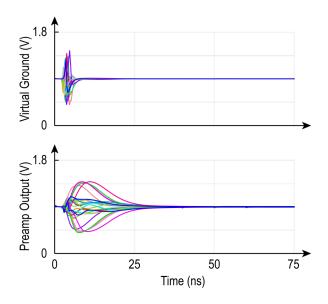

Fig. 13. Transient waveform at the virtual ground and output of the preamplifier during a chopping transition.

The dc bias at  $V_X$  is set by a duty-cycled resistor  $R_{dc}$ implementing an equivalent resistance of 250 M $\Omega$  [22], [30], which ensures a flat gain response around  $f_{CH} \pm 20$  kHz. In a CDA, temperature fluctuations can be significant and signal-dependent due to the thermal dissipation of the output stage. Therefore, a duty-cycled resistor is chosen over a pseudoresistor for its robustness under temperature variations. The periodic switching of this resistor also introduces some noise folding and IMD, but they are insignificant since the duty cycle (~0.04%) is much smaller than the deadband's one.

The preamplifier is built around a two-stage Millercompensated opamp, as shown in Fig. 9. The input stage

Fig. 14. Top-level schematic of the proposed capacitively coupled CDA.

employs a pMOS input pair that achieves a 1/f noise corner of about 50 kHz with an input capacitance of around 1 pF, to keep its 1/f noise contribution below 10%. Its nMOS load is heavily degenerated to reduce its noise contribution.

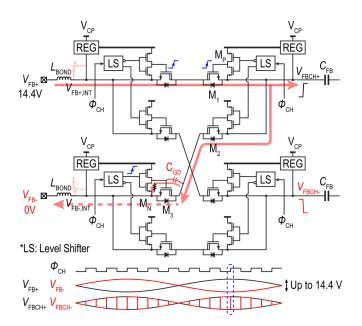

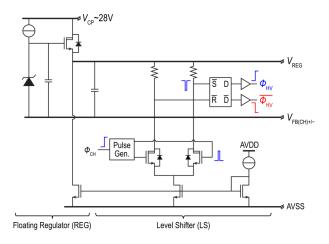

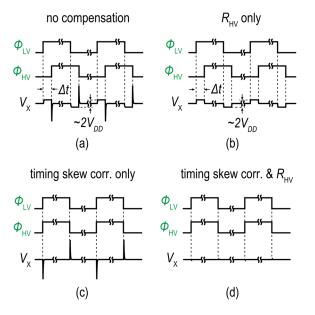

The input chopper (CH<sub>IN</sub>) is implemented with conventional bootstrapped switches for high linearity. The feedback chopper (CH<sub>FB</sub>) is also bootstrapped and employs back-to-back LDMOS switches to handle the output up to 14.4 V [26], as shown in Fig. 10. Level shifters (see Fig. 11) are required to control the switches in the HV chopper, which adds delay and offsets the switching instants of the two choppers. In this capacitively coupled CDA, the timing skew can cause the voltage across the virtual ground to temporarily exceed the supply range by up to two times (ignoring parasitic loading at  $V_X$ ), as shown in Fig. 12(a) and (b). A replica-based timing skew correction circuit is employed to reduce the timing skew from more than 3 ns to be within 200 ps [26].

The ON-resistance mismatch of the two choppers can also cause large transients at  $V_X$ , which is exacerbated by the need to upsize  $CH_{FB}$  to mitigate the large 1/f noise of LDMOS transistors [see Fig. 12(a) and (c)]. The gate length is fixed for n-channel LDMOS transistors in this process, so their width must be increased. According to simulations, an ON-resistance of about 10  $\Omega$  for each set of back-to-back switches is required to keep their total 1/f noise contribution below 10%. This problem is addressed by adding a series resistance  $R_{\rm HV}$  (=2.4 k $\Omega$ ) to match the resistance ratio of the input and feedback paths to the ratio of their capacitive impedance (1:8), assuming low source impedance ( $\ll 300 \Omega$ ) at the CDA input. If a source with higher output impedance is used, two external resistors in series with  $C_{\rm FB}$  can be employed. Some residual mismatch is acceptable as long as the swing of the residual glitches at  $V_X$ , shown in Fig. 12(d),

does not lead to oxide damage, and the resulting transient at the output of  $A_1$  settles before the deadband ends. The deadband, nominally 25 ns long, is generated by an *RC* timer, while the same type of component is used in  $A_1$ 's constant- $g_m$ biasing circuit to ensure settling within the deadband across process, voltage, and temperature (PVT).

In addition, unlike [26], where the HV feedback signal is directly accessible within the chip, the output of this work is fed back from the off-chip LC filter. In simulations, cross conduction through CHFB, even only lasting several hundred picoseconds, can create ringing up to several volts across the parasitic inductance from the bondwire, printed circuit board (PCB) trace, and the LC filter, adding to the glitches at  $V_X$ . The HV chopper transients during a chopping transition are shown in Fig. 10. Cross conduction happens when coupling through  $C_{GD}$  pulls up the gate of a transistor that is supposed to be OFF, e.g., transistor  $M_3$  in Fig. 10. This can happen when  $M_1$  is turned on too quickly by its gate pull-up transistor  $M_P$ , causing the displacement current through  $C_{GD}$  of  $M_3$  to exceed  $V_{\text{TH},M_3}/R_{\text{ON},M_N}$ , where  $R_{\text{ON},M_N}$  is the ON-resistance of the gate pull-down transistor  $M_N$ . Hence, the ratio of the pull-up and pull-down strength of the switch drivers for CHFB is resized to 1/7 in this work such that the switches can be kept OFF during such switching events [31].

Fig. 13 shows the simulated waveform at  $V_X$  and the output of  $A_1$  under process and temperature variations during a chopping event. The swing at  $V_X$  is well within the supply range, while the glitch at the output mostly settles within 25 ns, which is limited by the bandwidth of the preamplifier.

#### B. Class-D Amplifier

As shown in Fig. 14, the rest of the loop filter stages employ an active-*RC* topology for high linearity. The 2.1-MHz triangle wave required for PWM is generated by a differential

Fig. 15. Die photograph.

oscillator. The output stage employs a three-level topology with constant output common mode for low idle power. Amplifiers  $A_2-A_4$  in the loop filter, the differential oscillator, and the output stage are reused from [23].

The triangle wave's peaks and zero crossings are extracted to create a 4.2-MHz digital clock, which is then divided by 21 to generate a 200-kHz clock with a 50% duty cycle for chopping.

#### **IV. MEASUREMENT RESULTS**

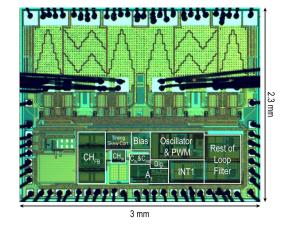

A prototype of the proposed capacitively coupled CDA is implemented in a 180-nm bipolar-CMOS-DMOS (BCD) process. Fig. 15 shows a photograph of the die, which occupies 7 mm<sup>2</sup>. The output stage employs a 14.4-V supply (PVDD), while the rest, including the loop filter, oscillator, and timing, operates from a 1.8-V supply (AVDD). The quiescent current drawn from AVDD is 7 mA, in which the preamplifier draws 1 mA. The HV chopper draws about 1 mA from PVDD. An Audio Precision APx555 Analyzer generates the input and captures the output of the CDA.

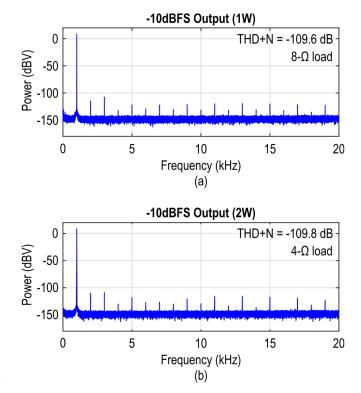

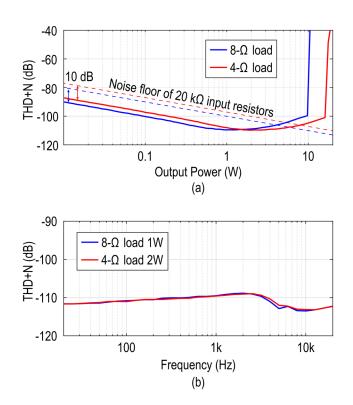

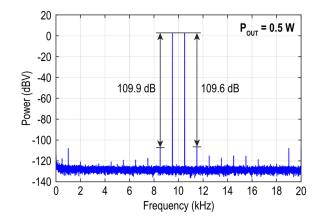

Fig. 16(a) shows the measured output spectrum when the CDA delivers 1 W into an 8- $\Omega$  load, corresponding to -10 dBFS. In this case, the measured THD + N is -109.6 dB. Fig. 16(b) shows the result for a 4- $\Omega$  load at the same output swing, where the THD + N is -109.8 dB.

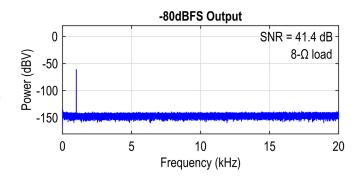

Fig. 17 shows the output spectrum with a -80-dBFS input, where the measured SNR is 41.4 dB, indicating that the prototype achieves a DR of 121.4 dB. The measured A-weighted integrated output noise is 8  $\mu$ V<sub>RMS</sub>.

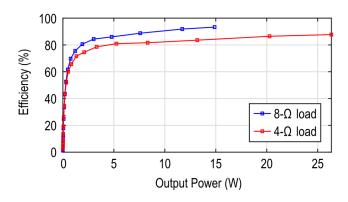

Fig. 18(a) shows the measured THD + N across output power levels with both 8- $\Omega$  load and 4- $\Omega$  load. In both cases, the peak THD + N is about -110 dB. The maximum output power (defined at 10% THD) is 15 and 26 W for 8- and 4- $\Omega$  loads, respectively. The noise floor, which dominates over distortion at small signal amplitudes, is about 10 dB lower than that contributed by a pair of 20-k $\Omega$  resistors, which is common for conventional resistive-feedback CDAs [5], [10]. The THD stays below -100 dB until the point of clipping. Fig. 18(b) plots the measured THD + N across input frequency, which is between -108.8 and -113.5 dB. Fig. 19 shows the spectrum measured from a two-tone test. At an output power

Fig. 16. Measured output spectra at -10~dBFS for (a)  $8\text{-}\Omega$  load and (b)  $4\text{-}\Omega$  load.

Fig. 17. Measured output spectrum at -80 dBFS.

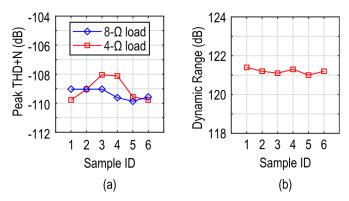

of 0.5 W, the third-order intermodulation distortion (IM3) is about -110 dB. Fig. 20 shows the measured THD + N and DR for six samples. The peak THD + N varies by less than 1 dB for an 8- $\Omega$  load and less than 2 dB for a 4- $\Omega$  load. The DR is within 0.5 dB for all samples.

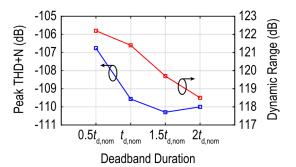

To evaluate the noise folding effect of the deadband, the deadband duration is made programmable. Fig. 21 shows the measured THD + N and DR while varying the deadband duration. When the deadband duration is intentionally reduced, linearity degrades as a portion of the nonlinear chopping glitches propagates down the loop filter. On the other hand, when the deadband is lengthened, the DR degrades due to increased noise folding, as mentioned in Section II-B.

Fig. 22 shows the measured power efficiency. The peak efficiency is 93% and 88% for 8- and 4- $\Omega$  loads, respectively.

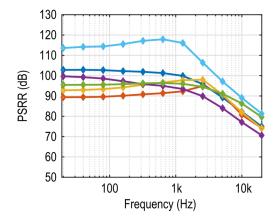

Fig. 23 plots the PSRR measured from six samples. The worst case PSRR is 89 dB at low frequencies. The degraded

|                                         | This Work         | TPA3255<br>[5]       | Sun<br>ISSCC'22<br>[16]  | Zhang<br>JSSC'22<br>[7] | Karmakar<br>JSSC'20<br>[10] | Cope<br>ISSCC'18<br>[11] | Schinkel<br>JSSC'17<br>[12] | Wang<br>JSSC'10<br>[15] |

|-----------------------------------------|-------------------|----------------------|--------------------------|-------------------------|-----------------------------|--------------------------|-----------------------------|-------------------------|

| Process                                 | 180 nm<br>BCD     | -                    | 0.5 μm<br>CMOS           | 180 nm<br>BCD           | 180 nm<br>BCD               | 180 nm<br>BCD            | 130 nm<br>BCD               | 65 nm<br>CMOS           |

| Architecture                            | Analog-In         | Analog-In            | Digital-In               | Analog-In               | Analog-In                   | Digital-In               | Digital-In                  | Digital-In              |

| Feedback Network                        | Capacitive        | Resistive            | Resistive <sup>(1)</sup> | Resistive               | Resistive                   | Resistive                | Resistive                   | N.A.                    |

| Supply (V)                              | 14.4              | 51                   | 0.625~5                  | 14.4                    | 14.4                        | 8~20                     | 14/25                       | 3                       |

| R <sub>LOAD</sub> (Ω)                   | 8/4               | 4                    | 8                        | 8/4                     | 4                           | 8                        | 4                           | 8                       |

| P <sub>OUT,MAX</sub> (W)                | 15/26             | 315                  | 1.5                      | 12/21                   | 28                          | 20                       | 80                          | 0.4                     |

| Efficiency                              | 93%/88%           | - 90% <sup>(2)</sup> | 81                       | 91%/87%                 | 91%                         | 90%                      | >90%                        | 88                      |

| I <sub>Q,PVDD</sub> / Channel (mA)      | 9                 | 24                   | 2.4                      | 8                       | 17                          | 21                       | -                           | 2.4                     |

| I <sub>Q,AVDD</sub> / Channel (mA)      | 7                 | 30                   | -                        | -                       | -                           | -                        | -                           | -                       |

| THD+N (dB)                              | -109.6/-109.8     | -84                  | -95.4                    | -107.1/-105.6           | -102.2                      | -97.7                    | -88.6                       | -94(2)                  |

| DR                                      | 121.4             | 113                  | 121                      | 110 <sup>(3)</sup>      | 109                         | 115.5                    | 115                         | 120                     |

| A-wt. Output Noise (µV <sub>RMS</sub> ) | 8                 | 85                   | 3.15                     | -                       | 31                          | 20                       | 19/34                       | 1.7                     |

| PSRR (dB)<br>(Frequency/Hz)             | 89~71<br>(20~20k) | >65 dB<br>-          | 100<br>(217)             | -                       | 70~62<br>(20~20k)           | 80~50<br>(20~20k)        | 90~60**<br>(20~20k)         | 82<br>(1k)              |

TABLE I Performance Summary and Comparison

<sup>(1)</sup> Feedback only enabled at high output power

(2) Estimated from graph

(3) SNR number used

Fig. 18. Measured THD+N across (a) output power and (b) input frequency.

PSRR compared to [26] was traced to the mismatch of the near-minimum-width resistor pair  $R_{FB2}$  (see Fig. 14). Supply noise thus leaks into the differential signal present at the input of the third integrator, which, in this design, is only suppressed by about 30 dB, as shown in Fig. 6.

Table I summarizes the prototype's performance and compares it with state-of-the-art CDAs, including both

Fig. 19. Measured spectrum from a two-tone test.

Fig. 20. (a) THD + N and (b) DR for six samples.

analog- and digital-input ones. Due to the capacitively coupled architecture, this work achieves 5.9-dB higher DR,  $2.4 \times$  lower A-weighted integrated output noise, and 2.5-dB better peak

Fig. 21. Peak THD + N (left axis) and DR (right axis) for different deadband settings.

Fig. 22. Measured power efficiency across output power.

Fig. 23. Measured PSRR across the audio band of six samples.

THD + N. Meanwhile, it achieves competitive efficiency, idle power, and PSRR among HV (>10 V) CDAs.

#### V. CONCLUSION

In conclusion, a capacitively coupled chopper Class-D audio amplifier is presented, which enables significant improvement in the DR. To protect thin-oxide devices, HV chopping transients are addressed through timing and impedance matching. Deadbanding is applied to suppress the residual glitches and maintain high linearity. Due to the low-noise capacitively coupled chopper preamplifier in the loop filter, the 180-nm prototype achieves 8  $\mu V_{RMS}$  of A-weighted integrated noise and 121.4-dB DR.

#### REFERENCES

- AKM. AK4377 High Sound Quality Advanced 32-Bit Stereo DAC With HP Amp. Accessed: Apr. 10, 2022. [Online]. Available: https://www.akm.com/eu/en/products/audio/audio-dac/ak4377ecb/

- [2] ESS. ES9038PRO Flagship 32-Bit HyperStream II 8-Channel Audio DAC. Accessed: Apr. 10, 2022. [Online]. Available: https://www.esstech. com/wp-content/uploads/2021/03/ES9038PRO-Datasheet-v3.7.pdf

- [3] C. Logic. CS43131 130 dB, 32-Bit High-Performance DAC With Integrated Headphone Driver and Impedance Detection. Accessed: Apr. 10, 2022. [Online]. Available: https://statics.cirrus.com/pubs/ proDatasheet/CS43131\_F1.pdf

- [4] Texas Instruments. PCM1794A 24-Bit, 192-kHz Sampling, Advanced Segment, Audio Stereo Digital-to-Analog Converter. Accessed: Apr. 10, 2022. [Online]. Available: https://www.ti.com/ product/PCM1794A

- Texas Instruments. TPA3255-Q1 315-W Stereo, 600-W Mono PurePath Ultra-HD Analog-Input. Accessed: Apr. 10, 2022. [Online]. Available: https://www.ti.com/lit/gpn/tpa3255-q1

- [6] E. Gaalaas, B. Y. Liu, N. Nishimura, R. Adams, and K. Sweetland, "Integrated stereo ΔΣ class D amplifier," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2388–2397, Dec. 2005.

- [7] H. Zhang, M. Berkhout, K. A. A. Makinwa, and Q. Fan, "A –121.5-dB THD class-D audio amplifier with 49-dB *LC* filter nonlinearity suppression," *IEEE J. Solid-State Circuits*, vol. 57, no. 4, pp. 1153–1161, Apr. 2022.

- [8] M. Høyerby, "A 2×70 W monolithic five-level class-D audio power amplifier in 180 nm BCD," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 2819–2829, Dec. 2016.

- [9] W. Wang and Y. Lin, "A 0.0004% (-108 dB) THD+N, 112dB-SNR, 3.15 W fully differential class-D audio amplifier with Gm noise cancellation and negative output-common-mode injection techniques," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 58–60.

- [10] S. Karmakar et al., "A 28-W, -102.2-dB THD+N class-D amplifier using a hybrid ΔΣM-PWM scheme," *IEEE J. Solid-State Circuits*, vol. 55, no. 12, pp. 3146–3156, Dec. 2020.

- [11] E. Cope et al., "A 2×20W 0.0013% THD+N class-D audio amplifier with consistent performance up to maximum power level," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 56–58.

- [12] D. Schinkel *et al.*, "A multiphase class-D automotive audio amplifier with integrated low-latency ADCs for digitized feedback after the output filter," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3181–3193, Dec. 2017.

- [13] A. Matamura et al., "An 82-mW ΔΣ-based filter-less class-D headphone amplifier with -93-dB THD+N, 113-dB SNR, and 93% efficiency," *IEEE J. Solid-State Circuits*, vol. 56, no. 12, pp. 3573–3582, Dec. 2021.

- [14] T. Ido, S. Ishizuka, L. Risbo, F. Aoyagi, and T. Hamasaki, "A digital input controller for audio class-D amplifiers with 100W 0.004% THD+N and 113 dB DR," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2006, pp. 1366–1375.

- [15] M. Wang, X. Jiang, J. Song, and T. L. Brooks, "A 120 dB dynamic range 400 mW class-D speaker driver with fourth-order PWM modulator," *IEEE J. Solid-State Circuits*, vol. 45, no. 8, pp. 1427–1435, Aug. 2010.

- [16] W. H. Sun, S. H. Chien, and T. H. Kuo, "A 121 dB DR, 0.0017% THD+N, 8× jitter-effect reduction digital-input class-D audio amplifier with supply-voltage-scaling volume control and series-connected DSM," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 65, Feb. 2022, pp. 486–488.

- [17] S. Pavan, R. Schreier, and G. C. Temes, "Circuit design for continuoustime delta-sigma modulators," in *Understanding Delta-Sigma Data Converters*. Piscataway, NJ, USA: IEEE Press, 2017, p. 304.

- [18] Q. Fan, F. Sebastiano, J. H. Huijsing, and K. A. A. Makinwa, "A 1.8 μ W 60 nV/√ Hz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1534–1543, Jul. 2011.

- [19] H. Chandrakumar and D. Marković, "An 80-mVpp linear-input range, 1.6-GΩ input impedance, low-power chopper amplifier for closed-loop neural recording that is tolerant to 650-mVpp common-mode interference," *IEEE J. Solid-State Circuits*, vol. 52, no. 11, pp. 2811–2828, Nov. 2017.

- [20] H. Wang, G. Mora-Puchalt, C. Lyden, R. Maurino, and C. Birk, "A 19 nV/ √ Hz noise 2-µV offset 75-µA capacitive-gain amplifier with switched-capacitor ADC driving capability," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3194–3203, Dec. 2017.

- [21] H. Zhang, M. Berkhout, K. A. A. Makinwa, and Q. Fan, "A 121.4 dB DR, -109.8 dB THD+N capacitively-coupled chopper class-D audio amplifier," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 65, Feb. 2022, pp. 484–485.

- [22] H. Chandrakumar and D. Marković, "A 15.2-ENOB 5-kHz BW 4.5-μ W chopped CT ΔΣ-ADC for artifact-tolerant neural recording front ends," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3470–3483, Dec. 2018.

- [23] H. Zhang et al., "A high-linearity and low-EMI multilevel class-D amplifier," *IEEE J. Solid-State Circuits*, vol. 56, no. 4, pp. 1176–1185, Apr. 2021.

- [24] P. Adduci, E. Botti, E. Dallago, and G. Venchi, "Switching power audio amplifiers with high immunity to the demodulation filter effects," J. AES, vol. 60, no. 12, pp. 1015–1023, Dec. 2012.

- [25] Texas Instruments. Application Report SLOA119B Class-D LC Filter Design. Accessed: Jul. 11, 2022. [Online]. Available: https://www.ti.com.cn/cn/lit/pdf/sloa119

- [26] H. Zhang, N. N. M. Rozsa, M. Berkhout, and Q. Fan, "A chopper class-D amplifier for PSRR improvement over the entire audio band," *IEEE J. Solid-State Circuits*, vol. 57, no. 7, pp. 2035–2044, Jul. 2022.

- [27] T. Rooijers, S. Karmakar, Y. Kusuda, J. H. Huijsing, and K. A. A. Makinwa, "A fill-in technique for robust IMD suppression in chopper amplifiers," *IEEE J. Solid-State Circuits*, vol. 56, no. 12, pp. 3583–3592, Dec. 2021.

- [28] V. Colonna, M. Annovazzi, G. Boarin, G. Gandolfi, F. Stefani, and A. Baschirotto, "A 0.22-mm<sup>2</sup> 7.25-mW per-channel audio stereo-DAC with 97-dB DR and 39-dB SNR<sub>out</sub>," *IEEE J. Solid-State Circuits*, vol. 40, no. 7, pp. 1491–1498, Jul. 2005.

- [29] K. Nguyen, A. Bandyopadhyay, B. Adams, K. Sweetland, and P. Baginski, "A 108 dB SNR, 1.1 mW oversampling audio DAC with a three-level DEM technique," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2592–2600, Dec. 2008.

- [30] H. Jiang, S. Nihtianov, and K. A. A. Makinwa, "An energy-efficient 3.7-nV/ √ Hz bridge readout IC with a stable bridge offset compensation scheme," *IEEE J. Solid-State Circuits*, vol. 54, no. 3, pp. 856–864, Mar. 2019.

- [31] M. Berkhout, "A class D output stage with zero dead time," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2003, pp. 134–135.

**Marco Berkhout** (Member, IEEE) received the M.Sc. degree in electrical engineering and the Ph.D. degree from the University of Twente, Enschede, The Netherlands, in 1992 and 1996, respectively.

From 1996 to 2019, he was with Philips/NXP Semiconductors, Nijmegen, The Netherlands. He is currently a Fellow with Goodix Technologies, Nijmegen. His main interests are class-D amplifiers (CDAs) and integrated power electronics.

Dr. Berkhout currently serves as a member of the Technical Program Committee for the International

Solid-State Circuits Conference (ISSCC). He was a member of the Technical Program Committee of the European Solid-State Circuits Conference (ESSCIRC) from 2008 to 2018 and the ISSCC from 2013 to 2016. He received the 2002 ESSCIRC Best Paper Award. He was a Plenary Invited Speaker on audio at low and high powers at the 2008 ESSCIRC.

Kofi A. A. Makinwa (Fellow, IEEE) received the B.Sc. and M.Sc. degrees from Obafemi Awolowo University, Ife, Nigeria, in 1985 and 1988, respectively, the M.E.E. degree from the Philips International Institute, Eindhoven, The Netherlands, in 1989, and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2004. From 1989 to 1999, he was a Research Scientist with the Philips Research Laboratories, Eindhoven, where he focused on interactive displays and digital

recording systems. In 1999, he joined the Delft University of Technology, where he is currently an Antoni van Leeuwenhoek Professor and the Head of the Microelectronics Department. His research interests include the design of mixed-signal circuits, sensor interfaces, and smart sensors. This has led to 17 books, more than 300 technical papers, and more than 30 patents.

Dr. Makinwa was the Analog Subcom Chair of the International Solid-State Circuits Conference (ISSCC) and has served on the program committees of several other IEEE conferences. He has also served as a Distinguished Lecturer for the Solid-State Circuits Society and an elected member of its Adcom. He is currently one of the organizers of the Advances in Analog Circuit Design Workshop and the IEEE Sensor Interfaces Meeting. He is an ISSCC top-10 contributor (with more than 60 papers) and was a co-recipient of 17 best paper awards, from the JSSC (two), ISSCC (five), and VLSI Circuits Symposium (two), among others. He is a member of the Royal Netherlands Academy of Arts and Sciences.

Huajun Zhang (Graduate Student Member, IEEE) received the B.E. degree in electrical and computer engineering from Shanghai Jiao Tong University, Shanghai, China, in 2015, and the B.S.E. and M.S. degrees in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2015 and 2017, respectively. He is currently pursuing the Ph.D. degree with the Delft University of Technology, Delft, The Netherlands.

In 2016, he joined Analog Devices Inc., Wilmington, MA, USA, as an Analog/Mixed-Signal

Design Intern. From May 2017 to February 2019, he was a Mixed Signal Design Engineer with Analog Devices Inc., Norwood, MA, USA. He joined the Electronic Instrumentation Laboratory, Delft University of Technology, in March 2019. He holds one U.S. patent. His technical research interests include precision analog circuits, class-D audio amplifiers, and ultralow-power data converters.

Mr. Zhang has served as a Reviewer for the IEEE OPEN JOURNAL OF THE SOLID-STATE CIRCUITS SOCIETY, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: REGULAR PAPERS, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, and the IEEE SENSORS JOURNAL.

**Qinwen Fan** (Member, IEEE) received the B.Sc. degree in electronic science and technology from Nankai University, Tianjin, China, in 2006, and the M.Sc. degree (*cum laude*) in microelectronics and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2008 and 2013, respectively.

From August 2007 to August 2008, she was an Intern with the NXP Research Laboratories, Eindhoven, The Netherlands, where she designed a precision instrumentation amplifier for biomedical

purposes. From October 2012 to May 2015, she was with Maxim Integrated Products, Delft. From June 2015 to January 2017, she was with Mellanox, Delft. Since 2017, she rejoined the Delft University of Technology, where she is currently an Assistant Professor with the Electronics and Instrumentation Laboratory. Her current research interests include precision analog, class D audio amplifiers, dc–dc converters for energy harvesters, and current-sensing amplifiers.

Dr. Fan currently serves as an Associate Editor for the *Open Journal* of the Solid-State Circuits Society (OJ-SSCS) and a TPC Member for the International Solid-State Circuits Conference (ISSCC), VLSI Symposium on Technology and Circuits, and European Solid-State Circuits Conference (ESSCIRC).