**Delft University of Technology**

### Hardware Acceleration of High-Performance Computational Flow Dynamics Using High-Bandwidth Memory-Enabled Field-Programmable Gate Arrays

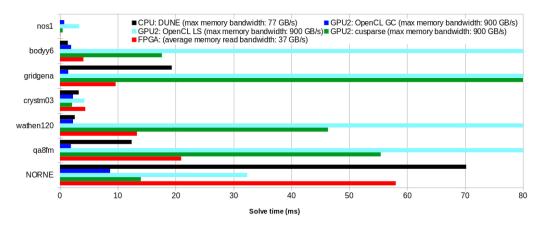

Hogervorst, Tom; Nane, Razvan ; Marchiori, Giacomo; Qiu, Tong Dong ; Blatt, Markus; Rustad, Alf Birger

DOI 10.1145/3476229

Publication date 2022 Document Version Final published version

Published in ACM Transactions on Reconfigurable Technology and Systems

### Citation (APA)

Hogervorst, T., Nane, R., Marchiori, G., Qiu, T. D., Blatt, M., & Rustad, A. B. (2022). Hardware Acceleration of High-Performance Computational Flow Dynamics Using High-Bandwidth Memory-Enabled Field-Programmable Gate Arrays. *ACM Transactions on Reconfigurable Technology and Systems*, *15*(2), 1-35. Article 20. https://doi.org/10.1145/3476229

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

## 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Hardware Acceleration of High-Performance Computational Flow Dynamics Using High-Bandwidth Memory-Enabled Field-Programmable Gate Arrays

TOM HOGERVORST and RĂZVAN NANE, Delft University of Technology, The Netherlands GIACOMO MARCHIORI and TONG DONG QIU, Big Data Accelerate B.V., The Netherlands MARKUS BLATT, OPM-OS AS, Norway ALF BIRGER RUSTAD, Equinor S.A., Norway

Scientific computing is at the core of many High-Performance Computing applications, including computational flow dynamics. Because of the utmost importance to simulate increasingly larger computational models, hardware acceleration is receiving increased attention due to its potential to maximize the performance of scientific computing. Field-Programmable Gate Arrays could accelerate scientific computing because of the possibility to fully customize the memory hierarchy important in irregular applications such as iterative linear solvers. In this article, we study the potential of using Field-Programmable Gate Arrays in High-Performance Computing because of the rapid advances in reconfigurable hardware, such as the increase in on-chip memory size, increasing number of logic cells, and the integration of High-Bandwidth Memories on board. To perform this study, we propose a novel Sparse Matrix-Vector multiplication unit and an ILU0 preconditioner tightly integrated with a BiCGStab solver kernel. We integrate the developed preconditioned iterative solver in *Flow* from the Open Porous Media project, a state-of-the-art open source reservoir simulator. Finally, we perform a thorough evaluation of the FPGA solver kernel in both stand-alone mode and integrated in the reservoir simulator, using the NORNE field, a real-world case reservoir model using a grid with more than  $10^5$  cells and using three unknowns per cell.

CCS Concepts: • **Computer systems organization**  $\rightarrow$  **Reconfigurable computing**; *Heterogeneous (hybrid) systems*; *Data flow architectures*;

Additional Key Words and Phrases: Iterative solvers, FPGA, GPU, ILU0, BiCGStab, CFD, HPC

#### **ACM Reference format:**

Tom Hogervorst, Răzvan Nane, Giacomo Marchiori, Tong Dong Qiu, Markus Blatt, and Alf Birger Rustad. 2021. Hardware Acceleration of High-Performance Computational Flow Dynamics Using High-Bandwidth Memory-Enabled Field-Programmable Gate Arrays. *ACM Trans. Reconfigurable Technol. Syst.* 15, 2, Article 20 (December 2021), 35 pages.

https://doi.org/10.1145/3476229

© 2021 Copyright held by the owner/author(s).

1936-7406/2021/12-ART20 \$15.00

https://doi.org/10.1145/3476229

Authors' addresses: T. Hogervorst and R. Nane, Delft University of Technology, Mekelweg 4, 2628CD, Delft, The Netherlands; emails: tom.hogervorst74@gmail.com, razvan.nane@bigdataccelerate.com; G. Marchiori and T. D. Qiu, Big Data Accelerate B.V., Burgemeestersrand 66, 2625NW, Delft, The Netherlands; emails: marchiori.giacomo@gmail.com, tongdong. qiu@bigdataccelerate.com; M. Blatt, OPM-OS AS, Heyerdahlsvei 12b, 0777 Oslo, Norway; email: markus@dr-blatt.de; A. B. Rustad, Equinor S.A., Arkitekt Ebbels veg 10, Rotvoll, Norway; email: abir@equinor.com.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

#### **1 INTRODUCTION**

The advent of data proliferation and the slowing down of Moore's law is driving many application designers to implement an algorithm's computationally demanding functionality using a hardware accelerator. Although **Graphical Processing Units (GPUs)** benefit from a larger user base because of their massive amount of parallel cores, on-board **High-Bandwidth Memories (HBMs)**, and ease of programming, **Field-Programmable Gate Arrays (FPGAs)** recently have been gaining a lot of attention because of their application-specific customizability. Furthermore, the recent integration of **High-Bandwidth Memorys (HBMs**) in FPGA-based systems have touted the **Field-Programmable Gate Array (FPGA)** as a viable competitor for the **Graphical Processing Unit (GPU)** in emerging machine learning-related domains, but also in **High-Performance Computing (HPC)** applications where the **GPU** was traditionally the sole candidate. The acquisition of Altera by Intel [13] and the recent announcement of AMD acquiring Xilinx [2], two of the biggest **FPGA** providers, can be considered an indication of this trend.

In this context, it is highly relevant to reassess the potential of FPGAs for High-Performance Computing (HPC), when we consider the addition of HBM on board, the increase of on-chip memory (e.g., Ultra RAM (URAM) [34]), and the continuing increase of logic cell resources enabling one to implement complex functionality. To perform this evaluation, we look at an ubiquitous scientific computing field used in many HPC application domains, namely the solution of systems of non-linear partial differential equations in time and space. It is typically not possible to solve these systems exactly through analytical methods. Hence, the equations are discretized in time and over a domain space using finite difference, finite volume, or finite element methods. The derived system of equations is solved, often iteratively using a combination of preconditioners and iterative linear solvers available in one of the many scientific solver libraries, such as DUNE [4] and PETSc [11]. Due to the complexity of implementing linear solvers on **FPGA**, there are only a few previous works that studied the acceleration of them on FPGA. Those works often made assumptions to simplify the design and implementation, such as either focusing solely on singleprecision floating point support, or using simple solvers without preconditioners, and all ignored the integration into the whole scientific computing pipeline. However, to realistically assess the potential of FPGAs, it is important to eliminate the aforementioned restrictions. Consequently, in this work, we develop a complete solver with a preconditioner on FPGA with support for double precision, which is utterly important in a real-world setting because it enables the convergence to a solution. Furthermore, we integrate our work in a state-of-the-art reservoir simulator, OPM Flow [25], and validate our work by running with a real-world use case containing a large number of grid cells  $(10^6)$ .

To accomplish our study goals, we develop a novel BiCGStab [31] solver implementation with ILU0 [5] as preconditioner on **FPGA**. This combination of preconditioner and linear solver was chosen because it is known be a good solver for the large sparse linear systems arising when simulating oil reservoirs [35]. Due to the challenging properties of the linear systems, it is mandatory to use powerful Krylov methods like BiCGStab together with good preconditioners and high precision. Often oil reservoir simulators use even more powerful preconditioners like nested factorization [3, 28]. Otherwise, the iterative solver will not converge due to highly heterogeneous material parameters, which lead to rather ill-conditioned matrices. This choice of solver also leads to an apples-to-apples comparison with the CPU performance on the NORNE field dataset, as this combination was best performing in that case. To maximize the performance, we use manually written **Register-Transfer Level (RTL)**. Please note that there might be other solvers that can be more efficient in terms of time needed per iteration of the linear solver on a parallel architecture such as the **FPGA** (and **GPU**) than an ILU0 preconditioner, but these still might not be suitable to

Hardware Acceleration of HPC CFD Using HBM FPGAs

reach convergence or even scale in terms of time needed to reach the solution. However, this is left for future work because it was most important to make certain the results are close to the ones obtained by the already validated software-only simulation. Therefore, we selected the same combination of preconditioner and solver as those used by default in *OPM Flow* and designed the solver to support double precision because high accuracy is required, as otherwise the selected real-world case would not converge. Furthermore, integration is key to benchmark the performance in the overall system. Previous work [6, 16, 32] has only benchmarked the solvers in isolation, whereas we consider the whole system for benchmarking, where including the memory transfers between off-chip and off-board as well as the pre- and post-processing times is crucial. Finally, we make our work available in the **Open Porous Media (OPM)** Git repository [19].

The contributions of this work are summarized as follows:

- We propose a novel **Compressed Sparse Row (CSR)**-based encoding to optimize **Sparse Matrix-Vector (SpMV)** multiplication on **FPGA**, which is the core functionality required to implement iterative solvers.

- We develop a hardware model to predict and guide the design of the solver, helping us to understand trade-off between area and performance when scaling the resources.

- We design a novel ILU0-BiCGStab preconditioned solver on **HBM**-enabled **FPGA** using optimized hand-coded **Register-Transfer Level** (**RTL**).

- We integrate the proposed solver in *OPM Flow*, both for **FPGA** and **GPU**. Furthermore, we make all sources available in the **OPM** Git repository [19].

- We provide extensive evaluation results for both stand-alone solver kernel benchmarking and complete reservoir simulation execution on a real-world use case running on three different types of systems: CPU, **FPGA**, and **GPU**.

The rest of the article is organized as follows. In Section 2, we introduce the background required to understand the work, whereas in Section 3, we highlight related works. We then start a bottomup explanation approach in which we first describe the **Sparse Matrix Vector Multiplication** (**SpMV**) kernel in Section 4, then the solver in Section 5, and discuss the performance hardware model used to guide the design in Section 6. Finally, in Section 7, we present the experimental results.

### 2 BACKGROUND

#### 2.1 Sparse Matrix Iterative Solvers

The central problem in this work is to solve  $A * \vec{x} = \vec{b}$  for vector  $\vec{x}$ , where A is a known sparse matrix and  $\vec{b}$  is a known dense vector. There are different methods for solving such a problem, which can be grouped into direct solvers and iterative solvers. Direct solvers, as the name implies, use linear algebra techniques to solve the problem for x directly and precisely. However, direct methods are not suitable to solve large sparse linear systems, as is usually the case in a real-world **HPC** application, because they will fill in the zero values of the sparse matrix to solve the problem, resulting in a very high computational cost and memory usage. Iterative solvers are a heuristic alternative to direct solvers: they start from an initial guess of the solution and then iteratively improve this guess, until it is deemed close enough to the actual solution. In this article, we use the BiCGStab (bi-conjugate gradient stabilized) solver with the ILU0 (incomplete LU factorization with no fill-in) as the preconditioner because this combination is the most robust and the default software configuration used in *OPM Flow*. Consequently, besides the goal of studying the acceleration potential of FPGAs, another implicit goal required by the reservoir engineers using the simulator was to obtain simulation results close to the software counterpart. Consequently, although it might not

### ALGORITHM 1: Pseudo-code BiCGSTAB Solver

**Input**:  $\vec{b}$ ,  $\vec{x}$ ,  $A \Rightarrow \vec{b}$  and  $\vec{x}$  are  $\vec{b}$

$\triangleright \vec{b}$  and  $\vec{x}$  are N element arrays, A is an NxN matrix Output:  $\vec{r}$ ,  $\vec{x}$

$\triangleright$  Both are *N* element arrays

1:  $\vec{r} = \vec{b} - spm\upsilon(A, \vec{x})$ 2:  $\vec{rt} = \vec{r}$ 3:  $\rho = 0$ 4:  $\vec{p} = \vec{0}$ 5:  $norm = sqrt(dot(\vec{r}, \vec{r}))$ 6: conv\_threshold = norm/desired\_improvement 7: while norm > conv\_treshhold do  $\rho_{new} = dot(rt, r)$ 8. 9:  $\beta = (\rho * \alpha) / (\rho_{new} * \omega)$  $\vec{p} = axpy(\beta, \vec{r}, axpy(\omega, \vec{p}, \vec{v}))$ 10: 11:  $\vec{y} = preconditioner(\vec{p})$  $\vec{v} = spmv(A, \vec{y})$ 12:  $\alpha = \rho_{new}/dot(\vec{rt}, \vec{v})$ 13: 14:  $\rho = \rho_{new}$ 15:  $\vec{x} = axpy(\alpha, \vec{x}, \vec{y})$ 16:  $\vec{r} = axpy(-\alpha, \vec{r}, \vec{v})$  $norm = sqrt(dot(\vec{r}, \vec{r}))$ 17: if norm  $\leq$  conv threshold then 18: break 19: end if 20: 21:  $\vec{y} = preconditioner(\vec{r})$  $\vec{t} = spm\upsilon(A, \vec{y})$ 22:  $\omega = dot(\vec{r}, \vec{t})/dot(\vec{t}, \vec{t})$ 23:  $\vec{x} = axpy(\omega, \vec{x}, \vec{y})$ 24:  $\vec{r} = axpy(-\omega, \vec{r}, \vec{t})$ 25: 26:  $norm = sqrt(dot(\vec{r}, \vec{r}))$ 27: end while

be the best choice for acceleration on a parallel architecture, fulfilling the conformance criteria led us to use the same solver used in the software stack.

Algorithm 1 shows the pseudo-code of the BiCGStab solver. This code makes use of several other functions:

- An **SpMV** function, which performs an SpMV multiplication.

- A dot function, which calculates the dot product (or inner product) of two vectors.

- An axpy function, which scales its first input vector by a scalar value and adds it to its second input vector (i.e.,  $axpy(\alpha, \vec{x}, \vec{y})$  performs:  $\alpha * \vec{x} + \vec{y}$ ).

- A preconditioner function. This is an optional part of the solver and does not have a set behavior. For more information about preconditioners, see Section 2.3.

The result of the solver are two vectors:  $\vec{x}$ , which is the estimation of the solution of  $A * x_{actual} = \vec{b}$ , and  $\vec{r} = \vec{b} - A\vec{x}$ , a residual vector, which is an indication of how close the result  $\vec{x}$  vector is to

the exact solution  $x_{actual}$ . It is worth noting in Algorithm 1 how the exit condition of the solver is set, or, in other words, how the algorithm determines when to stop iterating because the results are sufficiently close to the actual result. The solver stops iterating when the norm of the residual is lower than a certain *convergence* threshold. There are two ways in which this convergence threshold can be chosen: either it is a constant value, in which case we speak of an absolute exit condition, or it is a value set by the norm of the initial residual by a *desired improvement* factor, in which case we speak of a relative exit condition. An absolute exit condition can be useful when one needs to be certain that the result of a solver is at least within a certain numerical distance from the actual result. However, when solving for multiple different matrices from different domains, a matrix with lower values all across the board might start off at a lower error and also reach the absolute exit condition more quickly. In such a case, a relative exit condition leads to a more fair comparisons between solves, which is why a relative exit condition is used in this work.

Ignoring for now the preconditioner, what remains in the BiCGStab solver are a series of vector operations and **SpMV**s, as well as a few scalar operations. From profiling the solver, it is clear that the majority of its computational time is spent on performing **SpMV** and SpMV-like computations. Therefore, the first goal to design a performant solver kernel would be to perform the **SpMV** efficiently.

#### 2.2 SpMV Multiplication

The **SpMV** is a widely used, rather elementary operation in which a sparse matrix is multiplied by a dense vector. How this operation will be performed algorithmically depends on how the matrix is stored. A sparse matrix consists of many more zeroes than non-zero values, which means that storing all of them is not efficient. There are a variety of different formats in which only the non-zero values of a sparse matrix can be stored. Among these formats, **Compressed Sparse Column (CSC)** and CSR are two of the most commonly used and have inspired many variants (e.g., [23, 24]). The **Compressed Sparse Row (CSR)** and CSC formats both store matrices efficiently without putting any restrictions on the contents of the matrix, whereas other formats may require the matrix to have certain sparsity pattern features such as symmetry, values being repeated multiple times, or store additional non-zeroes, such as sliced ELLPACK [15], to be efficient. In this article, we focus only on the **CSR** representation, as the column-major CSC format would be more difficult to use during the application of the ILU0 preconditioner because ILU0 goes through the matrix row by row (see Section 2.3), which would be difficult to implement in the column-major CSC format.

The **CSR** format consists of three arrays: an array with all non-zero values of the matrix stored row-major, an array of the column indices of those non-zero values, and an array of row pointers, which contains an index for each row to identify which non-zero value is the first value of that row, plus a last additional entry containing the total number of non-zeroes stored. The pseudo-code showing how the SpMV is performed on a matrix stored in the CSR format is given in Algorithm 2. It is worth noting that there is a high degree of parallelism available in this SpMV. In theory, the calculations for all rows can be done in parallel because the result of one row is never used during the calculation of another row. However, in practice, the irregular memory accesses in the x vector, which depend on the random column index representing the location of the non-zero value in the system matrix, restrict the amount of parallelism that can be exploited efficiently. The main bottleneck is the requirement to replicate the x vector to enable multiple read units to feed independent row **Processing Units (PUs)**. This replication is impractical for realistic large use cases for two main reasons: (1) limited on-chip (i.e., cache) memory and (2) significant pre-processing computations required to align the read data feed into the multiple PUs, which is needed to exploit the maximum available bandwidth in state-of-the-art accelerators with **HBM**.

### ALGORITHM 2: Pseudo-code of a CSR SpMV

**Input**: *nnzs*, *colInds*, *rowPointers*, *x*

▶ *nnz* is an *M* element array of floating point values,

▶ *colInds* is an *M* element array of integers,

▷ rowPointers is an N + 1 element array of integers,

$\triangleright x$  is an *N* element array of floating point values

#### **Output**: y

$\triangleright$  *y* is an *N* element array of floating point values

```

for 0 ≤ i < N do</li>

y[i] = 0

for rowPointers[i] ≤ v < rowPointers[i + 1] do</li>

y[i] = y[i] + nnzs[v] * x[colInds[v]]

end for

end for

```

#### 2.3 The ILU0 Preconditioner

How hard a series of linear equations is to solve depends on various different aspects of those equations, or the matrix that represents them. In other words, how many non-zeroes the matrix has, where they are located in the matrix, and their values in relation to one another, among other things, all play a role. The *condition number*  $\kappa(A)$  of a matrix A, which is the ratio of the biggest eigenvalue of the matrix divided by the smallest one, is a measure of how relative changes in the right-hand side b of a linear equation  $A * \vec{x} = \vec{b}$  result in relative changes of the solution  $\vec{x}$ . In addition, it is a measure of how changes in A affect the solution and how numerical errors affect the solution. Often, convergence of iterative methods is worse for matrices with high condition numbers. Therefore, although iterative solvers such as BiCGStab are a powerful method for solving sparse matrix problems, they might still take many iterations before they approach the result within the desired precision when solving matrices with a high condition number.

One technique for reducing the amount of iterations needed for BiCGStab and other Krylov methods is utilizing a preconditioner. Generally, a preconditioner is a transformation or matrix M that approximates A, but for which  $M * \vec{x} = \vec{b}$  is less computationally expensive to solve than  $A * \vec{x} = \vec{b}$ . If M is a matrix, then the preconditioned method solves  $M^{-1}A * \vec{x} = M^{-1} * \vec{b}$ . Note that if M is a good approximation for A, then this system will have a much better condition number than the original one and hence the iterative solver will converge faster. A simple example of a preconditioner is the Jacobi method with M = diag(A), the diagonal values of A. Many different types of preconditioners exist, from very simple ones that only very weakly approximate the problem's solution to complex ones that almost solve the system by themselves. Unfortunately, how well a preconditioner performs depends not only on the type of preconditioner but also on the matrix being solved. For example, the Jacobi preconditioner is fairly accurate if the original matrix has most of its non-zeroes clustered around the diagonal, and if the values on the diagonal have a higher magnitude than those off the diagonal, but does not work as well for matrices that do not have those characteristics.

In this work, we utilize the zero fill-in incomplete LU factorization (ILU0) as the preconditioner, which falls somewhere in the middle: it approximates the system reasonably while not being too computationally intensive to apply. Using an ILU0 consists of two steps. First, before the solver is started, an incomplete LU decomposition is performed. To understand what this is, we must first introduce the LU decomposition. LU decomposition is a direct solving method that calculates an

| Preconditioner | None             | None      | Jacobi    | Jacobi    | ILU0      | ILU0             |

|----------------|------------------|-----------|-----------|-----------|-----------|------------------|

| Matrix         | 10 <sup>-2</sup> | $10^{-6}$ | $10^{-2}$ | $10^{-6}$ | $10^{-2}$ | 10 <sup>-6</sup> |

| Hummocky       | 5.9              | 925       | 1.2       | 125.8     | 3.1       | 32.3             |

| bcsstk25       | 5.8              | 3396      | 3.7       | 34.9      | 18.9      | 4331             |

| bodyy6         | 4.4              | 224       | 1.2       | 86.3      | 3.7       | 15.7             |

| wathen120      | 8.0              | 112       | 5.2       | 25.2      | 12.8      | 18.7             |

| gridgena       | 2.0              | 403       | 5.9       | 643.3     | 18.7      | 324.7            |

| qa8fm          | 12.7             | 114       | 13.1      | 79.7      | 44.8      | 60.3             |

Table 1. CPU Solver Time in Milliseconds with  $10^{-2}$  &  $10^{-6}$  Exit Condition

upper-triangular matrix U and a lower-triangular matrix L so that A = L \* U. Such a decomposition can be done using Gaussian elimination, among other methods. Once such a decomposition has been found,  $A * \vec{x} = \vec{b}$  can be solved for  $\vec{x}$  by first solving  $L * \vec{y} = \vec{b}$  for  $\vec{y}$  and then solving  $U * \vec{x} = \vec{y}$ for  $\vec{x}$ . Since L and U are triangular matrices, these two solves can be done using forward and backward substitution, respectively. However, like we discussed in the previous section, direct solving methods become very computationally intensive for sparse matrices because they start filling in the zero values of the matrix, and LU decomposition is no exception. Incomplete LU(N) decomposition decreases the high computational cost of LU decomposition for sparse matrices by reducing the amount of fill-in that happens, where N is an indicator of how much fill-in is done. The case were N = 0 (ILU0) means that for the L and U matrices, the decomposition generates non-zero values only at the same indices where A had non-zero values. Since the result of the decomposition algorithm, L and U, is not unique, it is common practice to restrict the L matrix to be a unit triangular matrix. With the diagonal of the L matrix set to known constant values, it is possible to store both the L and U matrices resulting from ILU0 decomposition in a matrix with the same sparsity pattern as the decomposed matrix. The diagonal of this LU result matrix belongs to the U matrix, and the assumption that the L matrix has a diagonal filled with ones needs to be taken into account by the operations performed using this matrix.

Once the ILU0 decomposition is complete, the solver can start. The solver will then apply the ILU0 preconditioner in every iteration. In this apply\_ILU0 step, the solution to the matrix solve is approximated by solving for the LU matrix. Pseudo-code of the ILU0 application is shown in Algorithm 3. The ILU0 application consists of two parts, represented by the two for loops in lines 1 and 11: a forward substitution on the lower-triangular part of the LU matrix, and a backward substitution on the upper-triangular part of that matrix. Both loops are very similar in the operations they perform, with the main differences being that the forward substitution traverses the matrix top to bottom, whereas the backward substitution traverses the matrix bottom to top, and that the backward substitution concludes by dividing the result array by the values on the diagonal of the LU matrix. It is worth noting that although these loops ostensibly have the same basic structure as the SpMV loop, there is one major difference: the results of one row depend on rows before it, which means the operations on the rows cannot be performed all in parallel. See Section 2.4 for more on how this issue can be circumvented somewhat by reordering the matrix.

To quantify the effect of the ILU0 preconditioner in practice for our solver performance, we ran software implementations of the solver without a preconditioner and with the Jacobi and ILU0 preconditioners on several benchmark matrices. The matrices were obtained from the SuiteSparse matrix collection [7].

Table 1 shows the results of these tests, which were obtained by running the preconditioned solver for a single thread on an Intel i7-9700 CPU with 16 GB of RAM. Two exit conditions were used: the more precise exit condition requiring the absolute value of the residue being reduced by

### ALGORITHM 3: Pseudo-code of the applying of the ILU0 preconditioner

Input: LUmat, *x*

▶ LUmat is an NxN sparse matrix in the CSR format

$\triangleright x$  is an *N* element array of floating point values

### Output: p

$\triangleright p$  is an *N* element array of floating point values

```

1: for 0 \le i < N do

p[i] = x[i]

2:

for LURowPointers[i] \leq v < LURowPointers[i + 1] do

3:

pIndex = LUcolInds[v]

4:

if pIndex \ge i then

5.

break

6:

end if

7.

p[i] = p[i] - LUnnzs[v] * p[pIndex]

8:

end for

٩.

10: end for

11: for N > i \ge 0 do

diagIndex = LURowPointers[i + 1]

12:

for LURowPointers[i + 1] > v \ge LURowPointers[i] do

13:

pIndex = LUcolInds[v]

14:

if pIndex \leq i then

15:

diagIndex = v

16:

break

17:

end if

18:

p[i] = p[i] - LUnnzs[v] * p[pIndex]

19:

end for

20.

p[i] = p[i]/LUnnzs[diagIndex]

21.

22: end for

```

$10^{-6}$  of its initial value, and the less precise exit condition requiring a residue norm reduction of  $10^{-2}$ . Not shown in the table are the number of iterations in which the solvers converged, which in all matrices except for *bcsstk25* were lower when ILU0 preconditioning was used over the other two preconditioning options. However, a lower iteration count does not directly result in a higher solver performance. The first reason for this is the time the pre-processing of the preconditioner takes, which accounts for between 60% and 90% of the time taken by the lower-accuracy solver with the ILU0 preconditioner. The Jacobi preconditioner has barely any pre-processing time, and it is powerful enough to be preferred over no preconditioner for all but one matrix, and preferred over ILU0 for all matrices when the solver's precision is low. Only when the solver's precision was set higher did the ILU0 preconditioner's power show: the number of iterations required to reach this accuracy was high enough that the pre-processing time no longer dominated the runtime. For most matrices, the ILU0 preconditioner reduced the iteration count enough that the solve performance was better than that of the other preconditioner options tested, with the bcsstk25 matrix being an exception, as its solve was only accelerated by the Jacobi preconditioner. We suspect the matrix' narrow banded structure and high values on the diagonal make it particularly well estimated by the Jacobi preconditioner. The second reason a lower iteration count does not translate to a higher solver performance directly is not captured in our software tests. In other words, different preconditioners might be easier or harder to parallelize, therefore making them

more or less worthy to be accelerated on hardware, respectively. The single vector calculation that is the applying of the Jacobi preconditioner is easy to parallelize and therefore is suitable for hardware acceleration. ILU0 application, however, is not that inherently parallel but can be made more parallel when using **graph coloring (GC)**.

### 2.4 Matrix Reordering

As covered in Section 2.3, the ILU0 application function does not inherently have a lot of parallelism for a hardware accelerator to exploit. However, by reordering the matrix, some parallelism in this function can be obtained. The goal of such a reordering is to group rows together that do not depend on one another (i.e., that do not have non-zero values in columns that have the same index as the row indices of other rows in the group). During our work, we have focused on two ways of doing such a reordering: **level scheduling (LS)** and GC.

2.4.1 Level Scheduling. LS is a way of reordering a matrix by moving the rows and the columns of the matrix. In other words, the rows are grouped together in colors that can be operated on in parallel, then the columns are reordered in the same way to keep the matrix consistent in the (re)order of the unknowns, which is required during ILU0 decomposition. LS not only groups independent rows together into "levels" but also keeps the order of dependencies of the original matrix intact [26]. In other words, if a certain row *j* that depends on row *i* comes after row *i* in the original order, then after LS, row  $j_{ls}$  (the row to which row *j* was moved during LS) will still come after  $i_{ls}$  for all possible values of *i* and *j*. An LS algorithm will go through the matrix and gather all rows that do not depend on any other rows into the first level. Then it will go through the matrix again and group all rows that only depend on rows in level 0 into level 1. Then it will fill level 2 with rows only dependent on rows from levels 0 and 1, and so on until every row has been added to a level.

2.4.2 Graph Coloring. GC is a term that we use to describe the reordering of matrices into groups ("colors") of independent rows that do not require the maintaining the order of dependencies in a matrix. To be more specific, we use the Jones-Plassmann algorithm [14] to do GC. This algorithm assigns a random value to every row in the matrix, and then groups all rows that have a higher number than all not-yet-grouped rows it depends on into a single color, and keeps repeating this process until all rows have been assigned a color. In this work, GC was chosen over the other method because it is parallelizable and it allows more control over the maximum amount of rows and columns in a color, which will alleviate some of the size restrictions a hardware design may impose. The disadvantage of GC is that it is not guaranteed to find the minimum number of colors, and thus the highest amount of parallelism because of its random nature.

2.4.3 *Reordering Scheme Selection.* Selecting one of the two matrix reordering methods depends on the answer to how important it is to obtain a solution that is as close as possible to the one obtained without reordering. If the answer is *very important*, then LS is the preferred reordering scheme. However, when the answer is *not important*, because an iterative solver is already estimating the result instead of solving the system precisely, GC can be used if the result is *close enough* to the actual solution.

#### 2.5 Sparstitioning

To increase the scalability of our design and allow it to work on larger matrices, we will use sparstitioning [27]. Sparstitioning is a method for splitting both the matrix and the vector of a matrixvector operation into partitions so that no unnecessary data is read during the running of the operation on each partition. However, we make two changes to the sparstitioning algorithm. First, we modify how the partitions are chosen to conform with the matrix reordering scheme chosen. Concretely, every color/level will be one partition. Second, we modify how the vector partitions are stored. When sparstitioning is used for an SpMV, the vector that is operated on is stored in a partitioned format, which introduces some duplication of the vector data. However, storing the vector in this way is not convenient because the non-partitioned vector is needed for the vector operations of the solver. Therefore, instead of storing the vector partitions themselves, our design stores an array that denotes for every partition which indices of the vector are part of that partition. Consequently, only the relevant values are read from the vector when computations start on each partition.

Because of the matrix reordering and sparstitioning optimization required to design an HPC iterative solver, we modify the standard CSR matrix storage format in two ways. First, the number of non-zeroes, rows, and vector partition indices used in each partition of the matrix need to be known. These will be collectively referred to as the sizes of each color. Second, the vector partition indices themselves are needed so that the solver knows which values of the matrix are accessed by each color. To account for these CSR modifications, we introduce our own format, **Compressed Sparse Row-Offsets (CSRO)**, which we will formally introduce in Section 4.2.

#### 3 RELATED WORKS

#### 3.1 SpMV Multiplication on FPGAs

As described in Section 2.1, we focus on **Conjugate Gradient (CG)** solvers in this article, particularly on its general version (i.e., not only for symmetric matrices as CG is), BiCGStab. Previous research into accelerating (parts of) CG solvers using FPGA has focused until now mostly on accelerating the SpMV kernel [30] for one good reason: the SpMV function has a wide range of uses in a broad variety of domains, and because of its irregular memory accesses, it is not efficiently performed by classical von-Neumann architectures like CPUs. This makes SpMV a perfect candidate to be accelerated using customizable dataflow architectures that can fully exploit application-specific configurable memory hierarchies. Furthermore, in the context of linear algebra iterative solvers, SpMV takes up most of the processing time, making it an even more interesting target for acceleration. Consequently, a plethora of previous works addressed the topic of accelerating SpMV on FPGAs. Therefore, we only list a few of the performant designs without trying to be exhaustive:

- The SpMV unit proposed by Zhuo and Prasanna [36] achieves a performance of between 350 MFLOPS and 2.3 GFLOP/s, depending on the number of PUs, the input matrix, the frequency, and the bandwidth. However, to realize their design, the authors use zero-padding and column-wise blocking of the matrix. These design choices make SpMV less efficient due to storage overhead that becomes critical for large matrices and very inefficient to use in combination with an ILU0 preconditioner.

- Fowers et al. [12] implemented an SpMV unit that uses a novel sparse matrix encoding designed with the fact that the matrix will be divided over multiple PUs in mind, and a banked vector buffer that allows many memory accesses to the input vector at the same time. That implementation reaches a performance of up to 3.9 GFLOP/s but does not actually outperform GPU or CPU implementations for large matrices.

- Dorrance et al. [8] obtain a performance of up to 19.2 GFLOP/s for their CSC-based SpMV accelerator, which is as far as we could find the highest performance of any FPGA-based implementation of SpMV. This high performance was thanks to the high computational efficiency of the implementation paired with its 64 PUs and high bandwidth (36 GB/s). However, as can be seen in Algorithm 3, in the applying of the ILU0 preconditioner, the result of one row is needed to calculate the result of ones after it. So, unlike the SpMV, the apply\_ILU0

cannot be done as easily with CSC as it can with CSR. In fact, the CSC is completely unsuitable to use in conjunction with ILU0, and as a result we will not use that storage format in this article.

Please note that the scope of the work is not to design the fastest SpMV unit possible, but also to integrate this in a larger and complex application that is a preconditioned linear solver. Consequently, although some of the design choices might be sub-optimal for the design of the *fastest* SpMV (e.g., using a CSR-like format instead of the more parallelizable CSC format), which is thus not a primary goal, we focused on the complete integration and looked for the best SpMV design options from a system-level view and not SpMV in isolation as most of previous work considers. Nevertheless, the SpMV designed and implemented in this work is on par with the best SpMV solution we could find in the literature when we consider normalized resources and bandwidth as comparison parameters. Our SpMV is able to achieve up to 4.5 and 8.5 GFLOP/s in double and single precision, respectively.

#### 3.2 Sparse Matrix CG Solvers on FPGAs

Research into designing a complete CG solver on an FPGA has been done as well. However, probably due to the complexity of iterative solver algorithms coupled with a limited area, small on-chip memory, and no HBMs available on previous generation FPGAs, we could find only a handful of related works of solvers on reconfigurable hardware:

- Morris et al. [16] implement a CG solver on a dual-FPGA using both a HLL-to-HDL compiler and custom floating point units written in VHDL. Despite the fact that using the HLL-to-HDL compiler is probably less optimized than writing VHDL directly, they obtain a speedup over software of 30%, showcasing the potential of FPGA in accelerating sparse CG solvers.

- Wu et al. [32] implemented a CG solver on an FPGA consisting of an efficient SpMV unit, a vector update unit, and a diagonal preconditioner. They obtain a speedup between 4 and 9× over their software implementation.

- Chow et al. [6] introduce a novel way of statically scheduling accesses to the on-chip memory in a **Conjugate Gradient** (CG) solver on an FPGA. Despite the initial cost of performing this scheduling, an average speedup of 4.4 over a CPU solver and of 3.6 over a GPU solver is achieved.

However, different from the work in this article, all of this previous research focused on smaller (i.e., dimension size up to 66,127) scale matrices that are not enough for a HPC real-world application setting. For example, a small reservoir contains more than 10<sup>5</sup> cells and a medium more than  $10^6$  cells, whereas a large model contains more than  $10^7$  grid cells (which translates to the dimension N of the underlying matrix). Please note also that double precision is required to store the model data. In this work, we focus on a small reservoir model due to the limited on-chip FPGA BRAM resources required by our design (i.e., the NORN model used in Section 7 has a dimension of 133,293 cells). Another issue that all of these implementations share is that no or only a very simple preconditioner has been used. Preconditioners can improve the performance of a solver significantly, as they reduce the amount of iterations that the solver needs to run until it reaches its desired precision significantly. Despite costing additional time to perform each iteration, the ILU(0) preconditioner used in this work improves the performance of all kinds of CG solvers over cases without preconditioners or with the diagonal preconditioner [29]. Consequently, not using a preconditioner in an iterative solver for a HPC real-world application that requires very large and sparse matrices is not an efficient approach. Finally, using the CG solver limits the applicability of the design to only problems that use symmetric matrices to describe the physical system.

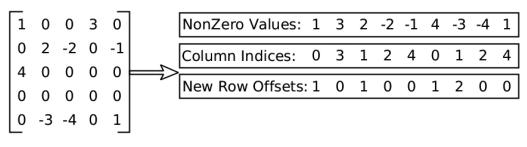

Fig. 1. An example matrix stored in the novel CSRO format.

#### 4 SPMV MULTIPLICATION

#### 4.1 Design Objective

The main objective of our SpMV kernel on the FPGA is to ensure that the unit has a high computational efficiency, which is required to fully exploit the **HBM** available on the state-of-the-art FPGA generations such as the Xilinx Alveo U280 [33] data center accelerator card. The remainder of this section highlights the design choices of the SpMV implementation for the **HPC** domain when using the latest **HBM**-enhanced **FPGA** accelerators.

### 4.2 The Matrix Format

As described in Section 3.1, we have chosen to base our kernel on the row-major CSR matrix storage format. CSR is also the default format used in *Flow*, a real-world HPC software application that we will use in Section 7 to validate our results and benchmark the performance. However, this format poses a challenge for any HPC FPGA-based design because the CSR contains one integer per matrix row to describe how many values are in each row. Since our design objective is to maximize throughput of the SpMV unit, we want to feed as many non-zero values and column indices into the SpMV unit as it can sustain on every clock cycle. Unfortunately, it is not straightforward when using the CSR's *rowPointers* to determine to which row each value belongs to. The number of rows a given number of non-zero values in a matrix belong to can vary wildly based on the matrix's sparsity pattern. Consequently, the number of rowPointers that need to be read every cycle also varies, and also depends on the values of the rowPointers of the cycle before it. A hardware implementation would by necessity need to set a maximum number of row pointers it can read every cycle, thereby putting restrictions on the matrices it can process. To circumvent this, we introduce a novel sparse matrix storage format based on CSR to be used by our accelerator.

Similar to CSR, this new format contains the matrix's non-zero values and their column indices as two arrays, but instead of the rowIndices, it contains a new row offset for every non-zero value in the matrix. Because of the added offset array, this new format is tentatively called *CSRO* format. A value in the newRowOffset array is 0 if the non-zero value at that same index is in the same row as the non-zero value before it. If a non-zero value is not in the same row as the value before it, then the rowOffset at the same index will be equal to 1 + the number of empty rows between that non-zero value's row and its predecessor's row. To help illustrate how a matrix is stored in the CSRO format. Figure 1 shows a matrix as it would be represented in the CSRO format. Note that the NewRowOffset value of the first value in the CSRO format is 1. This is a convention adopted to show that the first row starts with the first value.

4.2.1 The Blocked CSR. The **Open Porous Media (OPM)** platform and its flow simulator do not use regular CSR but rather blocked CSR, in which each non-zero value in the matrix is not one

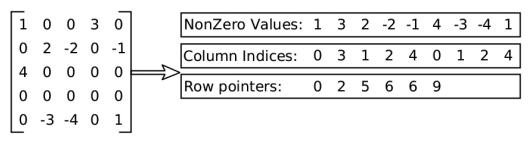

Fig. 2. An example matrix stored in the CSR format.

value but a  $3 \times 3$  matrix of values. This is done to group together all relevant physical information about a single point of the reservoir that the matrix modeled. Unfortunately, the nine values in the  $3 \times 3$  blocks are not convenient for an FPGA. Not only do these blocks often contain zeroes (about half of all values in the blocks of the NORNE testcase are zeroes), but the odd number of values in a block poses a problem when reading them over the ports of the FPGA or storing them in its internal memories, all of which are built to consist of an even number of values. Since the new matrix format that we introduce and the sparstitioning already require extensive reordering of the non-zero values of the matrix, we take this opportunity to also remove the blocking from the matrices in those steps. As a result, the FPGA solver kernel primarily works on non-blocked matrices. The only exception to this is the division at the end of the backward substitution step in the apply\_ILU0. Here, a division by the values on the diagonal needs to be done, and this value on the diagonal is a block. These diagonal blocks are the only blocks that could not be removed, and as a result the hardware kernel still uses those blocks as inputs.

#### 4.3 Design Overview

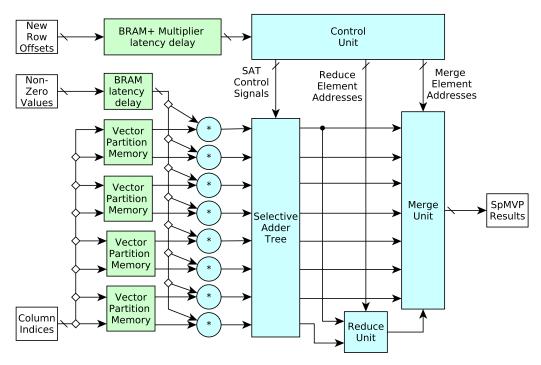

4.3.1 The SpMV Pipeline. The upper limit of the throughput of our SpMV unit design is determined by the number of multipliers in the unit. Thus, to achieve a high computational efficiency, our design aims to stream values into those multipliers every cycle. Figure 3 shows how data is streamed into the multipliers: non-zero values and column indices are read from the memories that hold them, and the column indices are used as addresses at which to read elements from the input vector, whereas the non-zero values are delayed by the delay of the vector memory. This way, the non-zero matrix values and the corresponding vector elements arrive in the multiplier at the same time. There is one memory that holds the vector partition for every two multiplier units, because the BRAM blocks of an FPGA have at most two read ports. Which values of the vector are part of a certain partition is determined by the vector partition indices of that partition. Those values are calculated by the software during pre-processing. Each vector partition memory contains the entire vector partition, so the data is replicated and stored in each one. Although not the most space-efficient solution, this does allow a high number of simultaneous memory accesses at different addresses, which is what the SpMV unit requires.

After the multiplications have finished, the SpMV unit needs to add together the multiplication results that belong to the same matrix row together to obtain the SpMV result of that row. For this, we designed a **selective adder tree (SAT)** and a reduce unit, which receive instructions about which values to add together from a control unit. This control unit in turn obtains this information from the new row offset data. The SAT adds all the values in a single cycle that belong to the same row together, whereas the reduce unit adds together the SAT results from different clock cycles that belong to the same row. SAT results that already represent the final result of a row (i.e., if all the values of that row were in the same clock cycle) do not need to go into the reduce unit. Finally,

Fig. 3. A high-level schematic of the SpMV unit.

a merge unit merges all of the results of the adder tree and reduce unit into a set number of output ports that will be written to a result memory.

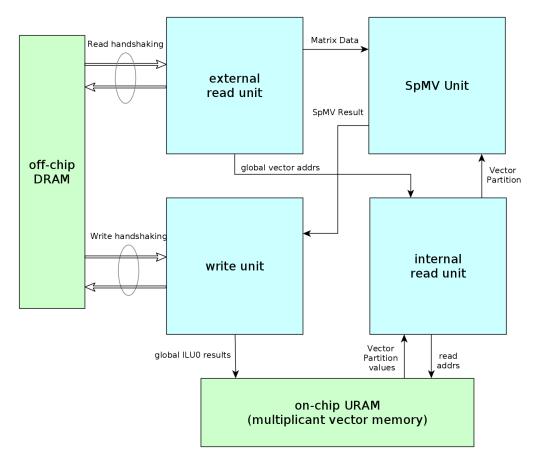

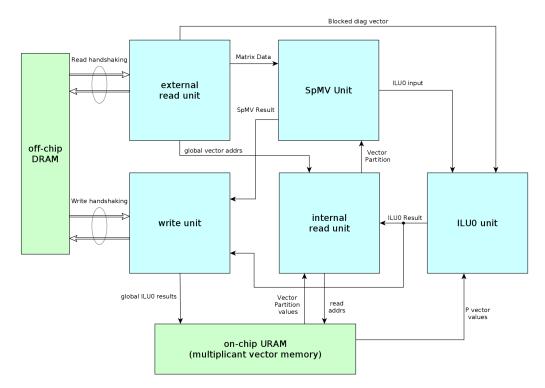

*4.3.2 SpMV Top Level.* Although the SpMV pipeline is the most important part of the SpMV unit, as it does the calculations, some additional units are needed to keep the pipeline running correctly. These units are as follows:

- The external read unit handles all reads from outside of the FPGA chip. At the start of the SpMV run it reads the sizes of all colors, and it uses these to read all matrix data that is needed during the SpMV.

- For the SpMV unit to be able to use sparstitioning with vector partition indices, the vector values at those indices need to be able to be read quickly. To achieve this, our FPGA design contains a single large URAM memory to store the multiplicant vector once. Due to the current size chosen for this memory in the design, up to 262,144 values can be stored, meaning that a matrix may not have more than 262,144 columns to be able to be multiplied by the kernel. The internal read unit coordinates reads from this memory. It receives the vector partition indices of the current color from the external read unit, reads the vector values at those indices, and sends those values into vector partition memories of the SpMV pipeline.

- The results of the SpMV pipeline can be out of order, as the time some results spend in the reduce and merge units are different from others. The write unit stores the results of the SpMV pipeline in a memory block that has been cyclically partitioned so that it can write multiple results into it at the same time while also reading from it. It also keeps track of up to which index all results have been received. Whenever it has received enough values to fill up a cacheline, it will queue up that line to be sent to the HBM.

Fig. 4. Schematic of SpMV top level.

An overview of the SpMV top-level unit is shown in Figure 4. Not shown in this figure is the control logic around it that instructs the units how much data to read or write and to/from where. To do this, the control logic keeps track of which color it is currently operating on and how many still remain.

4.3.3 Non-Partitioned SpMV. One of the tasks the SpMV top-level unit must perform is the reading of the vector partition data that the sparstitioning adds to the matrix data. For a large part, this read operation can be done as look-ahead, meaning that while the SpMV pipeline operates on one color, the vector partition data of the next color can already be read from the URAM. This data is then stored in a BRAM block in the internal read unit. However, after the SpMV pipeline completes, this vector partition data needs to be transferred to the vector partition memories of the SpMV pipeline, and the vector partition indices for the next color need to be read from the off-chip memory. This is overhead added by our choice to use sparstitioning. To determine how much this overhead slows down the overall performance, we added the option to the design to not use sparstitioning. This version of the design has as downside that it has a more limited maximum matrix size that it can operate on, as the complete multiplicand vector needs to be stored multiple times in the vector memories of the SpMV pipeline. The advantage is that these additional steps of reading vector partition indices and transferring vector partition data no longer need to occur.

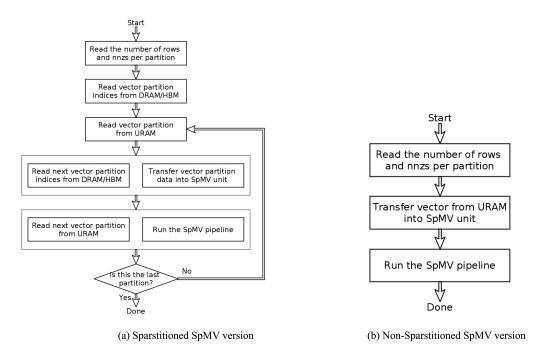

Fig. 5. Overview of the tasks in different SpMV unit implementations.

To visualize the difference in way of operating between the sparstitioned and the nonsparstitioned SpMV unit, Figure 5(a) shows the steps the sparstitioned SpMV unit takes, whereas Figure 5(b) shows those the non-sparstitioned SpMV unit takes. Tasks horizontally next to one another in these figures are performed at the same time. Obviously, the flow in Figure 5(b) is much simpler. Also note how in Figure 5(a) the reading of the next vector partition (and the reading of the indices to read from) are already done while the SpMV unit is still working on another partition. This hides the time these reads would normally take but also necessitates an additional memory to read the next vector partition into, and a step in which the data is transferred from this memory into the SpMV unit.

### 4.4 GPU SpMV Kernels

For the GPU, kernels in CUDA and OpenCL are tested. Only doubles are used for non-zero values. NVIDIA's cuSPARSE [18] features a blocked SpMV function called *cusparseDbsrmv()*. For OpenCL, Algorithm 1 from Eberhardt and Hoemmen [10] is used. In this algorithm, a warp of 32 threads is assigned to a single block row, and threads are assigned to elements in the block row. To cover the entire block row, a warp iterates, handling  $floor(32/bs^2)$  blocks at a time, where *bs* is the blocksize. A warp only operates on complete blocks, so some threads might be always idle. For  $3 \times 3$  blocks, a warp can cover three blocks with 27 threads and has 5 inactive threads. During initialization, a thread calculates the index of the block row, how many blocks the row has, and which block it is supposed to operate on. It also calculates its position within a block (row and column). Since a warp only covers complete blocks, a thread's assigned position in a block never changes. During iterating, it multiplies the target element from A with the value from *x*, adding the product to a running total. Once the whole block row is complete, threads with the same vertical position (row) in the blocks reduce the values in their local registers and write the reduced output to global memory. Reduction can be done with shuffling or via shared memory.

#### 5 SPARSE MATRIX SOLVER DESIGN

To expand the SpMV kernel into a kernel that can perform preconditioned BiCGStab, units to perform both the preconditioning and the vector operations need to be added. In this section, the design of those units is discussed, followed by a description of the complete design that links all units and performs the complete preconditioned solve.

#### 5.1 Applying the ILU0 Preconditioner

As shown in Algorithms 2 and 3, the basic structures of the SpMV and the forward and backward substitutions that the ILU0 application performs are similar. This, combined with the fact that the SpMV and ILU0 application are never active at the same time, since the result of one is needed to start the other, makes reusing the hardware of the SpMV unit for the ILU0 apply a desired feature to save resources. Unlike the SpMV, which goes through the matrix it operates on line by line, the ILU0 application goes through its LU matrix in a non-sequential order. First, it goes through all of the values below the diagonal top to bottom, and then it goes through all values above and including the diagonal bottom to top (last row first). This memory access pattern is not efficient to use on the FPGA, as it needs to read all LU matrix data twice, ignoring about half of it each time. Which data it needs to use and which it does not depends on the current row number and the column index. This memory access pattern is not only inefficient for the FPGA, but in general, so in our design the lower-triangular matrix L, the upper triangular matrix U, and the diagonal values are split from the LU matrix, which are used as three separate data structures. First, L is read to perform the forward substitution, and then U and the diag vals are read to perform the backward substitution. Since the latter step happens bottom to top, both the U matrix and the diag vals are stored in reverse order.

The main difference between the substitutions and the SpMV is that the substitutions modify the vector that they are operating on, whereas the SpMV does not. All rows that are grouped into the same color by GC can be in the pipeline at the same time, but between the colors, the results of the previous color need to be integrated into the vector that is currently being operated on. To achieve this, the results of the ILU0 application are not only written to the URAM vector memory but also forwarded directly into the vector partition memories so that they can be used during the next color, without requiring the unit to wait with reading its vector partition until the previous color finishes its computation.

There are additional operations that the forward and backward substitution needs to apply over the SpMV. For the forward substitution, this is a subtraction of the SpMV unit result from the p vector, and for the backward substitution, it is this subtraction followed by a division by the diagonal value. The ILU0 unit is added to the SpMV unit to perform these operations. The reading of the P vector can be done directly from the URAM, since that is where the P vector is stored during the ILU0 application. The diagonal vector is read from off-chip memory by the external read unit. Figure 6 shows how the original SpMV top level was modified to allow the unit to also apply the ILU0 preconditioning step. Note that this unit is not yet the top level of the complete solver.

#### 5.2 The Vector Operations

Over the course of a BiCGSTAB run, a number of vector operations of three different kinds need to be applied:

- A dot product, which calculates the inner product of two vectors.

- An axpy, which performs  $\alpha * \vec{x} + \vec{y}$ .

- A norm, which calculates the absolute value of a vector (i.e.,  $\sqrt{\vec{x} * \vec{x}}$ ).

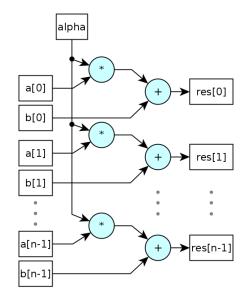

Fig. 6. Schematic of the SpMV/ILU0 unit.

Of these, the dot product and norm are very similar in structure, as a norm is the square root of an inner product of a vector with itself. All three operations are highly parallel and perform the same basic operations (one multiplication and one addition) for every element in their input vectors. For this reason, and to provide more flexibility in exploiting the task-level parallelism in the solver, we designed a unit that can perform either an axpy or a dot product. This dot\_axpy unit contains an equal number of multiply and add floating point units, which can be connected in different ways, depending on which function needs to be performed. When an axpy needs to be performed, the adders and multipliers are connected in parallel pipelines that each perform the axpy on one element of the input vectors at a time. For this function, an additional input port is used for the scaling constant  $\alpha$ , besides the two input vector and one output vector ports. Figure 7 gives an overview of how the adders and multipliers are arranged in the dot\_axpy unit when it performs an axpy operation.

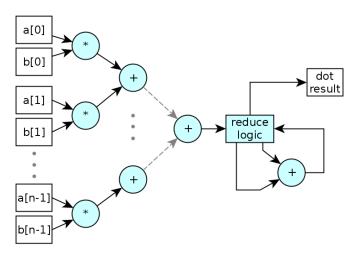

For the dot products, all multipliers work in parallel, the results of which are then added together into a single value by a tree of adders. The result of this adder tree is added together with the result of previous cycles in the final adder, which adds a new input to its most recent output. After the adder tree has processed all values of the input vectors, logic around the final adder continuously feeds two subsequent valid output of that adder back into it, until one singular final result is left. Figure 8 gives an overview of how the adders and multipliers are arranged in the dot\_axpy unit when it performs a dot product.

During the vector operations, a degree of task-level parallelism exists in the BiCGStab solver algorithm. This parallelism can be found in the following operations (using line numbers from Algorithm 1):

Fig. 7. Schematic overview of the dot\_axpy unit in axpy mode.

Fig. 8. Schematic overview of the dot\_axpy unit in *dot* mode.

- The vector subtraction in line 1 can be pipelined with the SpMV operation in that same line so that the subtraction of each element of  $\vec{b}$  happens as soon as the SpMV result in the same position as that element is done. The dot product in line 5 can be pipelined with the subtraction of line 1 in the same way.

- The two axpy operations in line 10 can be pipelined.

- The dot product in line 13 can be pipelined with the SpMV in line 12.

- The axpy operations in lines 15 and 16 can be done in parallel, and the dot product in line 17 can be pipelined with the axpy in line 16.

- The two dot products in line 23 can be done in parallel, and can both be pipelined with the SpMV in line 22.

• The axpy operations in lines 24 and 25 can be done in parallel. The dot product in line 26 can be pipelined with the axpy in line 25, and so can the dot product in line 8 in the following iteration.

Together, these instances of possible task-level parallelism cover all vector operations that the BiCGStab performs. The number of vector operations that can be performed in parallel in each of these instances is, in order: 2, 2, 1, 3, 2, and 4. The complete vector unit contains multiple dot\_axpy units to exploit this task-level parallelism; however, to avoid having dot\_axpy units being idle often, and to not increase the number of read/write ports too much (see Section 5.3), we choose to implement 2 dot\_axpy unit in the *vector operations* unit.

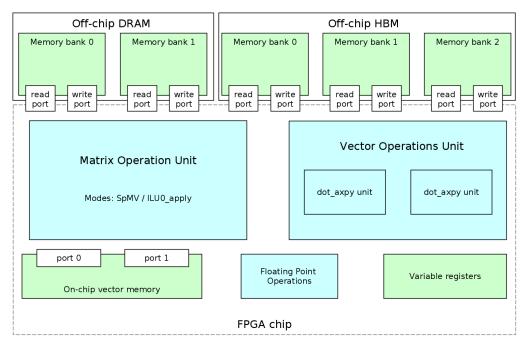

### 5.3 Read and Write Ports

The Xilinx Alveo U280 data center accelerator card has two different types of large memory that the FPGA chip is connected to: an off-chip DDR memory that consists of two 16-GB DDR4 memory banks, each of which is connected to the FPGA via a single read/write port, and an 8-GB on-chip HBM stack that is connected to the FPGA via 32 read/write ports. Each memory port is accessed at the kernel level either via a 512-bit wide AXI4 interface (for the DDR memory) or via a 256bit wide AXI3 interface (for the HBM). This memory architecture has led to the following design decisions:

- Reading and writing delays from/to the HBM are slightly shorter than those from/to the DDR memory, so all vectors (which all need to be read and written multiple times during the solver run) are stored in the HBM.

- To reduce the number of memories to which the host CPU needs to transfer its data, and to thereby reduce the initial data transfer time, all matrix data and the initial B vector are stored on the DDR memory.

- Some vector operations read from and write to the same vector—for example, the axpy in line 15 of Algorithm 1. To avoid conflicts and to make data buffering easier, each AXI port is used either to read or write, hence the *x*, *r*, and *p* vectors are stored in two memory locations connected to different ports. During an operation to update one of those vectors, it is read from the port that it was written to most recently, and written to the other port. This essentially makes use of the ping pong buffering technique used to stream data efficiently.

- All HBM ports are located on one of the two narrow sides of the FPGA chip (which has a rectangular shape), where the HBM crossbar and memory stack are located. Moreover, the FPGA is subdivided into three physical regions, each one being a single silicon die and called **Super Logic Region (SLR)**. Signals crossing these regions incur an additional delay compared to signals routed in the same SLR. Each instance of an AXI port (required to use an HBM port) comes with a cost in terms of routing (512 bits of data plus control bits) and BRAMs that are used for data buffering. The main factor for the design's logic to spill over to another SLR, causing the additional delays due to the signals crossing between SLRs to reach the HBM ports, is BRAM usage. To reduce such spilling, and to avoid routing congestion due to the high number of signals used by each AXI port, we choose to limit the number of HBM ports. We choose to use six HBM ports, because this number of read and write ports can be efficiently used during the vector operations.

- Since the width of the read ports is 512 bits, we design our computation pipelines to be able to accept one full cache line every cycle. For the HBM ports, which are natively 256-bit wide, we let the implementation tools to handle the AXI port width conversion. That means each dot\_axpy unit has eight double-precision multipliers and adders.

Fig. 9. Schematic overview of the complete solver design.

### 5.4 The Complete FPGA Solver

A top-level solver unit was designed to encompass both the SpMV/ILU0 unit and vector operations unit. This top-level unit instructs those units which tasks to perform and with which input/output vectors. It also regulates the access of both units to the URAM internal vector memory and handles filling of this memory during the initialization step of the solver. Figure 9 gives a schematic overview of the top-level unit of the BiCGStab solver kernel. To not overly complicate the figure, the signals between the units and the memory are not pictured. Besides the units already covered in the previous sections, the figure also shows a block of floating point operators and a memory for floating point variables. The operators are used to apply the operations that only need to be performed on a single value at a time, such as the square root of the norm calculation or the multiplications and division of the  $\beta$  calculation in line 9 of Algorithm 1. The memory is used to stored the results of these operations, and contains  $\alpha$ ,  $\beta$ ,  $\omega$ ,  $\rho$ ,  $\rho_{new}$  and conv\_threshold.

### 5.5 The GPU Solvers

For completeness of the evaluation and comparison of our work, we also developed a couple of GPU solvers using first CUDA and the NVIDIA's cuSPARSE library [18]. cuSPARSE has functions for vector operations like dot, axpy, and norm, as well as a blocked ILU0 preconditioner. Second, we also implemented the solver using OpenCL [17], where a similar structure to the CUDA is used, defining kernels for vector operations and applying the ILU0 preconditioner. One big difference is that the construction of the ILU0 preconditioner (the decomposition) is done on the CPU. This has not been implemented on GPU yet, whereas CUDA features an ILU0 decomposition on the GPU in cuSPARSE.

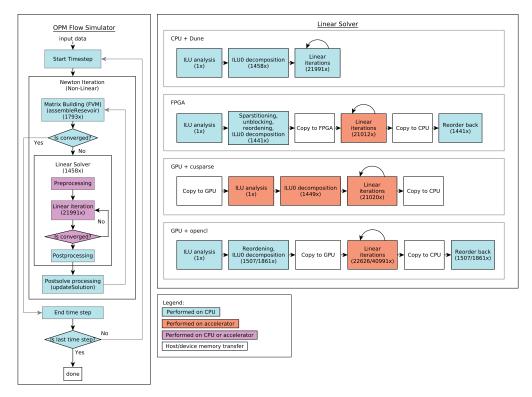

For a high-level overview of the complete flow simulator that will be used to integrate the different accelerated solvers, please refer to Figure 10.

Fig. 10. A block diagram representing the full flow simulator (left) and the different linear solver implementations (right). The numbers between brackets indicate how many times a function is performed for that implementation.

### 6 PERFORMANCE MODELING

To predict the performance of both the hardware design as it was in development as well as to gauge how well the design scales, we constructed a performance model that we run in Matlab. This model was made to emulate the data flowing through the computation units and to calculate how many clock cycles the execution would take. This section describes first what parts of the design are modeled and which are not, showing second the predicted modeling results.

### 6.1 Model Details

The performance model is composed of functions that model the individual hardware kernels: it has a function to estimate the performance of the SpMV, one for the ILU0, and one for the vector operations. To make the performance estimations as accurate as possible, the hardware models work on the same data that is sent to the kernel, including the partitioning data. The exception being that since the model does not actually perform the solving calculation, it does not read the non-zero matrix values or any vector data. Nevertheless, the partitioning and sparsity pattern information are needed to calculate the performance. Furthermore, the functions that calculate the performance of the ILU0\_apply and SpMV operations share the same structure, in the same way that those operations share the same module in the hardware kernel. These functions do the following for every color:

Hardware Acceleration of HPC CFD Using HBM FPGAs

- First, it calculates the time to transfer the vector partition data into the SpMV unit. It does this by dividing the number of values in the partition by the number of ports allocated to the internal URAM memory from which the partition is read.

- If apply\_ILU0 is performed, the function calculates the time the transfer of the P vector into the ILU0 unit memory would take in the manner described previously.

- Then, it calculates the time the SpMV pipeline takes. During this step, the function's emphasis is on the time the reading of the matrix data takes. It assumes a set bandwidth for each of three ports from which the three matrix arrays (non-zero values, column indices, and new row offsets) are read and simulates reading into three FIFOs at the speed set by that bandwidth. Whenever enough data is available in the FIFOs for all three arrays to fill an input line of the SpMV pipeline, that data is removed from the FIFOs.

- After enough data has been read from all three ports for the current color, and the simulated FIFOs are empty, a set delay is added for the SpMV pipeline to write back the result data. Since much less data needs to be written back than needed to be read, no delay beyond the regular write overhead of the final lines is deemed necessary.

- If apply\_ILU0 is performed, a set delay for the ILU0 unit is added, and the write delay is calculated with the on-chip URAM instead of an off-chip memory.

The cycle count results of all colors are added together to find the total number of clock cycles that the SpMV or apply\_ILU0 takes. The calculations done to estimate the cycle count of the vector operations are comparatively more simple but follow the same method: first the reading of data into FIFOs at a set bandwidth is modeled, data is removed from the FIFO whenever enough is in it to fill up a line of inputs of the vector operation unit, and finally, when all reading is done, the latency of the pipeline of the operation is added, as well as some writing overhead cycles for the axpy operation.

A top-level function adds together the cycle count results of apply\_ILU0, SpMV, and vector operations to get to a final estimate. This top-level function has a number of variables that can be changed to do domain space exploration and to assess the scalability of the kernel. These are as follows:

- The number of multipliers and adders in both the vector operation and SpMV/ILU0 units.

- The bandwidth to the off-chip memory in are located.

- The bandwidth to the on-chip URAM in number of ports (how many values of the vector stored on-chip can be read simultaneously).

- The delay of the adder and multiplier units

- The matrix that is modeled for, and how long the solve of that matrix takes, in iterations.

Please note that the largest source of performance uncertainty in the design is the time the memory operations take. Memory accesses do not happen at a constant pace, but in bursts, the size of which and the time between them may vary based on various factors related to the memory. As a result, the weakest part of the model is that it does not accurately capture this memory behavior. Similarly, it does not support modeling reading two arrays of data from the same port, nor the performance penalties from reading and writing on the same memory bank at the same time.

### 6.2 Modeling Results

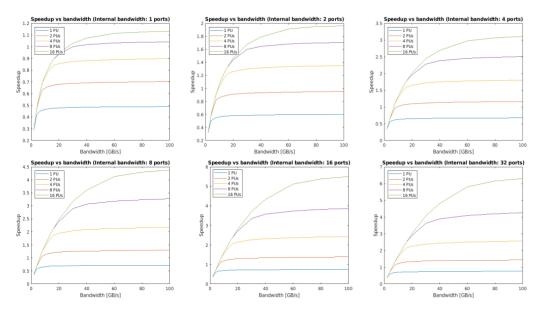

We use the model to analyze the scalability of the design and to understand what the critical points are in achieving the best performance. We perform a domain space exploration by varying the model parameters, starting with the number of adders and multipliers set at 2, increasing the bandwidth from 10 GB/s, and increasing the number of internal ports from 2. When a parameter

Fig. 11. Domain search exploration for the ILU0-BiCGStab solver. One internal port has a maximum bandwidth of around 18 GB/s at the current kernel frequency of 280 MHz. The configuration achieved in this work for the FPGA solver was two internal ports, eight PUs, and 50-GB/s external bandwidth. This corresponds to the parse line in the top middle figure that estimates a  $1.6\times$  speedup, which was confirmed by the experimental results presented next.

does not give a performance increase anymore, we switch to increase the new bottleneck parameter. We perform this exercise by increasing all parameters until a maximum value we select as an upper bound of a maximum practical boundary for our design. The limit for the number of PUs was set to 16 based on the hardware utilization results we obtained, especially the BRAM utilization (see Table 7). A total of 32 PUs might not be realistic as the BRAM utilization would be near 100%, which would make routing the design and meeting timing very challenging. For this number of PUs, 100 GB/s of bandwidth proved enough to approach the maximum performance for any of our models.

Figure 11 shows the modeling results. The first conclusion we can draw from these results is that the number of read ports to the internal vector memory has a major impact on the overall performance of the solver, even if we try to hide the time these memory accesses take. With only one port, barely any speedup can be achieved over the software implementation, whereas a speedup of more than 6× could be achieved with 32 ports, given enough bandwidth. This serves as an indication that the FPGA, with its ability to implement specialized memory infrastructure for multiple simultaneous random accesses, could achieve higher performances than we achieved in this work.

The second conclusion we draw from the modeling results is that doubling the PUs does not double the performance. We can attribute this to the increasing impact of the latency of the SpMV and ILU0 pipelines as the number of PUs increases. With a higher number of PUs, more data can go into the pipeline at the same time, decreasing the number of cycles that new data is fed into the pipeline while the latency of the pipeline stays the same. This effect is especially pronounced for the ILU0 solve steps, which have a longer pipeline, and the latency of which cannot be hidden by already starting operations on the next partition, because that computation depends on the results of the previous partition. Since doubling the number of PUs almost doubles the amount of logic and BRAMs used by the design, one must consider whether adding more PUs is worth the

|               | H                      | Host      |                       | Accelerator           |                       |  |  |

|---------------|------------------------|-----------|-----------------------|-----------------------|-----------------------|--|--|

| Short<br>Name | CPU                    | Frequency | Memory<br>(#Channels/ | Name                  | Memory (Bandwidth)    |  |  |

|               | (#Total Cores)         | ,         | Bandwidth)            |                       |                       |  |  |

| FPGA          | Xeon E5-2640V3 (16)    | 2.6 GHz   | DDR4-2133             | Xilinx Alveo U280     | DDR4+HBM (498 GB/s)   |  |  |

| ПОЛ           | Xcon LJ-2040 V J (10)  | 2.0 0112  | (4 / 59 GB/s)         | AIIIIX AIVeo 0200     | DDR4+11DW1 (490 OD/3) |  |  |

| $GPU^1$       | Xeon E5-2640V3 (16)    | 2.6 GHz   | DDR4-2133             | Nvidia K40m           | GDDR5 (288 GB/s)      |  |  |

| 010           | Acon 15 2010 \$ 5 (10) | 2.0 0112  | (4 / 59 GB/s)         |                       | GDDR3 (200 GD/3)      |  |  |

| $GPU^2$       | Xeon E5-2698V4 (40)    | 2.2 GHz   | DDR4-2400             | Nvidia V100-SXM2-16GB | HBM2 (900 GB/s)       |  |  |

| 010           | GFU Xeon E3-2098 (40)  |           | (4 / 77 GB/s)         |                       | 11DW12 (700 CD/3)     |  |  |

| CPU           | Xeon E5-2698V4 (40)    | 2.2 GHz   | DDR4-2400             |                       |                       |  |  |

|               | ACOII LJ-2090 V4 (40)  | 2.2 OI 12 | (4 / 77 GB/s)         | _                     |                       |  |  |

Table 2. Characteristics of the Platforms Used to Benchmark the Kernels

Table 3. SpMV Parameters of Different SpMV Implementations

| Parameter  | double_p | double_np | float_p | float_np |

|------------|----------|-----------|---------|----------|

| Num mults  | 8        | 8         | 16      | 16       |

| Max rows   | 262,144  | 65,536    | 262,144 | 65,536   |

| Read ports | 4        | 4         | 4       | 4        |

additional hardware resources, and the effort of having these resources meet timing. Perhaps more performance could be found more readily by improving the internal memory, as described earlier, or by reducing the apply\_ILU0 latency.

#### 7 EXPERIMENTAL RESULTS