**Delft University of Technology**

# Antenna-in-Package (AiP) Using Through-Polymer Vias (TPVs) for a 122-GHz Radar Chip

Yi, Hengqian ; Öztürk, E.; Koelink, Marco ; Krimmling, Jana ; Damian, Andrei A. ; Debski, Wojciech ; van Zeijl, H.W.; Zhang, Guoqi; Poelma, René H. **DOI**

10.1109/TCPMT.2022.3172618

Publication date 2022

**Document Version** Final published version

**Published in** IEEE Transactions on Components, Packaging and Manufacturing Technology

## Citation (APA)

Yi, H., Öztürk, E., Koelink, M., Krimmling, J., Damian, A. A., Debski, W., van Zeijl, H. W., Zhang, G., & Poelma, R. H. (2022). Antenna-in-Package (AiP) Using Through-Polymer Vias (TPVs) for a 122-GHz Radar Chip. *IEEE Transactions on Components, Packaging and Manufacturing Technology*, *12*(6), 893-901. Article 9795927. https://doi.org/10.1109/TCPMT.2022.3172618

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

#### Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

# 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Antenna-in-Package (AiP) Using Through-Polymer Vias (TPVs) for a 122-GHz Radar Chip

Hengqian Yi<sup>®</sup>, Efe Öztürk<sup>®</sup>, Marco Koelink<sup>®</sup>, Jana Krimmling, Andrei A. Damian, Wojciech Debski, *Member, IEEE*, H. W. van Zeijl, *Member, IEEE*, Guoqi Zhang<sup>®</sup>, *Fellow, IEEE*, and René H. Poelma, *Member, IEEE*

*Abstract*—High-performance IC-to-antenna interconnection is one of the key enablers for the mass production of high-end millimeter wave (mmW) radar systems above 100 GHz. In this work, a radar system with an on-package antenna array working at 122 GHz is presented. The antenna is placed on top of the molded package and the antenna-to-chip interconnection is realized by through-polymer via (TPV) technology. The detailed fabrication process of the radar antenna-in-package (AiP) with TPV is discussed. The results from the functional tests of the radar AiP are presented and benchmarked to a commercial quadflat no-leads (QFN) package with an open antenna cavity. The detection margin between the echo signal and the constant false alarm rate (CFAR) threshold is approximately 10 dB higher for the TPV radar AiP compared with the benchmarked commercial QFN package.

Index Terms—0.13- $\mu$ m silicon germanium bipolar complementary metal-oxide semiconductor (SiGe BiCMOS), film-assisted molding, metalized polymer, monostatic frequencymodulated continuous-wave (FMCW) radar, patch antennas, radar antenna-in-package (AiP), SU-8, system-in-package (SiP), through-polymer via (TPV).

#### I. INTRODUCTION

THE development of silicon germanium bipolar complementary metal-oxide semiconductor (SiGe BiCMOS) technology has enabled the monolithic integration of state-ofthe-art system-on-chip transceivers in the *G*-band frequency range (110–300 GHz). All RF signals are kept inside the

Manuscript received November 30, 2020; revised August 8, 2021; accepted April 8, 2022. Date of publication June 14, 2022; date of current version June 24, 2022. This work was supported by the Dutch National Funding Nederlandse Organisatie voor Wetenschappelijk Onderzoek (NWO), in TTW Section under Project 13921. Recommended for publication by Associate Editor K. J. Han upon evaluation of reviewers' comments. (*Corresponding author: René H. Poelma.*)

Hengqian Yi, H. W. van Zeijl, and Guoqi Zhang are with the Department of Microelectronics, Delft University of Technology, 2600 AA Delft, The Netherlands (e-mail: h.yi@tudelft.nl).

Efe Öztürk, Jana Krimmling, and Wojciech Debski are with the Silicon Radar GmbH, 15236 Frankfurt (Oder), Germany (e-mail: oeztuerk@siliconradar.com).

Marco Koelink is with the Chip Integration Technology Center (CITC), Novio Tech Campus, 6534 AT Nijmegen, The Netherlands (e-mail: marco.koelink@citc.org).

Andrei A. Damian is with the NXP, 6534 AE Nijmegen, The Netherlands (e-mail: andrei.damian@nxp.com).

René H. Poelma is with the Department of Microelectronics, Delft University of Technology, 2600 AA Delft, The Netherlands, and also with the Packaging Research Department, Nexperia B.V., 6534 AB Nijmegen, The Netherlands (e-mail: r.h.poelma@tudelft.nl).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TCPMT.2022.3172618.

Digital Object Identifier 10.1109/TCPMT.2022.3172618

chip except the signals from the chip to its antennas. Due to the increasing application frequencies, the influence of undesired parasitic electromagnetic interference introduced by the manufacturing limitations of the interconnects is becoming more pronounced [1], [2].

Due to the size reduction of the antennas with increasing frequency, the integration of antennas into the IC package is becoming possible and beneficial at frequencies above 100 GHz. Many antenna-in-package (AiP) concepts are developed recently using different packaging technologies, including quad-flat no-leads (QFN) with wire bonding, embedded wafer-level ball grid array (eWLB), and low temperature co-fired ceramics (LTCC).

For the QFN packaging solutions, wire bonding is used for the IC-to-antenna interconnection. Since the mm wavelength becomes comparable to the wire bond length, the wire bond introduces uncontrollable parasitic effects with its corresponding manufacturing tolerances [3]-[5]. To meet the RF requirement, the wire bonding process becomes costly, time-consuming, and yields limited performance improvement. eWLB technology allows antennas to be connected to the IC by the redistribution layer (RDL) [6]-[11]. However, the antennas are placed on the side of the IC which limits the area that can be used for the antenna fabrication. Furthermore, the chip is not placed in direct contact with any thermally conductive plane which is a disadvantage for high-power monolithic microwave integrated circuit (MMIC) applications. LTCC packages are advantageous for their low loss tangent, high thermal conductivity, and low thermal expansion coefficient (CTE) [12]–[14]. However, the co-fire temperature is much higher than the temperature that the Si circuit can withstand. Thus, the antenna substrate is fabricated separately and assembled afterward adding extra steps in the package fabrication. In addition, metal patterns made in the LTCC process have relatively large surface roughness which is not desired in mm-wave applications.

New package solutions for mm-wave frequency radar systems are needed. One promising package solution is to create a radar package with its antennas placed on top of the molded QFN package and connected vertically to the radar IC. In this case, additional fabrication, assembly, and wire-bonding of an external antenna substrate are avoided. Moreover, the length of electrical interconnection can be reduced to the thickness of the epoxy molding compound (EMC) layer. The antennas are patterned on top of the EMC; hence, the package can be further

2156-3950 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information. miniaturized when compared to other packaging solutions. Additionally, the IC can be bonded directly to a metal plate for improved heat dissipation. Therefore, the advantages of such radar AiPs are shorter electrical interconnection, a simpler fabrication process, finer antenna features, smaller footprints, and compatibility with high-power MMICs.

Conventionally, a vertical interconnection can be made through a molded package by laser drilling followed by Cu plating or solder filling of the drilled hole. This technology is called through mold via (TMV) [15]-[17]. The disadvantages of TMV include the damage of the substrate by laser, contamination of burned epoxy, thermal damage, limited aspect ratio and density, and poor sidewall control. As a novel technology for through package vertical interconnection, through-polymer via (TPV) takes an unconventional approach [18]. Instead of a laser drilling process, metalized polymer pillars are produced on the substrate, such as a wafer, before the epoxy molding process which is a bottom-up approach. The pillars are highaspect-ratio extensions of the top layer interconnects on the chip. Next, the substrate with pillars is molded using filmassisted transfer molding (FAM) technology [19]-[22]. In a FAM process, the mold parts are covered by plastic films fixed by vacuum. When the mold parts are closed prior to the injection of the molding compound, the top side of a metalized polymer pillar is in contact with the top mold and is slightly pressed into the soft plastic film. When the molding compound is injected into the mold, the top side of the pillars is then sealed by the film. Hence the FAM process keeps the top side of the metalized polymer pillars clean of the molding compound and enables further processing of the antennas. Compared with TMV, TPV is a lower-cost and cleaner process. It does no damage to the substrate and is suitable for scale-down and high-density fan-out. Furthermore, the TPVs are made by a lithographic process, which enables high precision, free form factor, and high-volume wafer-level production capabilities.

In this research, we demonstrated an AiP solution for a 122-GHz radar system with an on-package antenna array using TPVs as the IC-to-antenna interconnections. In Section II, the radar IC and the AiP solution are introduced. Then the antenna design and the simulation results are discussed in Section III. Furthermore, the fabrication process is explained and the results are shown in Section IV. Finally, the functional test results of the radar AiP are presented in Section V. The performance of a commercial radar AiP using open cavity and wire bonding with the same IC and same antenna array is compared with our work.

#### II. RADAR IC AND PACKAGING DESIGN

#### A. Radar IC and Its Layout

The radar IC is manufactured by SiGe technology with the 0.13- $\mu$ m BiCMOS process [23]–[27]. The radar IC operates at 122-GHz industrial, scientific, medical (ISM) band and is designed for highly accurate short-distance measurement. It consists of a push-push type voltage-controlled oscillator (VCO), a power amplifier, an in-phase-quadrature receiver chain, a 1/32 frequency divider, an external phase-locked loop

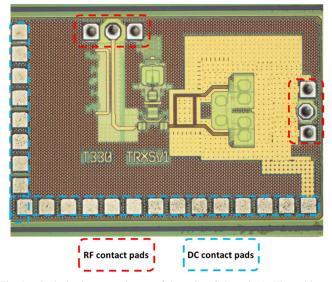

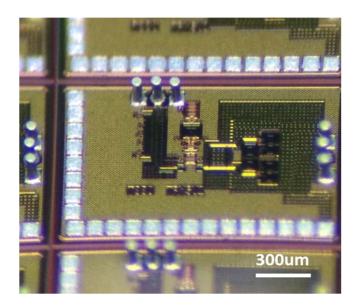

Fig. 1. Optical microscopy image of the radar IC (top-view). The red boxes indicate the RF contact pads and the blue boxes indicate the dc contact pads.

(PLL), several temperature sensors, and power detectors. The VCO can tune the signal frequency from 120.6 to 124.3 GHz.

Before reaching the antenna array, the signal is boosted by a power amplifier and around 0 dBm of output power could be achieved. The radar IC occupies a total chip area of 940 × 1450  $\mu$ m with 22 contact pads for interconnection with the QFN package and six RF contact pads for the interconnection with its antennas. A top view of the radar IC is shown in Fig. 1. The three contact pads on the top side of the IC are connected to the transmitter antennas and the other three contact pads on the right side of the IC are connected to the receiver antennas as indicated by the annotations in Fig. 1. The total power consumption of the radar IC is around 450 mW which is supplied with a single 3.3-V source [23].

#### B. Packaging Design Using TPVs

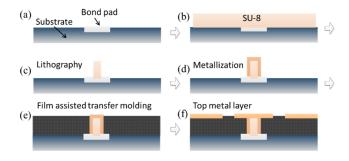

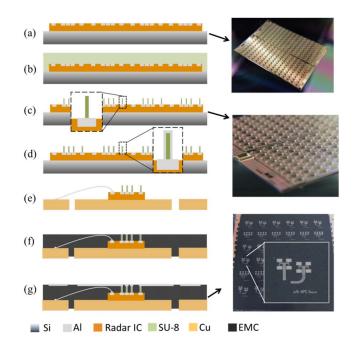

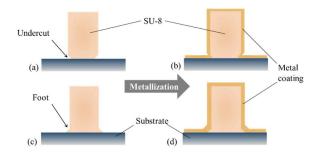

In our proposed packaging solution, the electrical interconnections between the radar IC and the antenna array are realized with TPVs instead of wire bonds. The main process steps of the TPV technology are shown in Fig. 2. First, a substrate is coated with a layer of polymer material, such as a photoresist. Then, the polymer layer is patterned into the desired high aspect ratio polymer pillars. The polymer pillars are coated with a metal layer for electrical conductivity. A FAM molding process is carried out afterward to encapsulate the substrate with the top side of the metalized pillars exposed. Finally, a metal layer can be added to the top of the encapsulated package.

The polymer material used in the process is SU-8 negative resist [28]–[30]. SU-8 is epoxy-based and therefore suitable for permanent use and compatible with the thermal budget requirements for transfer molding and soldering [30]. Furthermore, the SU-8 photoresist enables the fabrication of high aspect ratio structures [28].

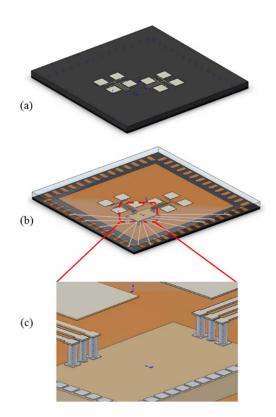

The 3-D schematic of the radar AiP using TPVs for chipto-antenna interconnections is shown in Fig. 3. The EMC is shown transparent in Fig. 3(b) and (c) to view the embedded

Fig. 2. Illustration of the main process steps of TPV fabrication. (a) Substrate with contact pads. (b) Coating of SU-8 layer on the substrate. (c) Patterning SU-8 via lithography. (d) Metallization of SU-8 pillars. (e) Molding process. (f) Top metal layer deposition.

Fig. 3. Schematic of the proposed package design. (a) QFN package with antennas on top. (b) Mold compound is made transparent to view the TPVs. (c) Zoomed-in view on the TPVs.

IC, wire bonds, and TPVs. Wire bonds are still in use for interconnecting the non-RF I/Os on the Radar IC to the QFN package lead frame. The minimum thickness of the molded EMC layer is in this particular design limited by the loop height of the wire bonds. The thickness of EMC above the radar IC requires a minimum of 150  $\mu$ m to keep the wire bonds sufficiently shielded. Hence the TPVs are designed to be 150  $\mu$ m in height. According to the position and dimension of the contact pads, the diameter and the pitch size of the SU-8 pillars are determined to be 40 and 100  $\mu$ m, respectively. The SU-8 pillars are conformably coated with Al (1%Si) alloy by sputtering to match the metallization of the contact pads of the die. A thickness of 2.5  $\mu$ m is chosen for sufficient electrical conductance and step coverage. The skin effect depth of Al at the working frequency of 122 GHz is 0.23  $\mu$ m. Thus, the

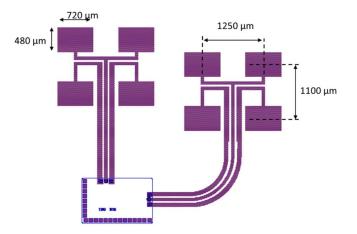

Fig. 4. Patch array antenna design using a GCPW feeding network and the dimensions of the patch elements.

electrical conductance of the TPVs, in this case, is limited by the skin effect rather than the metal coating thickness. The metalized SU-8 pillars have a diameter of 45  $\mu$ m, and an aspect ratio of 10:3. For the package housing, an 8 × 8 mm QFN is used, the same as the benchmarked commercially AiP [31].

### III. ANTENNA DESIGN

Patch array antenna structures are designed for the first fabricated radar packages. The antenna design uses a grounded coplanar waveguide (GCPW) as the feeding network [32], as shown in Fig. 4. The GCPW feeding lines are chosen instead of microstrip (MS) lines because they match with the on-chip GCPW networks, and no transition from the ground-signal-ground (GSG) pads to MS lines is required. Additionally, by using GCPW lines, the complete feeding network is realized in between the antenna elements which optimizes the space usage. The GCPW-fed antenna uses three vias for the GSG interconnection. The patch element has a height of 480  $\mu$ m and a width of 720  $\mu$ m. The pitches between the patch elements are 1250  $\mu$ m in the horizontal direction and 1100  $\mu$ m in the vertical direction. The vias and the feeding lines are designed for an optimized impedance matching. The die-attachment pad of the QFN which is about 300  $\mu$ m away from the antenna is used as the antenna reflector. The  $\varepsilon'$  and  $\tan\!\delta$  of the EMC material used in this work are 3.6 and 0.01 measured at 100 GHz according to the material manufacturer. The  $2 \times 2$  patches could reach around 13 dBi of directivity. With the additional matching network and efficiency drop due to the substrate, the gain would eventually reduce.

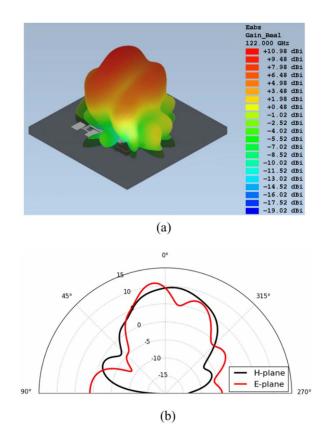

The simulations are completed using a full 3-D EM model of the package with EMPIRE 3-D software. The full 3-D EM model includes the antenna array, the TPVs, the GCPW lines, the radar chip, and the QFN package. The results of the radiation pattern and the realized gain in the E-/H-plane are shown in Fig. 5. The impedance matching design in the simulation is more straightforward when using TPVs when compared to wire bonds which reduce the cost of computation time and design effort. According to the results, the antenna

Fig. 5. Simulation results of the antenna utilizing GPCW matching network showing (a) 3-D radiation pattern and (b) more than 10-dBi gain in E-/H-plane at 122 GHz of operation frequency.

could provide more than 10 dBi of realized gain through the whole IC operation band. The beam tilt could be eliminated by correcting the antenna position on the package in future work. The antenna simulation has shown similar results compared to the design used in the commercial package with wire bonds [32].

## IV. PACKAGE FABRICATION

#### A. Fabrication Process

The TPV process can be a wafer or panel-level process. The 200-mm radar wafers are diced in tiles of  $24 \times 19$  mm. Each tile contains 270 radar ICs. The tile is mounted on a 4-in silicon carrier wafer using a temporary bonding layer. This allows the samples to be handled in the Else Kooi Lab (EKL), TUDelft cleanroom facilities. After the fabrication of TPVs, the wafer tile is removed from the carrier wafer by a thermal releasing process. Compared to the commercial package, the length of the RF interconnection is reduced from a wire bond length of 350  $\mu$ m to a TPV height of 150  $\mu$ m. The shorter electrical length reduces the inductive parasitic effect which is critical in millimeter-wave radar systems.

A detailed process flow is presented in Fig. 6. First, the wafer tile is bonded onto a silicon carrier wafer. The temporary bonding material used is poly (propylene carbonate) [33], [34]. Since the wafer tile is  $150-\mu$ m thick, a  $300-\mu$ m thick SU-8 layer is spin-coated at a spin speed of 500 r/min for 60 s so that the thickness of the SU-8 above the radar IC is around

Fig. 6. (Left) Schematic of the fabrication process flow of the proposed radar package. (Right) Images showing the intermediate fabrication results. (a) Assembly of the radar IC tile onto a silicon carrier wafer. (b) Spin coating of SU-8 resist. (c) Exposure and development of the SU-8 layer to obtain polymer pillars. (d) Metallization of polymer pillars and patterning of the metal layer. (e) Assembly of the singulated radar ICs onto a QFN substrate, including pick & place and wire-bonding steps. Each QFN panel was assembled with 36 radar ICs. (f) Film-assisted molding of the QFN substrate. (g) Metallization on top of the molded QFN and patterning of antenna structures. The schematic shown is not to scale. Following (g), the dicing of the QFN panel is performed to obtain individual radar AiPs.

150  $\mu$ m. After the spin coating, a soft baking step is applied to evaporate the solvent and solidify the SU-8 film. The exposure of SU-8 is carried out on an EVG 420 mask aligner with an exposure dose of 885 mJ/cm<sup>2</sup> followed by a post-exposure bake (PEB) step. The PEB process was carried out on a hotplate and consists of two stages. The first stage of PEB is a low-temperature bake at 65 °C for 5 min. The second stage of PEB is a higher temperature bake at 110 °C for 10 min. The SU-8 layer is developed in propylene glycol methyl ether acetate (PGMEA). During development, the wafer is placed in a wafer carrier facing down in the PGMEA solution. Gentle agitation is provided by a magnetic rotor. A low-power plasma flash is applied to remove the remaining residue of SU-8 after the development process. A hard baking step in a vacuum oven is carried out before metallization which helps the SU-8 to further cross-link and degas thoroughly. A hard baking temperature of 180 °C which is higher than the molding temperature is used to ensure the thermal stability of the polymer core during the molding process.

After hard baking, sputtering of  $2.5 - \mu m$  thick Al with 1% Si layer is performed. During the sputtering process, the wafer holder is kept at 25 °C, however, the temperature at the surface of the wafer can rise above the glass transition temperature with continuous deposition. Hence, a cooling step is inserted after every 156-nm-thick deposition. In this way, the sputtering process induces no damage to the SU-8 pillars.

Fig. 7. View of metalized SU-8 pillars fabricated on the radar IC under an optical microscope.

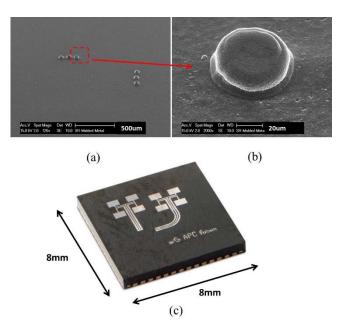

Fig. 8. (a) Protruding top surface of a TPV after FAM. (b) Close-up view. (c) Picture of the fabricated radar AiP with on-package antenna array using TPVs as the antenna-to-IC interconnection after package singulation.

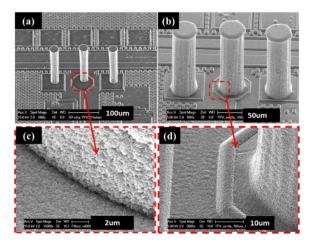

The fabrication results of metalized SU-8 pillars on the radar IC are shown in Fig. 7. The wafer tile containing the radar ICs is removed from the carrier wafer and diced into single chips. The removal of the IC is achieved by heating the wafer up to 180 °C to soften the PPC layer and then sliding the IC off the carrier wafer. The singulated radar chips with metalized pillars are then picked up and placed onto a QFN panel in a  $6 \times 6$  array. An automated wire bonder connects the remaining radar IC contact pads to the QFN panel using Al wire bonds. The entire panel is then molded using film-assisted molding which keeps the top surface of the metalized pillars of TPVs.

The last step is to fabricate the antenna arrays and the feeding networks on top of the encapsulated QFN panel. The antennas are created using front-end semiconductor manufacturing technology combined with film-assisted molding. Using FAM, the radar IC is encapsulated inside the EMC while keeping the top surface of the TPVs clean, as shown in Fig. 8(a) and (b). Before the metallization, a cleaning process is applied to the surface of the EMC molded QFN panel to remove any contamination and improve adhesion. Next, metallization of the entire QFN panel is carried out to form the antenna layer using sputtered Al (1%Si) to match the metallization of the TPV coating. The Al layer is masked and patterned using lithography and etching techniques. A photoresist layer is spin-coated on the surface of the metalized QFN panel. The antenna patterns are exposed on the photoresist layer and developed, followed by Al wet etching. After the resist removal by acetone, the antenna structures are completed and connected to the IC through the TPVs. An example of the fabricated radar AiP is shown in Fig. 8(c).

A miniaturized package could be achieved since the antennas are placed directly above the IC. For radar systems working at even higher frequencies, the dimension of the antenna will reduce further to be comparable to or even smaller than the size of the chip. This enables chip-scale or wafer-level packaging of radar systems with the antenna arrays on top.

#### B. TPV Profile Optimization

Good adhesion of the TPV pillars on the substrate is critical. For instance, during the dicing process of the wafer tiles, the TPVs are subjected to a high-pressure water jet from the dicing tool. The profile of the interface between the TPVs and the substrate has a decisive influence on the adhesion of the metalized pillars toward the contact pad material, and the step coverage of the metal coating. We improved the interface profiles of SU-8 pillars from an undercut profile to a foot profile, as shown in Fig. 9. SU-8 pillars with an undercut profile have smaller footprints while SU-8 pillars with a foot profile have larger footprints and no undercut. Because the resist material is exposed from the top, the lower parts of the film receive less exposure energy and are therefore less crosslinked. Under nominal process conditions (95 °C PEB and then development), an undercut profile at the interface is obtained. The adhesion of TPVs with the undercut profile is proven not sufficiently strong to survive the water jet from the dicing tool.

To obtain a foot profile, the exposure energy is kept the same, however, the PEB temperature was increased from 95 °C to 110 °C. Because the PEB step was carried out on a hotplate, the resist material at the interface receives more thermal energy. Consequently, in this area the thermally induced crosslinking is more effective which leads to the desired foot profile. The high-resolution SEM images of the resulting undercut and foot profiles of TPVs are shown in Fig. 10.

Fig. 9. Schematic illustration of the two different interface profiles between TPVs and substrate. (a) Undercut profile after SU-8 development. (b) Undercut profile after metalization. (c) Foot profile after SU-8 development. (d) Foot profile after metalization.

Fig. 10. SEM images of metalized SU-8 pillars on the radar IC bond pads. Shows foot profile (a) A and (b) B.

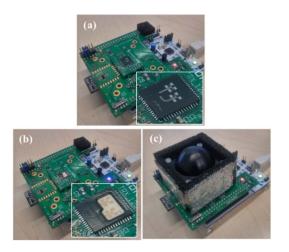

Fig. 11. Images of the fabricated radar package with TPVs and the commercial package assembled on the same test kit. The test kit loaded with the QFN AiP using TPVs with GCPW-fed patch array antenna is shown in (a). Test kit loaded with the open cavity QFN AiP is shown in (b). (c) Shows the test kit assembled with an RF lens.

#### V. RADAR FUNCTIONAL TEST

To characterize the functional performance, the fabricated radar AiPs using TPV technology were assembled on a test kit at Silicon Radar GmbH, Frankfurt (Oder), Germany. The radar AiPs using TPVs under test is shown in Fig. 11(a). A commercially available radar AiP with open cavity and

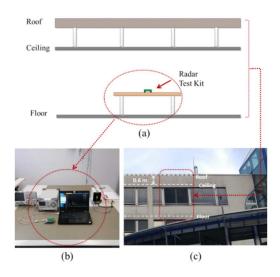

Fig. 12. Schematic of the test environment. Both the ceiling and the roof of the building were used as targets. (a) Schematic illustration of the test setup. (b) Measurement setup. (c) Photograph of the detected building features.

wire bonding was also measured to provide a reference for the performance, shown in Fig. 11(b). In this commercial package, antennas were fabricated on a substrate called Rogers ULTRALAM 3850 which has low permittivity and low losses up to the millimeter-wave range [32]. In the commercial package, the antennas are connected to the radar IC by 3 Al bond wires with a wedge-to-wedge technique. The test kit consists of three main parts, the radar package frontend under test, a baseband PCB assembly, and an additional plastic lens with lateral shielding. The additional lens and lateral shielding are used to enhance the signal and reduce side lobes. The test kit was fixed by glue on the table to make sure the position of the tested packages and RF lens could not change between measurements.

The radar test kit operates with a frequency modulated continuous wave (FMCW) principle using the constant false alarm rate (CFAR) mechanism for determining the detection threshold. An adaptive threshold can be calculated by keeping the probability of false alarms constant while the noise background is continuously changing [35]. The frequency of the signal is centered at 122 GHz. A bandwidth of 4500 MHz and 1024 fast Fourier transform (FFT) data acquisition were used to obtain an optimized detection accuracy of 19.4 mm with a maximum measurement range of 10 m. The radar signal was beamed toward the ceiling. A schematic illustration of the measurement environment is shown in Fig. 12.

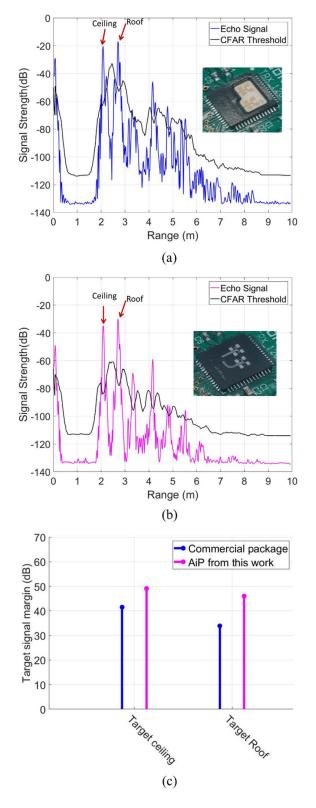

The echo signal strength and the CFAR threshold curve are plotted over the measurement range for both radar AiPs, as shown in Fig. 13(a) and (b). The measurements were carried out with a refresh rate of around 10 Hz, which generated ten sets of echo signal strength and CFAR threshold values in one second. The plotted curves are the average of the ten measured datasets. An object is considered detected when a peak is observed in the echo signal strength above the CFAR threshold curve.

According to the measurement results, objects at distances of 2.1 and 2.7 m are detected. The object detected at 2.1 m away corresponds to the ceiling, while at 2.7 m away it

Fig. 13. (a) Echo signal and CFAR threshold measured from the open cavity QFN AiP plotted over the detection range. (b) Echo signal and CFAR threshold of the QFN AiP using TPVs with GCPW-fed antenna plotted against distance. (c) Comparison of the detected target signal margin of the first two targets, the ceiling and the roof, measured by both AiPs.

corresponds to the roof of the building. Both radar AiPs under test captured the objects with a clear echo signal. The conventional AiP using wire-bonding and open cavity receives echo signals with strengths of -21 and -17 dB at 2.1 and 2.7 m, respectively. The AiP using TPVs with a GCPW-fed antenna receives an echo signal with a strength of -35 and -30 dB.

However, comparing the measured echo signal strength with the CFAR threshold, the target signal margins obtained by the conventional AiP are around 41.51 and 33.89 dB at the two targets. The target signal margins obtained by the AiP using TPVs are around 49.09 and 46 dB which are 7.5 and 12.1 dB higher than the conventional AiP, as shown in Fig. 13(c). This indicates the AiP using TPVs distinguishes the echo signals better from the background noise. The TPV interconnection which is shorter in length and lower in parasitic effect compared to the wire bonds contributes to the low noise performance.

The functional RF performance of the radar systems using the TPV packaging solution is superior to the conventional package. The prototype packages detect targets at similar accuracy with a lower noise level compared to the commercial package. The relatively higher loss observed in echo signals can be improved by optimizing both the impedance matching and the substrate material properties.

#### VI. CONCLUSION

In this work, we have presented a 122-GHz radar system with an on-package antenna array using TPVs as the IC-toantenna interconnections. The length of the electrical connection of the IC-to-antenna interconnection is reduced to an average of 150  $\mu$ m. The antenna array is placed on top of the IC which enables the miniaturization of the footprint of mm-wave radar AiPs. The antenna layer is fabricated directly on the EMC as the substrate which saves the cost of extra antenna substrates. By tuning process temperatures, the robustness of the TPVs in the following dicing and molding process was optimized. The final packages are tested with FMCW measurements. The performance of the radar AiP using TPVs is benchmarked with the radar AiP using wire bonds. The TPV interconnection shows a better noise performance compared to the wire bonds. The margin between the echo signal and the CFAR threshold curve at the detection peak of an object is 10 dB higher on average measured by the radar AiP using TPVs.

#### ACKNOWLEDGMENT

The authors would like to thank the staff from EKL, TUDelft, Delft, The Netherlands, for the laboratory support. The authors would like to thank Eef Boschman, Frank Boschman, Ritianne Camilleri, and Frank Pauw from Boschman Advanced Packaging Technology. B.V., Duiven, The Netherlands, who have helped with dicing, pick and place, and wire bonding, and also Jan Gulpen from NXP for his advice.

#### REFERENCES

T. Zwick, F. Boes, B. Göttel, A. Bhutani, and M. Pauli, "Pea-sized mmW transceivers: QFN-based packaging concepts for millimeter-wave transceivers," *IEEE Microw. Mag.*, vol. 18, no. 6, pp. 79–89, Sep./Oct. 2017, doi: 10.1109/MMM.2017.2712020.

- [2] E. Ozturk *et al.*, "Measuring target range and velocity: Developments in chip, antenna, and packaging technologies for 60-GHz and 122-GHz industrial radars," *IEEE Microw. Mag.*, vol. 18, no. 7, pp. 26–39, Nov. 2017, doi: 10.1109/MMM.2017.2738468.

- [3] J. Lim, D. Kwon, J. S. Rieh, S. W. Kim, and S. W. Hwang, "RF characterization and modeling of various wire bond transitions," *IEEE Trans. Adv. Packag.*, vol. 28, no. 4, pp. 772–778, Nov. 2005, doi: 10.1109/TADVP.2005.853554.

- [4] A. Sutono, N. G. Cafaro, J. Laskar, and M. M. Tentzeris, "Experimental modeling, repeatability investigation and optimization of microwave bond wire interconnects," *IEEE Trans. Adv. Packag.*, vol. 24, no. 4, pp. 595–603, Nov. 2001, doi: 10.1109/6040.982850.

- [5] Y. P. Zhang, M. Sun, K. M. Chua, L. L. Wai, and D. Liu, "Antennain-package design for wirebond interconnection to highly integrated 60-GHz radios," *IEEE Trans. Antennas Propag.*, vol. 57, no. 10, pp. 2842–2852, Oct. 2009, doi: 10.1109/TAP.2009.2029290.

- [6] M. Frank *et al.*, "Antenna and package design for 61- and 122-GHz radar sensors in embedded wafer-level ball grid array technology," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 12, pp. 5156–5168, Dec. 2018.

- M. Wojnowski *et al.*, "Embedded wafer level ball grid array (eWLB) technology for millimeter-wave applications," in *Proc. IEEE 13th Electron. Packag. Technol. Conf.*, Dec. 2011, pp. 423–429, doi: 10.1109/EPTC.2011.6184458. [Online]. Available: https://ieeexplore.ieee.org/ielx5/6178148/6184374/06184458. pdf?tp=&arnumber=6184458&isnumber=6184374

- [8] M. Wojnowski, C. Wagner, R. Lachner, J. Bock, G. Sommer, and K. Pressel, "A 77-GHz SiGe single-chip four-channel transceiver module with integrated antennas in embedded wafer-level BGA package," in *Proc. IEEE 62nd Electron. Compon. Technol. Conf.*, May 2012, pp. 1027–1032, doi: 10.1109/ECTC.2012.6248962.

- [9] M. PourMousavi, M. Wojnowski, R. Agethen, R. Weigel, and A. Hagelauer, "The impact of embedded wafer level BGA package on the antenna performance," in *Proc. IEEE-APS Topical Conf. Antennas Propag. Wireless Commun. (APWC)*, Sep. 2013, pp. 828–831, doi: 10.1109/APWC.2013.6624913. [Online]. Available: https://ieeexplore.ieee.org/ielx7/6607256/6624859/06624913. pdf?tp=&arnumber=6624913&isnumber=6624859

- [10] M. Wojnowski and K. Pressel, "Embedded wafer level ball grid array (eWLB) technology for high-frequency system-inpackage applications," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2013, pp. 1–4, doi: 10.1109/MWSYM.2013.6697745. [Online]. Available: https://ieeexplore.ieee.org/ielx7/6684335/6697324/ 06697745.pdf?tp=&arnumber=6697745&isnumber=6697324

- [11] A. Fischer, Z. Tong, A. Hamidipour, L. Maurer, and A. Stelzer, "77-GHz multi-channel radar transceiver with antenna in package," *IEEE Trans. Antennas Propag.*, vol. 62, no. 3, pp. 1386–1394, Mar. 2014, doi: 10.1109/TAP.2013.2294206.

- [12] A. Bhutani *et al.*, "122 GHz aperture-coupled stacked patch microstrip antenna in LTCC technology," in *Proc. 10th Eur. Conf. Antennas Propag. (EuCAP)*, Apr. 2016, pp. 1–5, doi: 10.1109/EuCAP.2016.7481147. [Online]. Available: https://ieeexplore.ieee.org/document/7481147/

- [13] A. Bhutani, B. Gottel, A. Lipp, and T. Zwick, "Packaging solution based on low-temperature cofired ceramic technology for frequencies beyond 100 GHz," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 9, no. 5, pp. 945–954, May 2019, doi: 10.1109/TCPMT.2018.2882062.

- [14] Y. Zhang and J. Mao, "An overview of the development of antenna-in-package technology for highly integrated wireless devices," *Proc. IEEE*, vol. 107, no. 11, pp. 2265–2280, Nov. 2019, doi: 10.1109/JPROC.2019.2933267.

- [15] T. Braun et al., "3D stacking approaches for mold embedded packages," in Proc. 18th Eur. Microelectron. Packag. Conf., Sep. 2011, pp. 1–8.

- [16] S. W. Ho et al., "Through mold interconnects for fan-out wafer level package," in Proc. IEEE 18th Electron. Packag. Technol. Conf. (EPTC), Nov. 2016, pp. 51–56, doi: 10.1109/EPTC.2016.7861441. [Online]. Available: https://ieeexplore.ieee.org/ielx7/7840091/7861428/ 07861441.pdf?tp=&arnumber=7861441&isnumber=7861428&ref=

- [17] T. Braun et al., "Through mold via technology for multi-sensor stacking," in Proc. IEEE 14th Electron. Packag. Technol. Conf. (EPTC), Dec. 2012, pp. 316–321, doi: 10.1109/EPTC.2012.6507099. [Online]. Available: http://ieeexplore.ieee.org/ielx7/6504698/6507037/ 06507099.pdf?tp=&arnumber=6507099&isnumber=6507037

- [18] M. Kengen, R. H. Poelma, H. M. V. Zeijl, A. V. Weelden, and E. Boschman, *Through-Polymer-Via for 3D Heterogeneous Integration and Packaging*. Grenoble France: Minipad, Apr. 2015. [Online]. Available: http://ieeexplore.ieee.org/ielx7/7395505/7412260/ 07412400.pdf?tp=&arnumber=7412400&isnumber=7412260

- [19] L. Wang, A. Bos, T. van Weelden, and F. Boschman, "The next generation advanced MEMS& sensor packaging," in *Proc. 11th Int. Conf. Electron. Packag. Technol. High Density Packag.*, Aug. 2010, pp. 55–60, doi: 10.1109/ICEPT.2010.5582370. [Online]. Available: https://ieeexplore.ieee.org/ielx5/5570125/5582326/05582370. pdf?tp=&arnumber=5582370&isnumber=5582326&ref= https://ieeexplore.ieee.org/document/5582370/

- [20] J. Hamelink, T. van Weelden, M. Hoedemaker, and E. Boschman, "Selective over-molding of a CMOS TSV wafer with the flexible 3D integration of components and sensors," in *Proc. IEEE 19th Electron. Packag. Technol. Conf. (EPTC)*, Dec. 2017, pp. 1–5, doi: 10.1109/EPTC.2017.8277573. [Online]. Available: https://ieeexplore.ieee.org/ielx7/8267583/8277424/ 08277573.pdf?tp=&arnumber=8277573&isnumber=8277424&ref= and https://ieeexplore.ieee.org/document/8277573/

- [21] J. Hamelink, "Film assisted technology for the advanced encapsulation of MEMS/sensors and LEDs," in *Proc. IEEE* 15th Electron. Packag. Technol. Conf. (EPTC), Dec. 2013, pp. 373–378, doi: 10.1109/EPTC.2013.6745745. [Online]. Available: https://ieeexplore.ieee.org/ielx7/6732180/6745670/06745745.pdf?tp= &arnumber=6745745&isnumber=6745670&ref= https://ieeexplore.ieee.org/document/6745745/

- [22] A. Bos, L. Wang, and T. V. Weelden, "Encapsulation of the next generation advanced MEMS & sensor microsystems," in *Proc. Eur. Microelectron. Packag. Conf.*, Jun. 2009, pp. 1–5.

- [23] M. G. Girma *et al.*, "Miniaturized 122 GHz system-in-package (SiP) short range radar sensor," in *Proc. Eur. Radar Conf.*, Oct. 2013, pp. 49–52.

- [24] S. Scherr *et al.*, "Miniaturized 122 GHz ISM band FMCW radar with micrometer accuracy," in *Proc. Eur. Radar Conf. (EuRAD)*, Sep. 2015, pp. 277–280, doi: 10.1109/EuRAD.2015.7346291. [Online]. Available: https://ieeexplore.ieee.org/ielx7/7331815/7346207/07346291. pdf?tp=&arnumber=7346291&isnumber=7346207

- [25] E. Ozturk et al., "A 120 GHz SiGe BiCMOS monostatic transceiver for radar applications," in Proc. 13th Eur. Microw. Integr. Circuits Conf. (EuMIC), Sep. 2018, pp. 41–44, doi: 10.23919/EuMIC.2018.8539874. [Online]. Available: https://ieeexplore.ieee.org/ielx7/8521654/8539858/08539874. pdf?tp=&arnumber=8539874&isnumber=8539858&ref=

- [26] W. Debski, W. Winkler, Y. Sun, M. Marinkovic, J. Borngräber, and J. C. Scheytt, "120 GHz radar mixed-signal transceiver," in *Proc. 7th Eur. Microw. Integr. Circuit Conf.*, Oct. 2012, pp. 191–194.

- [27] E. Öztürk et al., "A 60-GHz SiGe BiCMOS monostatic transceiver for FMCW radar applications," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 12, pp. 5309–5323, Dec. 2017, doi: 10.1109/TMTT.2017. 2769049.

- [28] A. D. Campo and C. Greiner, "SU-8: A photoresist for high-aspect-ratio and 3D submicron lithography," *J. Micromech. Microeng.*, vol. 17, no. 6, pp. R81–R95, Jun. 2007. [Online]. Available: http://stacks.iop.org/0960-1317/17/i=6/a=R01

- [29] J. D. Williams, "Study on the postbaking process and the effects on UV lithography of high aspect ratio SU-8 microstructures," *J. Micro/Nanolithography, MEMS, MOEMS*, vol. 3, no. 4, p. 563, Oct. 2004.

- [30] R. Natu, M. Islam, J. Gilmore, and R. Martinez-Duarte, "Shrinkage of SU-8 microstructures during carbonization," *J. Anal. Appl. Pyrol.*, vol. 131, pp. 17–27, May 2018, doi: 10.1016/j.jaap. 2018.02.015.

- [31] S. R. GmbH. 120 GHz Radar Transceiver-TRX\_120\_001. Accessed: 2020. [Online]. Available: https://siliconradar.com/products/ single-product/120-ghz-transceiver-trx\_120\_001/

- [32] S. Beer et al., "An integrated 122-GHz antenna array with wire bond compensation for SMT radar sensors," *IEEE Trans. Anten*nas Propag., vol. 61, no. 12, pp. 5976–5983, Dec. 2013, doi: 10.1109/TAP.2013.2282708.

- [33] G. Luinstra and E. Borchardt, "Material properties of poly(propylene carbonates)," Adv. Polym. Sci., vol. 245, pp. 29–48, Jan. 2012, doi: 10.1007/12\_2011\_126.

- [34] O. Phillips, J. M. Schwartz, and P. A. Kohl, "Thermal decomposition of poly(propylene carbonate): End-capping, additives, and solvent effects," *Polym. Degradation Stability*, vol. 125, pp. 129–139, Mar. 2016, doi: 10.1016/j.polymdegradstab.2016.01.004.

- [35] H. Rohling, "Radar CFAR thresholding in clutter and multiple target situations," *IEEE Trans. Aerosp. Electron. Syst.*, vol. AES-19, no. 4, pp. 608–621, Jul. 1983, doi: 10.1109/TAES.1983. 309350.

**Hengqian Yi** received the B.Sc. degree in solidstate electronic engineering from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2013, and the M.Sc. degree in microelectronics from the Delft University of Technology (TUDelft), Delft, The Netherlands, in 2015.

From 2015 to 2019, he worked with the ECTM group, TUDelft, as a Ph.D. Researcher mainly focusing on 3-D advanced packaging. His current research interest includes heterogeneous integration, 5G/6G antenna-in-package, and advanced RF material characterization.

**Efe Öztürk** received the B.Sc. and M.Sc. degrees in electronics engineering from Sabanci University, Istanbul, Turkey, in 2012 and 2014, respectively.

From 2012 to 2014, he was a Research Assistant at Antenna and RF Laboratory, Sabanci University, where he was responsible for the development of RF circuit design for 77-GHz phased-array automotive radars. In 2014, he has joined Silicon Radar GmbH, Frankfurt (Oder), Germany, as an RFIC Designer and currently he is following his Ph.D. in cooperation with IHP, Frankfurt (Oder). His current research

interests include millimeter-wave circuit and antenna design for radar, communication, and imaging applications.

**Marco Koelink** received the Ph.D. and M.Sc. degrees in applied physics from the University of Twente, Enschede, The Netherlands, and the M.B.A. degree from Tilburg University, Tilburg, The Netherlands.

He has a diverse background within, among others, Philips, Eindhoven, The Netherlands, and NXP, Eindhoven, in the semiconductor industry (front end and back end), display technology, solid-state lighting, medical, and industrial equipment. His previous roles include Business

Development Manager for Boschman Advanced Packaging Technology, Duiven, The Netherlands, Development Manager for NXP RF Power, Director Materials Analysis for Philips Research, Eindhoven, and Market Intelligence Manager for Philips Lighting, Eindhoven, and a Business Development Manager with Chip Integration Technology Center (CITC), Nijmegen, The Netherlands, where he is currently responsible for the sales activities.

**Jana Krimmling** received the Dipl.-Ing. degree in microsystems technology from Otto-von-Guericke University, Magdeburg, Germany, in 2008.

From 2009 to 2016, she worked as a Researcher at IHP Microelectronics, Frankfurt (Oder), Germany. In 2016, she joined Silicon Radar GmbH, Frankfurt (Oder), as a System Designer for radar systems and applications. Her field of research covered security algorithms for embedded systems and automation systems.

Andrei A. Damian received the B.Sc. degree in electrical and computer Engineering from Jacobs University Bremen, Bremen, Germany, in 2011, and the M.Sc. degree in electrical engineering (micro-electronics) from the Delft University of Technology, Delft, The Netherlands, in 2013. His M.Sc. research thesis focused on low-temperature wafer bonding using nano-copper particle sintering.

He worked as a Material Development Engineer at NXP, Kaohsiung, Taiwan, from 2014 to 2015. Since 2015, he has been working as a Project Leader

on semiconductor package development and Pb-solder replacement at NXP Nijmegen, Netherlands. He represents NXP at Die Attach five industry consortium for implementing EU RoHS/ELV legislation in the semiconductor industry.

**Wojciech Debski** (Member, IEEE) was born in Krakow, Poland, in 1977. He received the M.S. degree in electronics engineering from the University of Science and Technology, Krakow, Poland, in 2002, and the Ph.D. degree in electrical engineering from the Brandenburg University of Technology, Cottbus, Germany, in 2007.

He joined Silicon Radar GmbH, Frankfurt (Oder), Germany, in 2007, where he is involved in the development of radar components and systems.

**H. W. van Zeijl** (Member, IEEE) was born in Wateringen, the Netherlands, in 1958. He received the Dip.Eng. degree in technical physics from Technical College, Rijswijk, The Netherlands, in 1980, and the Ph.D. degree from Delft University of Technology, Delft, The Netherlands, in 2005.

In 1980, he joined the Interuniversity Reactor Institute, Delft. In 1986, he joined the Delft Institute of Microelectronics and Submicron Technology (DIMES), Delft. He developed several technology courses and a full-week training for engineers from

relevant fields in the industry and academia. These courses are held more than 40 times. Since 2007, he has been a part-time Teacher at Delft University, Delft. He is a (co-) author of more than 80 technical articles and several patents. He currently holds a Staff Position at the Laboratory of Electronic Components Materials and Technology (ECTM), Delft University of Technology. Besides these educational activities, he cooperated in different research projects related to Lithography, MEMs, 3-D integration, packaging, and solid-state lighting integration.

**Guoqi Zhang** (Fellow, IEEE) received the Ph.D. degree from Delft University of Technology, Delft, the Netherlands, in 1993.

He serves as Deputy Director of the European Center for Micro- and Nanoreliability (EUCEMAN) and a Secretary-General of the International Technology Roadmap of Wide bandgap Semiconductors (ITRW). He has worked for NXP Semiconductors, Eindhoven, The Netherlands, as Senior Director of Technology Strategy, until 2009. He authored/coauthored more than 400 scientific

publications. His research interests include multilevel heterogeneous system integration and packaging, wide bandgap semiconductors sensors and components, multiphysics and multiscale modeling of micro/nanoelectronics, and digital twin for mission-critical multifunctional electronics components and systems.

Dr. Zhang was a Philips Research Fellow, until May 2013. He is a Chair Professor for "Micro/Nanoelectronics System Integration and Reliability" of the Delft University of Technology. He is a co-chair of the Advisory Board of the International Solid State Lighting Alliance (ISA).

**René H. Poelma** (Member, IEEE) received the Ph.D. degree (*cum laude*) from the Laboratory of Electronic Components Technology and Materials, Delft University of Technology, Delft, The Netherlands.

He is a Guest Researcher with the Department of Microelectronics, Delft University of Technology. He is currently working as Senior Principal Engineer with the Packaging Research Department, Nexperia B.V., Nijmegen, The Netherlands. His research interests include heterogeneous integration and packag-

ing challenges w.r.t: interfacing functional devices from different physical domains (e.g., photonics, electronics, microfluidics, mechanics, etc.) and making them compatible with new high demanding environments and applications which require increased power-density, device-frequency, manufacturability, and reliability.