## Speed-Power Improvement in High-Voltage Switches Employed in Multi-Electrode Arrays

Safarpour, Amin; Dehnavi, Farzaneh; Saberi, Mehdi; Lotfi, Reza; Serdijn, Wouter A.

DOI 10.1109/TCSII.2022.3161202

Publication date 2022 **Document Version** Final published version

Published in IEEE Transactions on Circuits and Systems II: Express Briefs

**Citation (APA)** Safarpour, A., Dehnavi, F., Saberi, M., Lotfi, R., & Serdijn, W. A. (2022). Speed-Power Improvement in High-Voltage Switches Employed in Multi-Electrode Arrays. *IEEE Transactions on Circuits and Systems II:* Express Briefs, 69(7), 3139 - 3143. Article 9739799. https://doi.org/10.1109/TCSII.2022.3161202

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

# 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# Speed-Power Improvement in High-Voltage Switches Employed in Multielectrode Arrays

Amin Safarpour, Farzaneh Dehnavi, Mehdi Saberi<sup>®</sup>, *Member, IEEE*, Reza Lotfi<sup>®</sup>, *Senior Member, IEEE*, and Wouter A. Serdijn<sup>®</sup>, *Fellow, IEEE*

Abstract-In multi-electrode arrays (MEAs), for electrical recording and electrical stimulation, high voltage (HV) switches are employed to build an analog multiplexer to conduct either a HV stimulation signal from the pulse generator circuit to an electrode or a low-voltage noise-sensitive signal from the electrode to a recording stage. In this brief, a new circuit structure is proposed for HV switches that significantly improves their switching speed, reduces their power dissipation, and also employs a minimum number of bulky HV devices. In order to reduce the transition time of the proposed switch without consuming a large amount of power, during the transition time that the switch is turning on/off, a large current flows through the driver circuit of the switch to turn the switch on/off rapidly; however, after the transition times, this current is significantly reduced to save power. Based on the proposed HV switch, a multiplexer structure has been implemented in 25-V, 0.18- $\mu$ m CMOS IC technology and the measurement results prove its efficacy. Supplied with 25 V and operating with 300 nA current consumption, this switch swings over 20 V with a relatively constant on-resistance of 100  $\Omega$  and features a 80 ns transition time.

*Index Terms*—High-voltage analog multiplexer, high-voltage analog switch, multi-electrode array, low power consumption.

#### I. INTRODUCTION

**H** IGH-VOLTAGE (HV) analog switches are used in a wide variety of applications, such as ultrasound imaging systems [1], battery management systems [2], and MEMS and medical micro-systems [3]. Using multi-electrode arrays (MEAs), it is possible to stimulate or record from multiple sites in a tissue or cell culture for studies on in-vitro or ex-vitro cell cultures or tissue, e.g., for neuroscientific research. In some applications (e.g., in-vitro analysis of excitable cells and closed-loop neurostimulators), it is needed

Manuscript received January 20, 2022; accepted March 12, 2022. Date of publication March 22, 2022; date of current version June 29, 2022. This work was supported by the ECSEL2014-2-662155 Project: Informed (www.informed-project.eu). This brief was recommended by Associate Editor Y. Zhang. (*Corresponding author: Mehdi Saberi.*)

Amin Safarpour, Farzaneh Dehnavi, and Mehdi Saberi are with the Department of Electrical Engineering, Ferdowsi University of Mashhad, Mashhad 9177948944, Iran (e-mail: msaberi@um.ac.ir).

Reza Lotfi is with the Department of Electrical Engineering, Ferdowsi University of Mashhad, Mashhad 9177948944, Iran, and also with the Microelectronics Department, Section Bioelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: rlotfi@ieee.org).

Wouter A. Serdijn is with the Microelectronics Department, Section Bioelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands, and also with the Neuroscience Department, Erasmus Medical Center, 3015 GD Rotterdam, The Netherlands (e-mail: w.a.serdijn@tudelft.nl).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TCSII.2022.3161202.

Digital Object Identifier 10.1109/TCSII.2022.3161202

Fig. 1. The structure of a MEA stimulation and readout system. (a) Stimulation phase. (b) Recording phase.

to apply stimulation signals from a pulse generator circuit to one out of multiple electrodes and then, immediately, record the signal from the tissue after stimulation [4]. For this purpose, an analog multiplexer, made of HV switches, can be used to connect the MEA to one of the stimulators or recording amplifiers, as shown in Fig. 1. In this structure, during the stimulation phase, as is shown in Fig. 1(a), the tissue is stimulated through a HV stimulation switch, i.e.,  $S_{s1}$ , while all the amplifiers of the recording system are disconnected from the tissue to protect them from the high voltage fluctuations. During the recording phase, as is shown in Fig. 1 (b),  $S_{s1}$  is turned off and all the amplifiers are connected to the tissue through HV-protected readout switches, i.e.,  $S_{r1}$ - $S_{rn}$ , to record electrical activity of the tissue immediately after stimulation. In another application [5], instead of injecting the stimulation signal through a single electrode, the user aims to divide it between multiple electrodes, so the switches must turn on and off successively to conduct the signal. For such an application, it is critical to have switches with fast transition times. Moreover, the current trend of increasing the number of electrodes necessitates the required switches to be realized with minimum area occupation (using a minimum number of bulky HV devices) and minimum power consumption. In addition, as the magnitude of the stimulation signal can reach up to several tens of volts, the stimulation switch must be able to swing that much, and have a relatively constant and low onresistance (Ron), when it is on. On the other hand, when it is off, it must provide the electrode with good isolation from the stimulation fluctuations. Moreover, to avoid charge accumulation in the tissue, the leakage current of the switch must

1549-7747 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

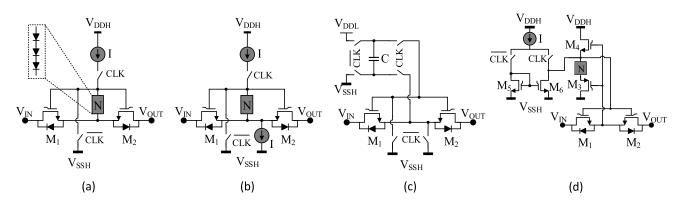

Fig. 2. HV analog switchs presented in (a) [9], [10], (b) [11], (c) [8], and (d) [6]. The switch is on and off during the time that *CLK* is *High* and *Low*, respectively.

be kept as low as possible. As for the recording switch, it is worth noting that a recording switch requires a low  $R_{on}$  to contribute little noise, a moderate off-isolation to protect the readout circuit, and good power and speed performances.

In order to improve the performance of the HV switches, several attempts have been reported in the literature, to be dis-cussed in Section II. However, none of them presents a structure fulfilling all the requirements of high speed, low power, low area, high swing, and zero leakage current. Hence, in this brief, a new structure for low-leakage HV switches is pro-posed that not only significantly improves the switching speed and power consumption of the circuit, but also employs a minimum number of bulky HV devices.

The rest of this brief is organized as follows. A review of reported structures for HV switches is presented in Section II, followed by the proposed circuit in Section III and measurement results in Section IV. Finally, Section V concludes this brief.

#### **II. LITERATURE SURVEY**

In order to implement HV switches, several types of HV devices such as thick-oxide MOSFETs and laterallydiffused MOSFETs (LDMOS) can be employed. Thick-oxide MOSFETs are usually symmetric, but they are able to operate with absolute gate-source/drain voltages up to 18V in conventional technologies. On the other side, LDMOSs are asymmetric with absolute gate-source voltages up to 5V and gate-drain voltages from 10V to more than 100V. Most designers prefer to use LDMOS devices to be able to work with voltages higher than 18V [1], [6]-[8]. However, as the body connection of LDMOSs must be always shorted to the source, the drain-body parasitic diode creates a path from source to drain terminals for NMOS with a negative drain-source voltage  $V_{DS}$  and for PMOS with a positive  $V_{DS}$ . Accordingly, it is impossible to employ a single LDMOS to build a bi-directional HV switch. Therefore, bi-directional HV switches are made up of two LDMOSs in series, with source-to-source connection. in a way that the body diodes are connected back-to-back so no current can flow through them when the MOSFETs are off, as shown in Fig. 2.

In the bi-directional switch structures shown in Fig. 2(a)-(d),  $M_1$  and  $M_2$  form the core of the HV

switch through which the switch current passes. Their source terminals and gate terminals are tied together, and their drains form the input and output (I/O) terminals of the switch. In order to turn on the switch, the gate-source voltages of M<sub>1</sub> and M<sub>2</sub> must be in the range of  $V_{TH} < V_{GS} < 5V$ , where  $V_{TH}$  represents the threshold voltage of the transistors. On the other hand, the gate-source voltages  $V_{GS}$  must be in the range  $-5V < V_{GS} < 0$  to turn the switch off. To drive M<sub>1</sub> and M<sub>2</sub> and provide the required  $V_{GS}$ , several techniques have been reported [6]-[11]. Fig. 2(a) illustrates the basic structure of the required driver circuit consisting of a current source, I, connected to the gate terminals of M1 and M2 and a one-port network N that converts the current to the required  $V_{GS}$ . It is clear that, by using the current source, it is possible to have a floating switch-driving circuit. Network N can be implemented by either a resistor [1], a Zener diode [10], several diodes placed in series, or diode-connected MOSFETs [9]. A significant drawback of this structure is the flow of the drivercurrent I through the terminal ports of the switch, leading to a non-zero leakage current which is not acceptable for applications working with current signals such as neural stimulation systems. To tackle this issue, the structure presented in [11] employs an additional current source to sink the driver current and null the leakage current, as shown in Fig. 2(b); however, due to the existing mismatch between the current sources, the leakage current cannot be fully nullified. In order to overcome this problem, a bootstrapped structure, symbolically shown in Fig. 2(c), is suggested in [8], which can connect a pre-charged flying capacitor to the gate and the source, even when the input signal is non-zero. The biggest advantage of using a flying capacitor is that there is no need for a HV power supply, so the power consumption decreases; however, these structures suffer from leakage current of the flying capacitor that, as a consequence, cannot maintain the gate-source voltage for a long time. Thus, the flying-capacitor technique is not appropriate for low-frequency applications and those in which the employed switch is on for a long time such as neural stimulation. Alternatively, the structures presented in [6] and [13] utilize a bootstrapped technique in which the driver current path is separated from the switch current path. The schematic of the circuit presented in [6] is shown in Fig. 2(d). In this structure, when the switch is on, the source terminals of M1 and M2 are connected to the gate

terminal of a PMOS (i.e., M<sub>3</sub>) operating as a source-follower circuit driven by a current source, I. In addition, the gate terminals of M<sub>1</sub> and M<sub>2</sub> can be connected to the source of M<sub>3</sub> so that  $V_{GS1-2}$  equals  $|V_{GS3}|$ , but it is better to put a Zener diode (i.e., network N) in series with  $M_3$  to generate the required gate-source voltage at a lower current. As the source terminals of  $M_1$  and  $M_2$  are connected to the gate terminal of M<sub>3</sub>, the driver current is completely isolated from the switch current so that no extra current flows through the I/O terminals of the switch. Similarly, when the switch is off, another source-follower structure (i.e., M<sub>4</sub>) is employed to create a negative  $V_{GS}$  for M<sub>1</sub> and M<sub>2</sub>. It is clear that this structure benefits from almost zero leakage current. However, in order to increase the transition speed of this switch, current I must be increased, leading to a significant increase in the power consumption, to be explained in Section III.

#### **III. THE PROPOSED HV SWITCHES**

As discussed above, the structure reported in [6], shown in Fig. 2(d), presents almost zero leakage current. However, it suffers from the existing trade-off between speed and power consumption. More specifically, to turn the switch on, the gate-source capacitance of  $M_1$  and  $M_2$ ,  $C_{gs1-2}$ , must be charged with the required charge  $Q_{req}$  provided by current source *I*. Assuming *I* is constant, the on-transition time,  $t_{on}$ , is obtained from

$$t_{on} = \frac{Q_{req}}{I}.$$

(1)

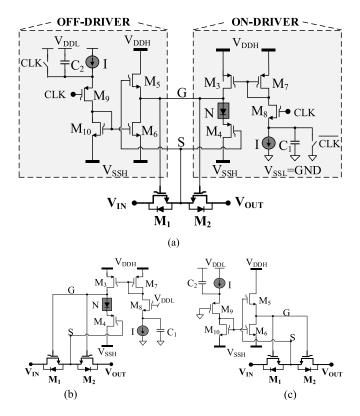

According to (1), for higher switching speed, I must be increased, leading to more power consumption. To overcome this problem, a new HV switch is proposed, as shown in Fig. 3(a). The proposed circuit employs two source-follower structures, i.e., M<sub>4</sub> and M<sub>5</sub>, as on- and off-driver circuits to provide the required gate-source voltage for M<sub>1</sub> and M<sub>2</sub>, when the switch is on and off, respectively. In order to reduce the transition time of the switch without consuming a large amount of power, during the transition times that the switch is turning on (off), a large current flows through the on- (off-) driver circuit to charge (discharge) C<sub>gs1-2</sub>, and turns M<sub>1</sub> and M<sub>2</sub> on (off); however, after the transition times, this current is significantly reduced to save power.

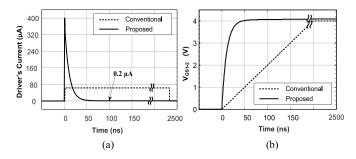

The operation of the proposed circuit is as follows. For the on-state behavior (i.e., Fig. 3(b)), when the controlling signal CLK changes from  $V_{SSL} = GND = 0$  V to  $V_{DDL}$ , M<sub>8</sub> turns on. Therefore, a current flows through M<sub>8</sub> and M<sub>7</sub>. This current is mirrored into M<sub>3</sub> and the source-follower structure (i.e., transistor  $M_4$  and network N) to create a constant  $V_{GS}$  for  $M_1$  and  $M_2$ . However, during the transition time, this current is consumed to charge  $C_{gs1-2}$  and to turn  $M_1$  and  $M_2$  on. In order to increase the speed of the switch, during the transition time, a large current is needed to charge C<sub>gs1-2</sub> and to turn the switch on; however, when the switch is turned on completely, this current can be reduced to save power, as shown in Fig. 4. For this purpose, a capacitor (i.e.,  $C_1$ ) is used in parallel with the current source. The effect of adding C<sub>1</sub> is that when M<sub>8</sub> is turned on, since capacitor C<sub>1</sub> is discharged, the gate-source voltage of M<sub>8</sub> is large, meaning that a large current flows

Fig. 3. (a) The schematic of the proposed HV switch, and its (b) on-state and (c) off-state equivalent circuits.

through this transistor. This current is mirrored into M<sub>3</sub> and charges C<sub>gs1-2</sub> rapidly, leading to a small transition time. At the same time, capacitor  $C_1$  is also being charged, decreasing the gate-source voltage and consequently the current of M<sub>8</sub>. When  $C_1$  is completely charged, the current of  $M_8$  will equal current I, as shown in Fig. 4. Since the transition time and consequently the speed of the proposed switch are independent of the static current, the static current can be decrease considerably. To minimize the static power, network N is employed to obtain a higher  $V_{GS1-2}$  with less current. As discussed in Section II, network N can be implemented by either a resistor, a Zener diode, several diodes placed in series, or diode-connected MOSFETs. In our design, it is implemented by three diode-connected transistors placed in series.  $V_{GS1-2}$  is equal to  $V_N + |V_{GS4}|$ , where  $V_N$  represents the voltage across network N, and can be controlled by the amount of current I, the number and sizes of the diode-connected transistors, and the size of transistor M<sub>4</sub>.

Similarly, when the control signal *CLK* becomes 0 V, the switch is forced to its off-state using M<sub>5</sub>, M<sub>6</sub>, M<sub>9</sub>, M<sub>10</sub>, and C<sub>2</sub>, as shown in Fig. 3(c). In more detail, as *CLK* changes to  $V_{SSL} = 0$  V, M<sub>9</sub> turns on, and a current flows through the off-driver circuit consisting of M<sub>9</sub>, M<sub>10</sub>, M<sub>6</sub>, and M<sub>5</sub>. As a consequence, the source-follower circuit (i.e., M<sub>5</sub>) generates a negative gate-source voltage for M<sub>1</sub> and M<sub>2</sub> to turn the switch off. Similar to the previous state, using a pre-discharged capacitor (i.e., C<sub>2</sub>) leads to the situation that, during the transition time, a large current flows through the off-driver circuit to discharge C<sub>gs1-2</sub>, and turns M<sub>1</sub> and M<sub>2</sub> off rapidly; however,

Fig. 4. The on-driver's current and the gate-source voltage of  $M_1$  and  $M_2$  (i.e.,  $V_{GS1-2}$ ) in the conventional (i.e., Fig. 2(d)) and the proposed HV switch.

Fig. 5. The schematic of the proposed HV readout switch.

after the transition time, the current of  $M_9$  will be reduced to current *I*, leading to power saving.

In the design of the proposed HV switch, three main design objectives (i.e.,  $R_{on}$ , transition time, and power consumption) affect each other. In order to reduce the on-resistance, i.e.,  $R_{on}$ , the values of not only  $V_{GS1-2}$  during the on-state, but also the width of the main transistors  $M_1$  and  $M_2$  have to be increased. In order to increase the value of  $V_{GS1-2}$ , several diodes in series are employed to reduce the value of current *I* and consequently the static power consumption of the circuit. As for the switching speed, the value of the current is increased only during the transition time (using  $C_1$  and  $C_2$ ) to charge  $C_{gs1-2}$  in a shorter time. It should be noted that an important design consideration here is to monitor  $V_{GS1-2}$  not to violate the safe operating area (SOA). For this purpose, the sizes of  $C_1$  and  $C_2$  have to be chosen such as not to overcharge  $C_{gs1-2}$ .

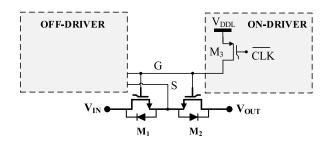

It is worth mentioning that the proposed HV switch shown in Fig. 3 is suitable for the stimulation switch employed in the MEA stimulation and readout system shown in Fig. 1. However, it is basically overdesigned to be used as a recording switch in the readout system, because, for a recording switch, the amplitude of its input signal is very small. In order to modify the proposed switch for a readout switch, the core devices (i.e., M<sub>1</sub> and M<sub>2</sub>) and the off-driver (i.e., M<sub>5</sub>, M<sub>6</sub>, M<sub>9</sub>, M<sub>10</sub>, R<sub>2</sub>, and C<sub>2</sub>) are kept without any modification but the on-driver is simplified and can be replaced with a single HV PMOS transistor connected to the low-voltage supply ( $V_{DDL}$ ), as shown in Fig. 5. When *CLK* is  $V_{DDL}$ , M<sub>3</sub> pulls node *G* up and as the input signal has a small amplitude with a DC level around GND (i.e.,  $V_{SSL}$ ), M<sub>1</sub> and M<sub>2</sub> can easily conduct the signal with small enough R<sub>on</sub>.

#### **IV. MEASUREMENT RESULTS**

The proposed HV switch shown in Fig. 3 has been designed and fabricated in  $0.18\mu$ m HV CMOS IC technology. In our

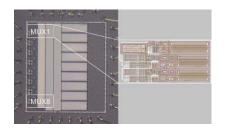

Fig. 6. Die micrograph and layout of the MEA stimulation and readout system using the proposed HV switches.

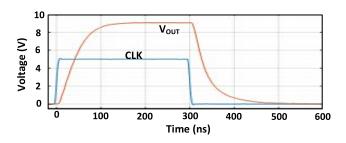

Fig. 7. On- and off-transition behaviors of the proposed HV switch, when a 10 V DC signal is applied to the input of the switch.

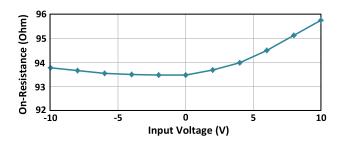

Fig. 8. On-resistance (i.e.,  $R_{on}$ ) of the proposed switch as a function of the input voltage.

design, in order to have an I/O swing of 20 V, the highvoltage power supplies are selected to be  $V_{DDH} = +15$  V and  $V_{SSH} = -10$  V and the low-voltage power supplies  $V_{DDL}$ and  $V_{SSL}$  are selected to be +2.5 V and 0 V, respectively. The die micrograph and the layout of the MEA stimulation and readout system using the proposed HV switches are shown in Fig. 6. The following measurement results were obtained when the proposed switch is loaded by a 1-k $\Omega$  resistor in parallel with a 20-pF capacitor.

Fig. 7 shows the measurement results related to the transition behavior of the proposed switch when a 10 V DC signal is applied to the input of the switch. The transition time of the proposed switch is less than 80 ns. It is worth mentioning that without employing capacitors  $C_1$  and  $C_2$  of the on- and offdriver circuits shown in Fig. 3, the transition time of the switch would be in the range of 1 ms which means that the proposed technique reduces the transition time of the HV switch by more than 4 orders of magnitude. Moreover, Fig. 8 depicts the onresistance ( $R_{on}$ ) of the proposed switch as a function of the input voltage. It can be observed that for different values of the input voltage from -10 V to +10 V, the on-resistance of the proposed switch varies only between 93.4  $\Omega$  and 95.7  $\Omega$ . In addition, the measurement results show that the leakage current of the proposed switch is lower than 3 nA which is low

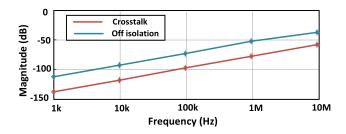

Fig. 9. Off-isolation and crosstalk of the proposed switch.

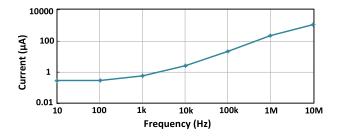

Fig. 10. Total current consumption of the proposed circuit as a function of switching frequency.

enough to avoid charge accumulation at the electrode-tissue interface [12].

The off-isolation and crosstalk of the proposed switch are depicted as functions of the input frequency in Fig. 9. To measure the off-isolation, the switch is turned off and a sinusoidal signal with the maximum amplitude, i.e., 10 V, is applied to its input terminal, and its output signal is measured. Then, the off-isolation obtained from

$$Off - isolation_{(dB)} = 20 \log \frac{V_{out,i}}{V_{in,i}}.$$

(2)

As for the crosstalk, a sinusoidal signal with maximum amplitude is applied to the input of an on-switch, and the output of an adjacent off-switch is measured. The crosstalk is calculated from

$$Crosstalk_{(dB)} = 20\log\frac{V_{out,i+1}}{V_{in,i}}.$$

(3)

From Fig. 9, it can be observed that the off-isolation and the crosstalk of the switch follow an almost -20-dB/decade slope.

Fig. 10 shows the current consumption of the proposed HV switch as a function of switching frequency. As expected, for low frequencies, the static current is dominant. As the switching frequency increases, the dynamic current grows.

Finally, in Table I, the performance of the proposed HV switch is compared with the other works, confirming the effectiveness of the proposed circuit technique.

It is worth mentioning that the measurement results show that the proposed readout switch shown in Fig. 5 presents the same performance as the proposed stimulation apart from that its static current consumption is zero when it is on, and its off-to-on transition time is smaller than 20 ns.

### V. CONCLUSION

In this brief, a new low-leakage high-voltage switch is proposed for multi-electrode array stimulation and recording

TABLE I

Comparison of the Proposed HV Switch With Other Works

|                                                 | [1]                                           | [13]                  | This work                     |

|-------------------------------------------------|-----------------------------------------------|-----------------------|-------------------------------|

| Process (µm)                                    | 0.35                                          | 0.35                  | 0.18                          |

| Application                                     | Ultrasound                                    | Neural<br>Stimulation | Neural<br>Stimulation         |

| Structure                                       | Resistor-based<br>driver                      | Bootstrapped          | Bootstrapped                  |

| I/O Swing (V)                                   | 50                                            | 120                   | 20<br>@Vddh=15V,<br>Vssh=-10V |

| Transition<br>Time (ns)                         | NA                                            | 4000                  | 80                            |

| Istatic (µA)                                    | 20                                            | 90                    | 0.3                           |

| $R_{on}\left(\Omega ight)$                      | 26                                            | 700                   | 100                           |

| Area (mm <sup>2</sup> )                         | 0.17                                          | 0.26                  | 0.018                         |

| Area× $R_{on}$<br>(mm <sup>2</sup> . $\Omega$ ) | 4.42                                          | 182                   | 1.8                           |

| Off-Isolation<br>(dB)                           | -90 @10MHz                                    | -34                   | -92 @ 10kHz                   |

| Constraints                                     | Speed-power trade-off,<br>unequal I/O current |                       |                               |

systems. The proposed structure significantly enhances the switching speed of the switch without any increase in the static power consumption. Moreover it employs a minimum number of bulky high-voltage devices. Measurement results of the proposed switch in an HV  $0.18\mu$ m technology confirm the efficacy of the proposed circuit techniques.

#### REFERENCES

- J. Borg and J. Johansson, "An ultrasonic transducer interface IC with integrated push-pull 40 Vpp, 400 mA current output, 8-bit DAC and integrated HV multiplexer," *IEEE J. Solid-State Circuits*, vol. 46, no. 2, pp. 475–484, Feb. 2011.

- [2] Q. Zhang, Y. Yang, and C. Chai, "60 V tolerance full symmetrical switch for battery monitor IC," J. Semicond., vol. 38, no. 6, p. 6500, Jun. 2017.

- [3] S. Dai, R. W. Knepper, and M. N. Horenstein, "A 300-V LDMOS analog-multiplexed driver for MEMS devices," *IEEE Trans. Circuits Syst. I, Reg. Paper*, vol. 62, no. 12, pp. 2806–2816, Dec. 2015.

- [4] "CMOS-MEA5000-System." MultiChannelSystems. [Online]. Available: https://www.multichannelsystems.com/products/cmosmea5000-system#description

- [5] M. Vöröslakos *et al.*, "Direct effects of transcranial electric stimulation on brain circuits in rats and humans," *Nat. Commun.*, vol. 9, no. 1, pp. 1–17. Feb. 2018.

- [6] C. S. Birk and G. M. Puchalt, "Four-quadrant bootstrapped switch circuit," U.S. Patent 0 009 623 A1, Jan. 10, 2013.

- [7] J. S. K. Hara, "A new 80V 32x32ch low loss multiplexer LSI for a 3D ultrasound imaging system," in *Proc. Int. Symp. Power Semicond. Devices ICs (ISPSD)*, 2005, pp. 359–362.

- [8] D. Y. Aksin and I. Ozkaya, "25V sampling switch for power management data converters in 0.35µm CMOS with DNMOS," in *Proc. Eur. Solid-State Circuits Conf. (ESSCIRC)*, 2009, pp. 136–139.

- [9] H. Shafir, C. M. Daft, and P. M. Wagner, "Switch for aperture control in medical diagnostic ultrasound imaging," U.S. Patent 0 021 920 A1, Jan. 27, 2011.

- [10] B. Dufort, T. Letavic, and S. Mukherjee, "Digitally controlled highvoltage analog switch array for medical ultrasound applications in thinlayer silicon-on-insulator process," in *Proc. IEEE Int. SOI Conf.*, 2002, pp. 78–79.

- [11] G. Diaz, "Wide common mode range transmission gate," U.S. Patent 0132331 A1, 2014.

- [12] H. Chun, T. Lehmann, and Y. Yang, "Implantable stimulator for bipolar stimulation without charge balancing circuits," in *Proc. Biomed. Circuits Syst. Conf. (BioCAS)*, 2010, pp. 202–205.

- [13] D. Osipov *et al.*, "Current driver with read-out HV protection for neural stimulation," in *Proc. IEEE Nordic Circuits Syst. Conf. (NORCAS)*, 2016, pp. 1–4.