### A 4-µW Bandwidth/Power Scalable Delta-Sigma Modulator Based on Swing-Enhanced Floating Inverter Amplifiers

Zhao, Menglian; Zhao, Yibo; Zhang, Huajun; Hu, Yaopeng; Bao, Yuanxin; Ye, Le; Qu, Wanyuan; Tan, Zhichao

DOI

10.1109/JSSC.2021.3123261

Publication date 2022

**Document Version**Final published version

Final published version Published in

IEEE Journal of Solid-State Circuits

Citation (APA)

Zhao, M., Zhao, Y., Zhang, H., Hu, Y., Bao, Y., Ye, L., Qu, W., & Tan, Z. (2022). A 4-µW Bandwidth/Power Scalable Delta-Sigma Modulator Based on Swing-Enhanced Floating Inverter Amplifiers. *IEEE Journal of Solid-State Circuits*, *57*(3), 709-718. Article 9607020. https://doi.org/10.1109/JSSC.2021.3123261

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

## Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A 4-μW Bandwidth/Power Scalable Delta–Sigma Modulator Based on Swing-Enhanced Floating Inverter Amplifiers

Menglian Zhao, *Member, IEEE*, Yibo Zhao, *Student Member, IEEE*,

Huajun Zhang<sup>®</sup>, *Graduate Student Member, IEEE*, Yaopeng Hu, *Student Member, IEEE*,

Yuanxin Bao, Le Ye<sup>®</sup>, *Member, IEEE*, Wanyuan Qu<sup>®</sup>, *Member, IEEE*,

and Zhichao Tan<sup>®</sup>, *Senior Member, IEEE*

Abstract—This article presents a fully dynamic scalable switched-capacitor delta–sigma modulator that achieves a 94.1-dB dynamic range (DR). Power-and- bandwidth scalability by only changing the clock frequency is achieved using a capacitively biased and swing-enhanced floating inverter operational transconductance amplifier (OTA). Fabricated in a 180-nm CMOS process, the prototype achieves an signal-to-noise-and-distortion ratio (SNDR) of >87 dB across 4× scaling from 100 to 400 kHz of the sampling frequency  $f_{\rm S}$ . At 200-kHz  $f_{\rm S}$ , it achieves an SNDR/DR of 89.3/94.1 dB while consuming 4  $\mu$ W, leading to a DR-based Schreier figure of merit (FoM) of 177.1 dB.

$\label{eq:lower_lower} \emph{Index Terms} \textbf{—} \textbf{B} \textbf{a} \textbf{n} \textbf{d} \textbf{w} \textbf{i} \textbf{d} \textbf{t} \textbf{h} \textbf{ (BW)} \quad \textbf{scalable, high resolution, ultra-low power.}$

#### I. Introduction

THE evolution of the Internet of Things (IoT) has fueled the demand for analog-to-digital converters (ADCs) with lower power dissipation and higher resolution in the past decade. Most of these converters for the IoT applications are powered by batteries or energy harvesters, so an ultra-low-power (ULP) design is essential to allow for a longer lifespan of up to 10–15 years. This type of converters also needs to measure small signals with different bandwidth (BW) requirements in the sub-kilohertz range for different applications. Moreover, IoT systems are often heavily duty-cycled to reduce power consumption, where on-demand conversions are executed when events of interest are detected. To allow for more flexible system-level partitioning and to cover a broader application space, higher resolution with low power consumption is desired while supporting scalable BW and power.

Manuscript received July 3, 2021; revised September 24, 2021; accepted October 15, 2021. Date of publication November 9, 2021; date of current version February 24, 2022. This article was approved by Associate Editor Mark Oude Alink. (Corresponding author: Zhichao Tan.)

Menglian Zhao, Yibo Zhao, Yaopeng Hu, and Zhichao Tan are with the College of Information and Electronics Engineering, Zhejiang University, Hangzhou 310063, China (e-mail: zhichaotan@zju.edu.cn).

Huajun Zhang is with the Department of Microelectronics, Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS), Delft University of Technology, 2628 CD Delft, The Netherlands.

Yuanxin Bao and Le Ye are with the Advanced Institute of Information Technology, Peking University, Beijing 100871, China.

Wanyuan Qu is with the School of Micro-Nano Electronics, Zhejiang University, Hangzhou 310063, China.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2021.3123261.

Digital Object Identifier 10.1109/JSSC.2021.3123261

However, it is challenging to achieve fully dynamic operation and high resolution simultaneously. Successive approximation register (SAR) ADCs feature fully dynamic operation and hence are BW and power scalable, and ULP designs have been reported [1]–[4]. They do not require operational transconductance amplifiers (OTAs), making them more power-efficient and suitable for conversion on-demand. However, to achieve high resolution, they need to implement complex calibration schemes to tackle mismatches in their capacitive DACs [5]–[7], which increases power and area. A low noise comparator is also required, which is often power-hungry.

A widely used architecture for high-resolution applications is the discrete-time delta–sigma modulator (DTDSM), which can achieve high power efficiency by oversampling and noise shaping [8]–[12]. However, their loop filters do not readily scale with the sampling frequency  $f_{\rm S}$  on the fly because they are based on OTAs that draw static bias currents. Especially in ULP applications, the SNR of previous designs using active [13] or passive [14] loop filters was limited to about 50 dB. In these designs, the loop filter has been the bottleneck to achieve low power and high resolution simultaneously.

To improve the power efficiency of DTDSM, inverter-based integrators are a popular choice [8]. However, the CMOS inverter's quiescent current is strongly dependent on its input voltage and is prone to process, supply voltage, and temperature (PVT) variations. They usually require special biasing circuits addressing PVT sensitivity [9], [15], [16] and common-mode feedback (CMFB) circuitry [8], [9], [15], [16] that consumes extra power and takes a certain amount of time to settle after waking up in a ULP design before the output becomes valid.

The floating inverter amplifier (FIA) [17] presents an option for a fully dynamic OTA implementation. However, it suffers from a limited output swing and an ill-defined operating point, both of which are functions of the supply and threshold voltages. In [18], multiple supplies are required to ensure sufficient speed and output swing to address this issue, which increases system complexity.

In this article, a capacitive biasing technique is introduced to improve the FIA's performance over PVT and increase its

0018-9200 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

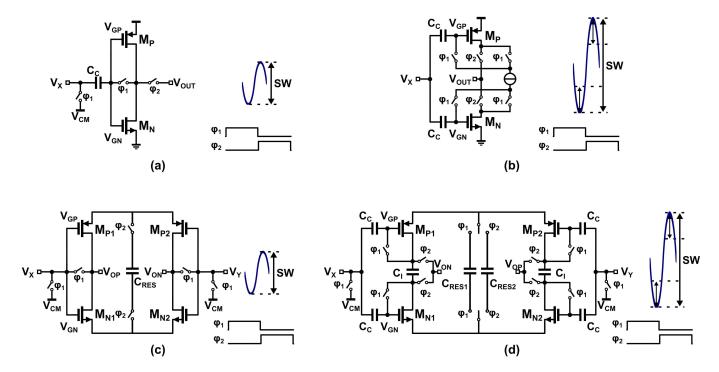

Fig. 1. (a) Conventional inverted-based OTA [8]. (b) Dynamic biasing scheme [9]. (c) Conventional floating inverted-based OTA [17], [18]. (d) Proposed capacitive biasing scheme.

output swing [19]. It also enables the proposed amplifier to adaptively change its BW when  $f_{\rm S}$  is varied, enabling BW and power scaling of the DTDSM by simply varying the clock frequency. Measurement results of the prototype implemented in a 180-nm CMOS process indicate a consistent performance of >87-dB signal-to-noise-and-distortion ratio (SNDR) over 4× clock frequency scaling. The prototype only consumes 4  $\mu$ W when operating with an oversampling ratio of 125- and 800-Hz signal BW.

This article is organized as follows. Section II reviews several existing inverter-based OTA designs. Section III presents the proposed capacitively biased swing-enhanced FIA (SEFIA) and analyzes the operation of the SEFIA in detail. The prototype SEFIA-based DTDSM implementation is detailed in Section IV, followed by measurement results in Section V. Section VI concludes this article.

#### II. REVIEW OF EXISTING INVERTER-BASED OTAS

Implementing OTAs has become increasingly challenging due to process scaling and the continuous quest to low power consumption. In [8], the use of logic inverters as OTAs is proposed, which achieves high power efficiency under low supply voltages because both NMOS and PMOS devices contribute transconductance  $(g_{\rm M})$ . However, its bias current is sensitive to PVT variations. For example, across process variations from SS corner to FF corner, the supply current and  $g_{\rm M}$  can vary by several orders of magnitude. To address this issue, a dedicated voltage regulator [20] or body biasing [21] can be applied at the cost of increased complexity and power. Furthermore, unlike conventional OTAs with differential input, the inverter does not offer a well-defined virtual ground. Therefore, they typically employ auto-zeroing (AZ) to store

the tripping voltage (including offset and 1/f noise) onto a coupling capacitor  $C_{\rm C}$  between the inverter's input and the actual input signal  $V_{\rm X}$ , as shown in Fig. 1(a).

The inverter-based amplifier is also sensitive to input common-mode (CM) variations. To process a fully differential input robustly, extra CMFB circuitry is also required, which increases the loading and noise [8] and, thus, the amplifier's power consumption. Also, the amplifier's output swing is limited to  $(V_{\rm THN} + |V_{\rm THP}| - 2V_{\rm DSAT})$ .

To achieve robust operation across PVT variations, a dynamic biasing scheme [9] can be applied, as shown in Fig. 1(b). During the AZ phase, a floating current source is employed to enforce a well-defined bias current by storing the bias voltages for the NMOS and PMOS devices separately on the 2  $C_{\rm C}$  values. This also improves the output swing to  $(V_{\rm DD}-2V_{\rm DSAT})$ . However, like the inverter-based OTA in Fig. 1(a), the AZ procedure consumes as much additional power as the actual signal amplification.

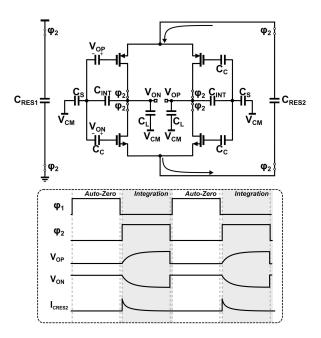

Recently, the FIA is proposed [17], [18], shown in Fig. 1(c), which is insensitive to input CM variations and operates without CMFB. This is because the FIA is supplied by a reservoir capacitor  $C_{\rm RES}$ , which forces the CM output current to zero [22]. However, similar to the conventional inverter-based amplifier, the FIA suffers from swing limitations, and its  $g_{\rm M}$  varies considerably across PVT variations.

#### III. ANALYSIS OF THE PROPOSED SEFIA

This section first presents the proposed capacitively biased swing enhancement technique. Afterward, the swing enhancement, BW scalability, and power efficiency of the proposed SEFIA are discussed.

#### A. Proposed SEFIA Using Capacitive Biasing

The proposed SEFIA using capacitive biasing is shown in Fig. 1(d). It is supplied by reservoir capacitors similar to the FIA in Fig. 1(c) and employs separate input coupling capacitors ( $C_{\rm C}$ 's) as the dynamically biased inverter in Fig. 1(b). The capacitor  $C_{\rm I}$  functions as a dynamic floating current source. During the AZ operation,  $M_{\rm NI,2}$  and  $M_{\rm Pl,2}$  are diode-connected, charge redistribution occurs between  $C_{\rm RESI}$ ,  $C_{\rm I}$ , and the  $C_{\rm C}$  values, and the bias voltages for  $M_{\rm NI,2}$  and  $M_{\rm Pl,2}$  are stored on the  $C_{\rm C}$ 's. During the amplification phase,  $C_{\rm I}$  is discharged, and the  $C_{\rm C}$  values couple the input to  $M_{\rm NI,2}$  and  $M_{\rm Pl,2}$ . Two reservoir capacitors,  $C_{\rm RESI}$  and  $C_{\rm RES2}$ , supply the amplifier in a ping-pong manner during the two phases.

Compared to the conventional FIA, the SEFIA achieves a wider output swing by the voltage across  $C_{\rm I}$  at the end of AZ. Meanwhile, the fully dynamic and CMFB-free operation of the FIA is also preserved.

Compared to the dynamically biased inverter-based OTA in Fig. 1(b), which consumes as much power in AZ as in the amplification phase,  $C_{\rm RES1}$  can be set smaller than  $C_{\rm RES2}$  in the SEFIA to save power, while the extra degree of freedom offered by  $C_{\rm C}$  can be used to ensure sufficient driving capability for amplification.

#### B. Swing Enhancement

Since the SEFIA is supplied dynamically by reservoir capacitors, its bias current changes with time. This section discusses its operation in detail and analyzes the output swing and BW characteristics of the SEFIA, which are essential parameters for switched-capacitor (SC) circuits.

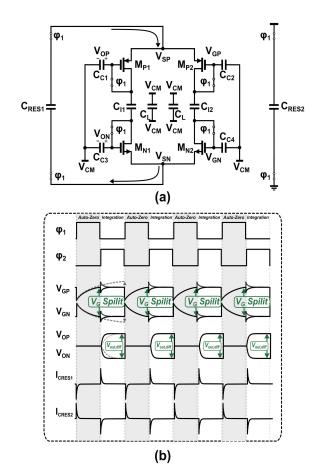

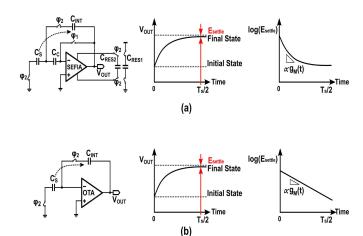

Fig. 2(a) shows the operation of SEFIA during  $\Phi 1$ . At the beginning of AZ, charge redistribution between  $C_{\text{C1-4}}$  and the  $C_{\text{I1,2}}$  occurs. This takes little time, assuming the switches'  $R_{\text{on}} \ll 1/g_{\text{M}}$ . Then, the reservoir capacitor  $C_{\text{RES1}}$  discharges into the  $C_{\text{I1,2}}$  through  $M_{\text{N1,2}}$  and  $M_{\text{P1,2}}$ . During this stage, the instantaneous current is a function of the voltages on  $C_{\text{RES1}}$  and  $C_{\text{I1,2}}$  and changes with time. As shown in Fig. 2(b), the current flowing into  $C_{\text{I1,2}}$  reduces over time, as the overdrive of  $M_{\text{N1,2}}$  and  $M_{\text{P1,2}}$  reduces. At the end of  $\Phi 1$ , the gate voltages of  $M_{\text{N1,2}}$  and  $M_{\text{P1,2}}$  are sampled onto  $C_{\text{C1-4}}$ .

Compared to the conventional FIA, the output swing of the SEFIA is increased by the voltage across  $C_{\rm II,2}$  at the end of AZ, which changes as the clock frequency, and thus, the duration of AZ is varied, as shown in Fig. 2(b). Assuming that  $M_{\rm NI,2}$  and  $M_{\rm PI,2}$  operate in weak inversion, it can be shown that the voltage across  $C_{\rm II,2}$  increases logarithmically with time<sup>1</sup>

$$V_{\rm CI}(t) = V_{\rm GP}(t) - V_{\rm GN}(t) = \frac{2C_{\rm RES1}}{2C_I + C_{\rm RES1}} nU_T \ln(\zeta t) + c$$

(1)

$^{1}$ To simply the derivation, we assume that the NMOS and PMOS have the same  $I_{\rm D0}W/L$ , implying the same  $g_{\rm M}$ . In reality, the PMOS and NMOS devices have different mobility and threshold voltages, and in the implementation, the W/L of the PMOS is two times that of the NMOS, which gives acceptable, but not exact matching of  $g_{\rm M}$ 's, so the waveform for  $V_{\rm GP}$  and  $V_{\rm GN}$  has different shapes.

Fig. 2. (a) Operation and (b) time-domain behavior of the SEFIA during AZ.

where

$$c = \frac{C_{\text{RES1}}}{2C_I + C_{\text{RES1}}} V_{\text{DD}} \tag{2}$$

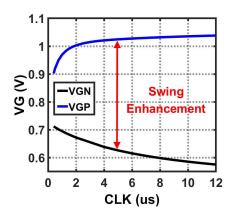

where n is the slope factor in weak inversion and  $U_T$  is the thermal voltage kT/q.  $\zeta$  is also a constant (see the Appendix), and  $V_{\rm GP}$  and  $V_{\rm GN}$  are the gate voltages for the PMOS and NMOS devices, respectively. Fig. 3 shows that the amount of swing enhancement is a function of the clock period, in which AZ takes half of the time. As shown, the swing increases less when the clock period is reduced. However, due to the logarithmic relation in (1), the variation across the clock period is relatively small.

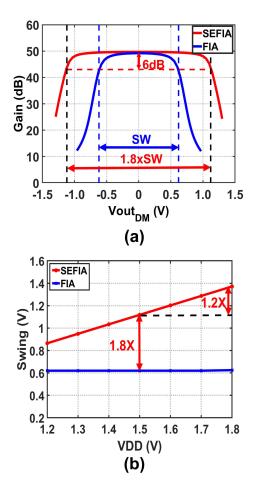

Fig. 4(a) shows the simulated dc gain of an example of the proposed SEFIA and the conventional FIA, sized for the same dc gain and settling speed, versus output swing when operating with a 200-kHz clock. Compared to the conventional FIA, the swing is expanded by 1.8 times, from 0.62 to 1.12 V at 6-dB gain compression. According to (1), the swing also widens with a higher supply voltage. As shown in Fig. 4(b), when  $V_{\rm DD}$  increases from 1.2 to 1.8 V, the output swing expands accordingly from 0.82 to 1.37 V.

#### C. Scalable BW

The conventional FIA is turned off automatically after the reservoir capacitor is discharged, and the output voltage

Fig. 3.  $V_{\rm GN}$  and  $V_{\rm GP}$  versus CLK period at the end of AZ.

Fig. 4. (a) Output swing comparison of the proposed SEFIA and conventional FIA. (b) Output swing as a function of the supply voltage.

remains constant afterward until the next clock cycle, leading to fully dynamic power consumption.

Similarly, the proposed SEFIA is also fully dynamic, as shown in Fig. 5. Furthermore, the amplifier's speed tracks the clock frequency  $f_S$ . For a lower  $f_S$ ,  $C_{RES1}$  has more time to discharge during  $\Phi 1$ , and it can be shown that assuming weak inversion operation, the  $V_{GS}$ 's of  $M_{N1,2}$  and  $M_{P1,2}$  reduces logarithmically with time t due to the exponential  $I_D - V_{GS}$

Fig. 5. Time-domain behavior of the proposed SEFIA during the amplification phase.

Fig. 6. Equivalent circuit for evaluating the settling errors of the SC integrator based on (a) SEFIA and (b) conventional amplifier with constant  $g_{\rm M}$ .

relation [22], i.e.,

$$V_{\rm GS} \sim -\ln(at+b) \tag{3}$$

where a and b are constants related to device parameters and capacitance values (see the Appendix). Since the  $g_{\rm M}$ - $V_{\rm GS}$  relation is also exponential, we have

$$g_{\rm M} \sim \exp(V_{\rm GS}) \sim \frac{1}{at+b}.$$

(4)

For the low-BW applications of this work, the clock period is large, and  $g_{\rm M}$  becomes approximately proportional to  $f_{\rm S}$ .

Since  $g_M$  changes with time, we consider the effective  $g_M$  by evaluating the settling error of the SEFIA and compare it with that of a conventional amplifier with a constant  $g_M$  using the equivalent circuits shown in Fig. 6 and assuming

|                      | This Work | ISSCC'18<br>Gagnon-<br>Turcotte | ISSCC'18<br>Yeknami | ISSCC'19<br>Konijnenburg | ISSCC'20<br>Jang | ISSCC'18<br>Chandrakumar |

|----------------------|-----------|---------------------------------|---------------------|--------------------------|------------------|--------------------------|

| Process (nm)         | 180       | 130                             | 65                  | 55                       | 110              | 65                       |

| Architecture         | SCSD      | SCSD                            | SCSD                | SAR                      | CTSD             | CTSD                     |

| BW/Power<br>Scalable | Yes       | No                              | No                  | Yes                      | No               | No                       |

| Area (mm²)           | 0.75      | -                               | -                   | -                        | 0.078            | 0.053                    |

| V <sub>DD</sub> (V)  | 1.5       | 1.2                             | 0.3                 | 0.9                      | 1                | 1.2                      |

| Power (μW)           | 4         | 4.4                             | 0.18                | 0.9                      | 6.5              | 4.5                      |

| f <sub>S</sub> (Hz)  | 200k      | 500k                            | 256k                | 32k                      | 1280k            | 400k                     |

| OSR                  | 125       | 25                              | 42.7                | 107                      | 64               | 40                       |

| BW (Hz)              | 800       | 7k                              | 3k                  | 150                      | 10k              | 5k                       |

| DR (dB)              | 94.1      | -                               | -                   | -                        | 81               | 96.5                     |

| SNDR (dB)            | 89.3      | 60.8                            | 60                  | 78.8                     | 80.4             | 93.5                     |

| FoM <sub>DR</sub>    | 177.1     | -                               | -                   | -                        | 172.9            | 187.0                    |

| FoM <sub>SNDR</sub>  | 172.3     | 154.4                           | 162.2               | 161                      | 172.3            | 184.0                    |

TABLE I

PERFORMANCE SUMMARY AND COMPARISON

infinite dc gain. For the SEFIA, we then define the effective transconductance  $g_{M,eff}$  to be equal to the  $g_{M}$  of a conventional amplifier with the same settling error  $E_{settle}$  at the end of the  $\Phi 2$ . From the conventional amplifier, we have

$$g_{\text{M,eff}} = -\frac{2f_S C_O}{\beta} \ln E_{\text{settle}}$$

(5)

where  $C_O$  is the total load capacitance and  $\beta$  is the feedback factor around the amplifier. For the SEFIA, the following can be derived (see the Appendix)

$$E_{\text{settle}} = \left(\frac{t}{\alpha} + 1\right)^{-\frac{C_{\text{RES2}}}{C_O}} \tag{6}$$

where  $\alpha = (nU_T/I_{D0})(L/W)C_{RES2}\exp(((V_{GP}(T_S/2) - V_{DD})/nU_T))$ .

Combining (5) and (6), we have

$$g_{\text{M,eff}} = \frac{2f_{\text{S}}C_{\text{RES2}}}{\beta} \ln \left(\frac{1}{2\alpha f_{\text{S}}} + 1\right). \tag{7}$$

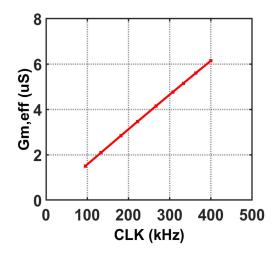

Fig. 7 plots the simulated  $g_{M,eff}$ , as a function of  $f_S$ , which is almost linear.

#### D. Power Efficiency

As shown in Fig. 6, the reduction in  $\log(E_{\rm settle})$  equals the integral of  $g_{\rm M}(t)$  over time. In other words, to achieve the same settling accuracy, the time-averaged  $g_{\rm M}$  of the SEFIA and the conventional amplifier is the same. Therefore, assuming similar  $g_{\rm M}/I_{\rm D}$  ratio and the same settling accuracy, the two amplifiers will consume a similar amount of power in the amplification phase.

#### IV. DTDSM WITH SEFIA

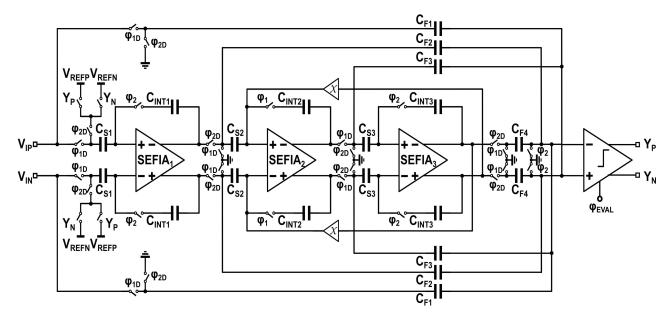

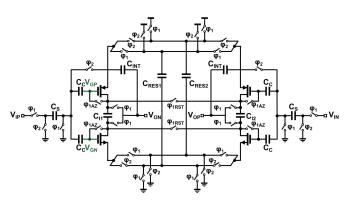

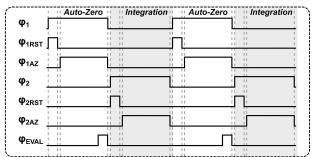

Fig. 8 shows the third-order DTDSM employing the proposed SEFIA. It employs a feedforward topology for low

Fig. 7.  $G_{m,eff}$  versus CLK frequency of the proposed SEFIA.

distortion and optimally spread NTF zeros for high signal-to-quantization-noise ratio (SQNR), and passive feedforward summation is implemented using  $C_{\rm Fl-3}$ . The input sampling capacitors are sized to 1 pF to meet the kT/C noise requirement. The 1-bit quantizer is composed of an FIA-based preamplifier and a StrongArm latch. The optimized NTF zeros are implemented with another SC sampling branch (shown as x for simplicity in Fig. 8). Each of the integrators has its own set of  $C_{\rm RES1}$  and  $C_{\rm RES2}$  and is optimized according to its noise and swing requirements. The SEFIAs are designed for 50 dB of dc gain. The resulting finite dc gain impact on SQNR is negligible according to MATLAB simulations.

Fig. 9 shows the complete schematic of the SEFIA-based SC integrator and its timing diagram. A short reset pulse is used at the beginning of  $\Phi 1$  to remove any differential voltage

Fig. 8. Circuit schematic of the  $\Delta \Sigma$  modulator.

Fig. 9. Circuit schematic of the SEFIA-based SC integrator and the corresponding timing diagram.

at the top and bottom plates of  $C_{\rm I1-2}$  and ensure that the AZ operation is signal-independent.

#### V. MEASUREMENT RESULT

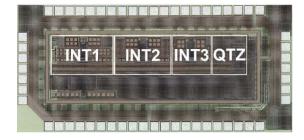

The modulator is fabricated in a 180-nm standard CMOS technology and occupies 0.75 mm<sup>2</sup>. Fig. 10 shows the chip microphotograph. At 200-kHz  $f_{\rm S}$ , the DTDSM consumes 4  $\mu{\rm W}$  from a 1.5-V supply.

Fig. 10. Chip micrograph of the  $\Delta\Sigma$  modulator.

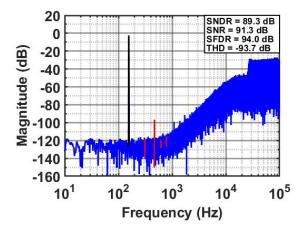

Fig. 11. Measured output spectrum at 200-kHz  $f_{\rm S}(500{\rm k}$  points). Harmonic distortion bins are plotted in red.

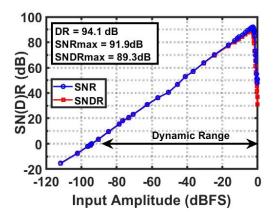

Fig. 11 shows the output spectrum at 200 kHz  $f_S$ . The DTDSM achieves a peak SNDR of 89.3 dB. Fig. 12 shows the measured SN(D)R performance over input amplitude at a 1.5-V supply. The prototype achieves a dynamic range (DR) of 94.1 dB. To verify the performance over supply voltage variations, Fig. 13 shows the measured SN(D)R of the DTDSM

Fig. 12. Measured SN(D)R versus input amplitude at  $f_S = 200$  kHz.

Fig. 13. Measured SN(D)R versus  $V_{DD}$ .

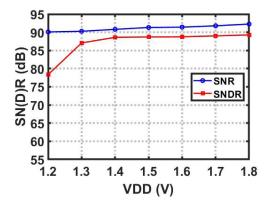

when the supply and reference are varied together from 1.3 to 1.8 V. The SNDR remains above 87 dB, demonstrating the robustness of the proposed SEFIA to supply voltage variations. At low supply, the SNR is lower since the full-scale input amplitude reduces when the supply voltage and reference are reduced. Toward 1.2 V, the SNDR drops because the amplifier swing becomes too small.

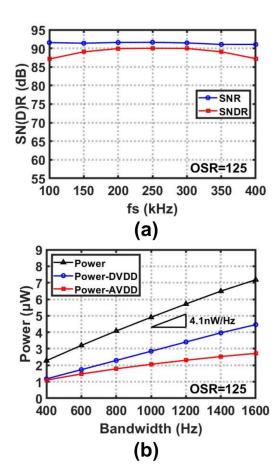

Fig. 14(a) presents the performance for various clock frequencies at 1.5-V supply. Due to the BW scalability of the SEFIA, the SNDR remains above 87 dB for  $f_{\rm S}$  between 100 and 400 kHz. At high  $f_{\rm S}$ , the SNDR slightly drops due to the reduced output swing. At low  $f_{\rm S}$ , the SEFIA's driving ability reduces, as mentioned in Section III. Although the small-signal effective  $g_{\rm M}$  scales linearly with  $f_{\rm S}$ , the large-signal performance degrades because the transistors operate in deeper subthreshold, causing the drop in the SNDR. The power consumption also scales with  $f_{\rm S}$ , from 2.2 to 7  $\mu$ W, as shown in Fig. 14(b).

Table I shows the performance summary and comparison with other state-of-the-art microwatt-level ADCs with similar BW. This is the first power/BW scalable DTDSM, due to the capacitive biased SEFIA. Moreover, it achieves the highest SNDR among the power/BW ADCs while maintaining high energy efficiency. The single-bit DTDSM achieves a Schreier figure of merit (FoM) of FOM<sub>DR</sub> of 177.1 dB and FOM<sub>SNDR</sub> of 172.3 dB, which are among the best reported for single-bit DTDSM designs.

Fig. 14. (a) Measured SN(D)R versus  $f_{\rm S}$  when OSR = 125. (b) Power consumption versus signal BW at  $V_{\rm DD}=1.5~{\rm V}.$

#### VI. CONCLUSION

In this article, a capacitively biased FIA is presented, which features a wide voltage swing that increases with the supply voltage and a scalable BW that adapts to the clock frequency. A DTDSM employing the proposed SEFIA-based integrators is implemented, demonstrating comparable power efficiency to state-of-the-art DTDSM and features scalable BW and power over two octaves of the sampling frequency range. The proposed SEFIA is thus a promising candidate for implementing power-efficient, fully dynamic SC circuits.

#### APPENDIX

#### DETAILED ANALYSIS OF THE SEFIA

Since the SEFIA is used for a low-power application in this work, the transistors mainly operate in weak inversion to take advantage of the high  $g_{\rm M}/I_{\rm D}$  ratio. When the transistor's  $V_{DS}$  exceeds  $3U_T$  to  $5U_T$  ( $\sim$ 130 mV), the drain current can be expressed as

$$I_{DS} = I_{D0} \frac{W}{L} \exp\left(\frac{V_{GS}}{nU_T}\right) \tag{8}$$

where  $I_{D0}$  is a process-dependent parameter of the transistor, n is the slope factor in weak inversion, and  $U_T$  is the thermal voltage kT/q. The transconductance is then given by

$$g_{\rm M} = \frac{\partial I_D}{\partial V_{\rm GS}} = \frac{I_{\rm D0}}{nU_T} \frac{W}{L} \exp\left(\frac{V_{\rm GS}}{nU_T}\right). \tag{9}$$

During the AZ operation,  $C_{RES1}$  discharges into  $C_I$  through the diode-connected transistors (Fig. 3). According to charge conservation,

$$C_{\text{RES1}}(V_{\text{DD}} - (V_{\text{SP1}}(t) - V_{\text{SN1}}(t)))$$

$$= (C_C + 2C_I)(V_{\text{GP}}(t) - V_{\text{GN}}(t))$$

$$+ C_C(V_{\text{GP}}(T_S/2) - V_{\text{GN}}(T_S/2)). \quad (10)$$

Since the current flowing through the two terminals of each capacitor  $C_I$ ,  $C_{RES1}$ , and  $C_{RES2}$  must be equal, we have

$$V_{\rm GP}(t) + V_{\rm GN}(t) = V_{\rm GP}(T_S/2) + V_{\rm GN}(T_S/2)$$

(11)

$$V_{\text{SP1}}(t) + V_{\text{SN1}}(t) = V_{\text{SP1}}(T_S/2) + V_{\text{SN1}}(T_S/2)$$

(12)

$$V_{\text{SP2}}(t) + V_{\text{SN2}}(t) = V_{\text{SP2}}(T_S/2) + V_{\text{SN2}}(T_S/2).$$

(13)

Here,  $V_{\rm GP}(T_S/2)$  and  $V_{\rm GN}(T_S/2)$  are the final values of the PMOS and NMOS gate voltages, respectively.  $V_{\rm SP1}(T_S/2)$  and  $V_{\rm SN1}(T_S/2)$  are the final voltages at the two terminals of  $C_{\rm RES1}$ . Similarly,  $V_{\rm SP2}(T_S/2)$  and  $V_{\rm SN2}(T_S/2)$  are the final voltages at the two terminals of  $C_{\rm RES2}$ . The sum of  $V_{\rm SP1}(T_S/2)$  and  $V_{\rm SN1}(T_S/2)$  is equal to the supply voltage if the PMOS and NMOS transistors have the same  $I_{\rm D0}W/L$  (implying the same  $g_{\rm M}$ ), so is the sum of  $V_{\rm SP2}(T_S/2)$  and  $V_{\rm SN2}(T_S/2)$ .

When  $C_{RES1}$  discharges into  $C_I$ , we have

$$-C_{\text{RES1}}\frac{dV_{\text{SP1}}(t)}{dt} = I_{\text{D0}}\frac{W}{L}\exp\left(\frac{V_{\text{SP1}}(t) - V_{\text{GP}}(t)}{nU_T}\right). \tag{14}$$

Combining (8), (10)–(12), and (14), and assuming  $g_{\rm M}$  of the NMOS and PMOS transistor are the same,  $V_{\rm GP}$  at the end of  $\Phi 1$  (as a function of the clock frequency) can be derived as

$$V_{GP}(f_S)|_{t=T_s/2} = \frac{C_{RES1}}{2C_I + C_{RES1}} nU_T \ln\left(\zeta \frac{1}{2f_S}\right) + \frac{C_{RES1} + C_I}{2C_I + C_{RES1}} V_{DD}$$

(15)

where

$$\zeta = \frac{1+\gamma}{nU_T} \frac{I_{\text{D0}}}{C_{\text{RFS1}}} \frac{W}{L} \tag{16}$$

and

$$\gamma = \frac{C_{\text{RES1}}}{2C_L + C_C}.\tag{17}$$

Similarly, during the amplification phase, we have

$$-C_{\text{RES2}} \frac{dV_{\text{SP2}}(t)}{dt} = I_{\text{D0}} \frac{W}{L} \exp\left(\frac{V_{\text{SP2}}(t) - V_{\text{GP}}(T_{\text{S}}/2)}{nU_{T}}\right). \tag{18}$$

Combining (9), (13), and (18), and according to the small-signal model [Fig. 6(a)], the normalized error  $E_{\text{settle}}$  of the charge-transfer process can be calculated as follows:

$$E_{\text{settle}} = \left(\frac{t}{\alpha} + 1\right)^{-\frac{C_{\text{RES2}}}{C_O}} \tag{19}$$

where

$$\alpha = \frac{nU_T}{I_{D0}} \frac{L}{W} C_{RES2} \exp\left(\frac{V_{GP}(T_S/2) - V_{DD}}{nU_T}\right). \tag{20}$$

Therefore, the effective transconductance  $g_{M,eff}$  can be expressed as

$$g_{\text{M,eff}} = \frac{2f_{\text{S}}C_{\text{RES2}}}{\beta} \ln\left(\frac{1}{2\alpha f_{\text{S}}} + 1\right). \tag{21}$$

Combining (15)–(17), (20), and (21),  $g_{M,eff}$  can be written as

$$g_{\text{M,eff}} = \frac{2f_S C_{\text{RES2}}}{\beta} \ln \left( \lambda \left( \frac{1}{f_S} \right)^{\frac{C_I}{2C_I + C_{\text{RESI}}}} + 1 \right)$$

(22)

where

$$\lambda = \frac{I_{\text{D0}}}{2nU_T} \frac{W}{L} \frac{1}{C_{\text{RES2}}} \exp\left(\frac{C_I}{2C_I + C_{\text{RES1}}} \frac{V_{\text{DD}}}{nU_T}\right)$$

$$\cdot \left(\frac{1 + \gamma}{2nU_T} \frac{I_{\text{D0}}}{C_{\text{RES1}}} \frac{W}{L}\right)^{-\frac{C_{\text{RES1}}}{2C_I + C_{\text{RES1}}}}.$$

(23)

#### REFERENCES

- P. Harpe, E. Cantatore, and A. van Roermund, "A 10b/12b 40 kS/s SAR ADC with data-driven noise reduction achieving up to 10.1b ENOB at 2.2 fJ/conversion-step," *IEEE J. Solid–State Circuits*, vol. 48, no. 12, pp. 3011–3018, Dec. 2013.

- [2] P. Harpe, H. Gao, R. V. Dommele, E. Cantatore, and A. H. M. van Roermund, "A 0.20 mm<sup>2</sup> 3 nW signal acquisition IC for miniature sensor nodes in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 51, no. 1, pp. 240–248, Jan. 2016.

- [3] D. Zhang, A. Bhide, and A. Alvandpour, "A 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-μm CMOS for medical implant devices," *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1585–1593, Jul. 2012.

- [4] H. Zhang et al., "A 1-V 560-nW SAR ADC with 90-dB SNDR for IoT sensing applications," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 12, pp. 1967–1971, Dec. 2019.

- [5] M. Ding, P. Harpe, Y. Liu, B. Busze, K. Philips, and H. D. Groot, "A 46 μW 13 b 6.4 MS/s SAR ADC with background mismatch and offset calibration," *IEEE J. Solid-State Circuits*, vol. 52, no. 2, pp. 423–432, Feb. 2017.

- [6] J. Shen et al., "A 16-bit 16MS/s SAR ADC with on-chip calibration in 55nm CMOS," in Proc. Symp. VLSI Circuits, Jun. 2017, pp. C282–C283.

- [7] H. Li, M. Maddox, M. C. W. Coin, W. Buckley, D. Hummerston, and N. Naeem, "A signal-independent background-calibrating 20b 1MS/S SAR ADC with 0.3ppm INL," in *IEEE Int. Solid-State Circuits Conf.* (ISSCC) Dig. Tech. Papers, Feb. 2018, pp. 242–244.

- [8] Y. Chae and G. Han, "Low voltage, low power, inverter-based switched-capacitor delta-sigma modulator," *IEEE J. Solid-State Circuits*, vol. 44, no. 2, pp. 458–472, Feb. 2009.

- [9] Y. Chae, K. Souri, and K. A. A. Makinwa, "A 6.3 μW 20 bit incremental zoom-ADC with 6 ppm INL and 1 μV offset," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3019–3027, Dec. 2013.

- [10] S. Karmakar, B. Gonen, F. Sebastiano, R. van Veldhoven, and K. A. A. Makinwa, "A 280 μ W dynamic zoom ADC with 120 dB DR and 118 dB SNDR in 1 kHz BW," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3497–3507, Dec. 2018.

- [11] E. Eland, S. Karmakar, B. Gonen, R. van Veldhoven, and K. A. A. Makinwa, "A 440-μW, 109.8-dB DR, 106.5-dB SNDR discrete-time zoom ADC with a 20-kHz BW," *IEEE J. Solid-State Circuits*, vol. 56, no. 4, pp. 1207–1215, Apr. 2021.

- [12] H. Zhang et al., "A 6 μ W 95 dB SNDR inverter based Σ Δ modulator with subtractive dithering and SAR quantizer," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 66, no. 4, pp. 552–556, Apr. 2019.

- [13] G. Gagnon-Turcotte, C. Ethier, Y. De Koninck, and B. Gosselin, "A 13μm CMOS SoC for simultaneous multichannel optogenetics and electrophysiological brain recording," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 466–468.

- [14] M. ElAnsary et al., "50nW opamp-less ΔΣ-modulated bioim-pedance spectrum analyzer for electrochemical brain interfacing," IEEE J. Solid-State Circuits, vol. 55, no. 7, pp. 1971–1983, Jul. 2020.

- [15] B. Gönen, F. Sebastiano, R. Quan, R. van Veldhoven, and K. A. A. Makinwa, "A dynamic zoom ADC with 109-dB DR for audio applications," *IEEE J. Solid-State Circuits*, vol. 52, no. 6, pp. 1542–1550, Jun. 2017.

- [16] S. Lee, W. Jo, S. Song, and Y. Chae, "A 300-μW audio ΔΣ modulator with 100.5-dB DR using dynamic bias inverter," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 11, pp. 1866–1875, Nov. 2016.

- [17] X. Tang et al., "An energy-efficient comparator with dynamic floating inverter amplifier," *IEEE J. Solid-State Circuits*, vol. 55, no. 4, pp. 1011–1022, Apr. 2020.

- [18] X. Tang et al., "9.5 A 13.5b-ENOB second-order noise-shaping SAR with PVT-robust closed-loop dynamic amplifier," in *IEEE Int.* Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2020, pp. 162–164.

- [19] Y. Zhao et al., "A 94.1 dB DR 4.1 nW/Hz bandwidth/power scalable DTDSM for IoT sensing applications based on swing-enhanced floating inverter amplifiers," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), Apr. 2021, pp. 1–2.

- [20] T. Christen, "A 15-bit  $140-\mu$  W scalable-bandwidth inverter-based  $\Delta\Sigma$  modulator for a MEMS microphone with digital output," *IEEE J. Solid-State Circuits*, vol. 48, no. 7, pp. 1605–1614, Jul. 2013.

- [21] H. Luo, Y. Han, R. C. C. Cheung, X. Liu, and T. Cao, "A 0.8-V 230-μW 98-dB DR inverter-based ΣΔ modulator for audio applications," *IEEE J. Solid-State Circuits*, vol. 48, no. 10, pp. 2430–2441, Oct. 2013.

- [22] M. S. Akter, K. A. A. Makinwa, and K. Bult, "A capacitively degenerated 100-dB linear 20–150 MS/s dynamic amplifier," *IEEE J. Solid-State Circuits*, vol. 53, no. 4, pp. 1115–1126, Apr. 2018.

Menglian Zhao (Member, IEEE) received the M.S. degree in microelectronics and solid-state circuits and the Ph.D. degree in engineering circuits and systems from Zhejiang University, Hangzhou, China, in 2001 and 2004, respectively.

She joined the College of Electrical Engineering, Zhejiang University, in 2004. From 2005 to 2006, she was a Research Assistant with the Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Hong Kong. She is currently an Associate Professor

with the College of Information Science and Electronic Engineering, Zhejiang University. Her current interests include CMOS analog and mixed-signal integrated circuit design, low-power techniques for integrated circuits, and SoC.

Yibo Zhao (Student Member, IEEE) received the B.E. degree in microelectronices science and engineering from the Hefei University of Technology, Hefei, China, in 2017. He is currently pursuing the Ph.D. degree with the College of Information Science and Electronic Engineering, Zhejiang University, Hangzhou, China.

His current research mainly focuses on ultralow-power data converters.

Huajun Zhang (Graduate Student Member, IEEE) received the B.E. degree in electrical and computer engineering from Shanghai Jiao Tong University, Shanghai, China, in 2015, and the B.S.E. and M.S. degrees in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2015 and 2017, respectively. He is currently pursuing the Ph.D. degree with the Delft University of Technology, Delft, The Netherlands.

In summer 2016, he was an Analog/Mixed-Signal Design Intern with Analog Devices, Inc., Wilmington, MA, USA. From May 2017 to February 2019, he was a Mixed Signal Design Engineer with Analog Devices, Inc., Norwood, MA, USA. He joined the Electronic Instrumentation Laboratory, Delft University of Technology, in March 2019. He holds one U.S. patent. His technical interests include precision analog circuits, class-D audio amplifiers, and ultra-low-power data converters.

Mr. Zhang has served as a Reviewer for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS and the IEEE SENSORS JOURNAL.

Yaopeng Hu (Student Member, IEEE) received the B.E. degree in electrical and electronics engineering from Zhejiang University, Hangzhou, China, in 2019, where he is currently pursuing the M.Sc. degree.

His current research interests include analog-todigital conversion and floating inverter amplifier.

Yuanxin Bao received the B.S. degree in microelectronics and the M.S. degree in circuits and systems from the Guilin University of Electronic Technology, Guilin, China, in 2010 and 2013, respectively, and the Ph.D. degree from the School of Information Science and Engineering, Southeast University, Nanjing, China, in 2019.

In 2019, he was with the Advanced Institute of Information Technology, Peking University, Beijing, China, as an IC Design Engineer working on low-power high-precision analog/mixed-signal cir-

cuit design. In 2020, he joined Peking University as a Post-Doctoral Researcher. His current research interests include energy-efficient sensor interfaces, precision analog circuits, and analog-to-digital converters.

Le Ye (Member, IEEE) was born in Jiangsu, China, in 1983. He received the B.S. degree (Hons.) in physics from the Department of Physics, Nanjing University, Nanjing, China, in 2005, and the Ph.D. degree in microelectronics from the Institute of Microelectronics, Peking University, Beijing, China, in 2010

From April 2009 to April 2010, he was a Visiting Scholar with the Institute of Circuits and Systems, Dresden University of Technology, Dresden, Germany. Since 2010, he has been a Fac-

ulty Member with Peking University, where he is currently an Associate Professor. He is currently the Dean of the IoT Research Center, Advanced Institute of Information Technology, Peking University. He has authored or coauthored more than 40 articles. He holds over 20 granted patents. His research interests include analog and mixed-signal integrated circuit (IC) design, ultra-low-power IC design, computing-in-memory artificial intelligence (AI) chip design, and implanted IC and micro-system for medical applications

Dr. Ye was a recipient of the National Science Fund for Outstanding Young Scholars and the Beijing New-star Plan of Science and Technology in China. He has been an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS since 2020.

Wanyuan Qu (Member, IEEE) received the B.S. degree from the Beijing University of Posts and Telecommunications, Beijing, China, in 2006, and the M.S. and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology, Daejeon, South Korea, in 2008 and 2016, respectively.

He was with Silicon Works Ltd., Daejeon, from 2008 to 2017 as a Principle Circuit Design Engineer. Since 2017, he has been with Zhejiang University, where he is currently an Associate Pro-

fessor. He has been granted with eight U.S. patents and five Korean patents. His current research interests include high-power-density dc-dc converters, GaN drivers and converters, energy harvesters, and high-performance amplifiers.

Dr. Qu serves as an Associate Editor for *Journal of Engineering* (IET) and a member of the Technical Program Committee (TPC) of IEEE Asian Solid-State Circuits Conference and IEEE Integrated Circuits, Technologies and Applications.

Zhichao Tan (Senior Member, IEEE) received the B.Eng. degree from Xi'an Jiaotong University, Xi'an, China, in 2004, the M.Eng. degree from Peking University, Beijing, China, in 2008, and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2013.

He was a Staff IC Design Engineer working on low-power high-precision analog/mixed-signal circuit design with Analog Devices, Inc., Wilimington, MA, USA, from 2013 to 2019. In 2019, he joined Zhejiang University, Hangzhou, China, as a Faculty

Member. He holds five U.S. patents and authored or coauthored more than 30 technique papers. His current research interests are in the areas of energy-efficient sensor interfaces, precision analog circuits, and ultra-low-power analog-to-digital converters (ADCs).

Dr. Tan was a Technical Program Committee (TPC) Member of IEEE Asian Solid-State Circuits Conference, IEEE Sensors Conference, and IEEE International Instrumentation and Measurement Technology Conference. He was the Chair of the IEEE Industrial Electronics Society Technical Committee on MEMS and Nanotechnology from 2019 to 2020. He has served as an Associate Editor for the IEEE Transactions on Circuits and Systems—I: Regular Papers and IEEE Transactions on Industrial Electronics. He is currently an Associate Editor of the IEEE Sensors Journal.