Delft University of Technology

# A 23.8–30.4-GHz Vector-Modulated Phase Shifter With Two-Stage Current-Reused Variable-Gain Amplifiers Achieving 0.23° Minimum RMS Phase Error

Zhang, Linghan; Shen, Yiyu; de Vreede, Leo; Babaie, Masoud

DOI 10.1109/LSSC.2022.3179661

**Publication date** 2022 **Document Version** Final published version

Published in **IEEE Solid-State Circuits Letters**

# Citation (APA)

Zhang, L., Shen, Y., de Vreede, L., & Babaie, M. (2022). A 23.8–30.4-GHz Vector-Modulated Phase Shifter With Two-Stage Current-Reused Variable-Gain Amplifiers Achieving 0.23° Minimum RMS Phase Error. IEEE Solid-State Circuits Letters, 5, 150-153. Article 9786764. https://doi.org/10.1109/LSSC.2022.3179661

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

# 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# A 23.8–30.4-GHz Vector-Modulated Phase Shifter With Two-Stage Current-Reused Variable-Gain Amplifiers Achieving 0.23° Minimum RMS Phase Error

Linghan Zhang<sup>(D)</sup>, *Graduate Student Member, IEEE*, Yiyu Shen<sup>(D)</sup>, *Member, IEEE*, Leo de Vreede<sup>(D)</sup>, *Senior Member, IEEE*, and Masoud Babaie<sup>(D)</sup>, *Member, IEEE*

Abstract-This letter presents a millimeter-wave (mm-wave) vectormodulated phase shifter (VMPS) for phased-array applications. To improve the phase-shift accuracy without drastically increasing design complexity, the proposed VMPS structure employs variable-gain amplifiers (VGAs) that offer 2x better resolution at their low-gain states compared to their high-gain states. A two-stage current-reused structure is also proposed to implement the desired VGAs with minimal layout complexity, negligible gain penalty, and no extra power. Moreover, the proposed VMPS can maintain its phase-shift accuracy even at lower voltage gains. Fabricated in 40-nm CMOS, the prototype core consumes 11 mW from a 1.1-V supply and occupies a core area of 0.19 mm<sup>2</sup>. At 28 GHz, with a phase resolution of 0.61°, the measured RMS phase error is 0.23° at the maximum gain and remains <0.5° at 9-dB gain back-off. With a fixed set of VGA's codewords, the RMS phase error and gain variation error are, respectively, lower than 1° and 0.24-dB over a bandwidth of 23.8-30.4 GHz.

Index Terms—Active phase shifter, millimeter-wave (mm-wave), phased-array systems, two-step variable gain amplifier, vector-modulator.

#### I. INTRODUCTION

Phased-array transceivers are widely exploited in the emerging millimeter-wave (mm-wave) systems to improve the communication range and channel capacity. A phase shifter is one of the critical elements in those systems, as its phase resolution and accuracy directly affect the beam's directivity, steering resolution, and pointing accuracy. Compared to passive phase shifters, the vector-modulator-based active ones are more attractive due to their superior performance in terms of chip area, insertion loss, and phase accuracy. Besides, they can accurately control the signal magnitude to realize spatial interference nulling [1]. Fig. 1 shows a simplified diagram of a vector-modulated phase shifter (VMPS). It consists of a network to generate the required in-phase (I) and quadrature (Q) signals, two variable-gain amplifiers (VGAs) with weights of  $G_I$  and  $G_O$ , and a current-domain combiner to synthesize the desired phase shift,  $\theta = (180/\pi) \arctan(G_O/G_I)$ . Each VGA is usually realized by *n*-bit current-steering cells [2] to enable linear gain control. As a result, due to the quantization noise, the worst-case phase error of a digitally controlled VMPS may be estimated by half of its phase resolution,

$$\theta_{e,q} = (180/\pi) \arctan(1/N)/2 \approx 90/(\pi N) = 90/(\pi 2^n).$$

(1)

The design of a VMPS also comes with several challenges. First, as indicated in (1),  $\theta_{e,q}$  can only be improved by increasing the number of VGA cells,  $N = 2^n$ , in the conventional VMPSs. However, at mm-wave frequencies, since this approach dramatically adds the layout complexity, the phase error related to layout mismatch or routing

Manuscript received March 5, 2022; revised May 3, 2022; accepted May 24, 2022. Date of publication June 2, 2022; date of current version June 10, 2022. This work was supported in part by the NWO under Project 17303. This article was approved by Associate Editor M. Hossain. (*Corresponding author: Linghan Zhang.*)

The authors are with the Department of Microelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: l.zhang-6@tudelft.nl).

Digital Object Identifier 10.1109/LSSC.2022.3179661

(a) (b)

Fig. 1. (a) Block diagram. (b) Basic operation of a VMPS.

parasitics grows significantly, which in turn counteracts the effect of the added cells. Second, by increasing n by 1 bit, not only the number of cells is doubled, but also the area of VGA's unit cell must be largened by  $2 \times$  to keep the differential nonlinearity (DNL) of the VMPS constant if the binary control is applied. As a result, the VMPS's output parasitic capacitance increases by  $4 \times$ , thus lowering its voltage gain dramatically if the power consumption is kept constant. In addition, the conventional VMPS exhibits larger phase errors at lower gain states due to the reduced effective gain resolution of the VGAs. This would degrade the rejection provided by interference nulling in a phased-array system.

To address these issues, this letter introduces a VMPS structure using a novel two-stage current-reused VGA. With a negligible increase in the number of current-steering cells and output capacitance, the proposed VGA offers  $2\times$  better resolution at low-gain states, thus enabling the VMPS to improve its phase resolution considerably without compromising the gain and power consumption. This letter is organized as follows. Our system-level solution for improving the VMPS phase accuracy is discussed in Section II. Section III reveals and analyzes the circuit details of the proposed VMPS and VGA. The measurement results are shown in Section IV, followed by conclusions in Section V.

#### **II. PHASE SHIFTER SYSTEM DESIGN**

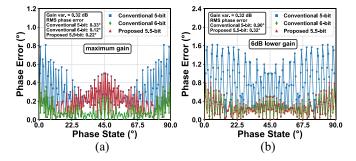

To gain more insight and improve the phase-shift accuracy, the phase error of an ideal VMPS with unsigned 5-bit VGAs (i.e., each consisting of 32 unit cells) is simulated, and the corresponding results of the first quadrant are shown in Fig. 2. Given a ~0.3 dB gain variation for different phase settings, the largest phase-shifting errors occur near 0° and 90°, where either  $G_I$  or  $G_Q$  is small. Hence, by improving the VGAs' gain resolution merely at the lower gain settings, the phase error around 0° and 90° can greatly be reduced.

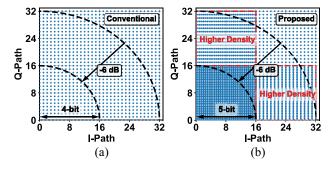

Fig. 3 compares the constellation diagrams of the conventional and proposed VMPS in the first quadrant. The conventional one uses unsigned 5-bit VGAs with a gain range from 0 to 32 and a step size of one. However, the proposed VMPS employs VGAs that offer  $2\times$  better gain resolution (i.e., 0.5 instead of 1) at lower gain states (i.e., from 0 to 16). Consequently, the phase error of the

2573-9603 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 2. Comparison between the phase error of the conventional VMPSs using unsigned 5-bit and 6-bit one-stage VGAs, and the proposed VMPS using unsigned 5.5-bit two-stage VGAs at their (a) maximum gain and (b) 6-dB lower gain.

Fig. 3. First-quadrant constellation diagram of (a) conventional VMPS using unsigned 5-bit one-stage VGAs and (b) proposed VMPS using unsigned 5.5-bit two-stage VGAs.

proposed VMPS improves near 0° and 90°, as its constellation diagram shows a higher density in the vicinity of those angles. Thanks to this technique, the RMS phase error decreases from  $0.33^{\circ}$  to  $0.22^{\circ}$ , and the maximum phase error reduces to half, as shown in Fig. 2 (a). Although the phase error of the VMPS with 6-bit VGAs can be further improved, its voltage gain is lowered dramatically due to the largened output capacitance. Besides, considering the layoutrelated errors, the improvement of the phase-shift error would not be achieved as expected in practice.

As can be gathered from Figs. 2 (b) and 3, when the VMPS voltage gain is scaled down by 6 dB, the RMS phase error of the conventional VMPS worsens to 0.9° due to the 1-bit decrease in the effective gain resolution of the VGAs. In contrast, the proposed VMPS can maintain its phase-shift accuracy up to a 6-dB lower voltage gain since the VGA's resolution remains almost the same. The phase-shift accuracy can alternatively be maintained if an attenuator/VGA follows the conventional VMPS. However, compared with the proposed solution, it demands a larger power consumption and chip area.

Note that the abovementioned improvements could be achieved by increasing the current-steering cells to 48 instead of doubling them (i.e., using 64 cells). Nevertheless, the output capacitance still increases by  $\sim$ 50%, lowering the VGA's gain. Consequently, to further simplify the layout complexity and reduce gain penalty, the next section introduces a *two-stage* VGA structure that realizes the desired characteristics using only 36 current-steering cells. Among these cells, four are placed in the first stage and the rest in the second one, resembling the conventional 5-bit VGA. Thus, the increase of the output capacitance is negligible, and the gain will not be degraded.

#### **III. PHASE SHIFTER CIRCUIT DESIGN**

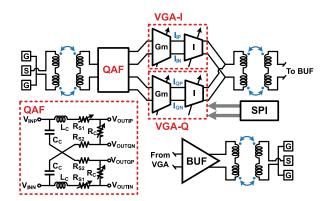

The block diagram of the proposed mm-wave phase shifter is shown in Fig. 4. A quadrature all-pass filter (QAF) [3] first generates the quadrature signals. The proposed two-stage current-reused phase-invariant VGAs then apply the desired gains to the I and Q signals. As the output buffer, a common-source differential amplifier is designed to drive the 50- $\Omega$  load and facilitate the measurements.

Fig. 4. Block diagram of the proposed phase shifter.

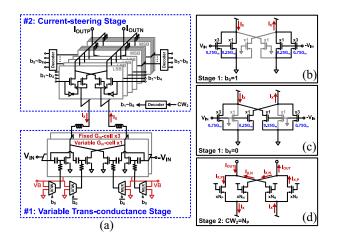

Fig. 5. (a) VGA schematic; Simplified schematics of the first stage when (b)  $b_1 = 1$  and (c)  $b_1 = 0$ . (d) Second stage when  $CW_2 = N_P$ .

Compared with poly phase filters, as a second-order network [3], the QAF structure can generate quadrature signals with larger bandwidth, lower voltage loss, and smaller form factor. However, its IQ mismatch would worsen at mm-wave frequencies since the load capacitance (i.e., the parasitic capacitance of the next stage) becomes non-negligible compared to the QAF coupling capacitance (i.e.,  $C_C$  in Fig. 4). To alleviate this issue, series resistors  $R_{S1}$  and  $R_{S2}$  are inserted into the  $L_C$  and  $C_C$  branches in the filter to make the QAF less sensitive to its load capacitance [3]. However, based on simulation results, the voltage gain of the QAF reduces by ~4 dB in this work. To deal with the PVT variations, the resistors  $R_{S1}$  and  $R_C$  are tunable with a range of  $\pm 10\%$  to limit the maximum I/Q phase and magnitude mismatch to about  $\pm^{\circ}$  and 0.5 dB, respectively.

#### A. Proposed Two-Stage VGA

Fig. 5 (a) shows the schematic of the proposed current-reused twostage phase-invariant VGA. The first stage consists of three fixed and one switchable trans-conductance (gm) cells with an identical size and a total trans-conductance gain of  $G_m$  (i.e., each cell  $G_m/4$ ). As shown in Fig. 5 (b) and (c), according to the control bit of the first stage ( $b_0 = 0$  or 1), the current of the switchable gm cell is added constructively or destructively to the current of the fixed cells. Hence, the output current of the first stage can be calculated by

$$I_{\rm X} = 0.5G_m(1+b_0) \times V_{\rm IN}$$

(2)

where  $V_{\text{IN}}$  is the input voltage. According to (2),  $I_{\text{X}}$  can have only two different values,  $0.5G_mV_{\text{IN}}$  and  $G_mV_{\text{IN}}$ .

The second stage employs a *signed* 5-bit (i.e.,  $2 \times 32$  cells in total) current-steering structure such that the entire constellation diagram and 0° to 360° phase shift can be covered by the VMPS. Each cell consists of four identical transistors that steer its differential input current to the output branches either positively (i.e.,  $I_X$  to the left

branch and  $-I_X$  to the right one) or negatively (i.e.,  $I_X$  to the right branch and  $-I_X$  to the left one). As illustrated in Fig. 5 (d), assuming that  $N_P$  and  $N_N$  cells, respectively, steer the current positively and negatively, the output current is calculated by

$$I_{\rm OUT} = I_{\rm X,P} - I_{\rm X,N} = I_{\rm X} [N_{\rm P}/N - N_{\rm N}/N]$$

(3)

where N = 64 is the total number of cells. To minimize the output phase variation over the gain states and cover larger bandwidth, the dc current and the input and output impedance of the current-steering structure should not change across all gain settings. Consequently, the total number of the ON-state (and OFF-state) transistors at each output node must be constant regardless of the gain state, leading to  $N = N_P + N_N$  and simplifying (3) to

$$I_{\rm OUT} = I_{\rm X} (2CW_2/N - 1) \tag{4}$$

where  $CW_2$  is the second stage codeword equal to  $N_P$  and can be changed from 0 to 64 with a step size of 1. Hence,  $I_{OUT}$  has 65 states from  $-I_X$  to  $I_X$  with a step of  $I_X/32$ . By exploiting (2) and (4), the total trans-conductance gain of the proposed VGA may be estimated as

$$G_{\rm VGA} = I_{\rm OUT} / V_{\rm IN} = G_m (1 + b_0) (CW_2 / N - 0.5).$$

(5)

To gain more insight,  $G_{VGA}$  is then normalized to  $G_m/N$

$$F_{\rm VGA,N} = (1+b_0) \times (CW_2 - 0.5N).$$

(6)

According to (6), the  $G_{VGA,N}$  range is -32–32 with a step size of 0.5 and 1 when  $|G_{VGA,N}|$  is 0–16 and 17–32, respectively. Therefore, by adding only one switchable gm cell in the first stage, the proposed VGA improves the gain resolution at low-gain states while keeping the number of current-steering cells in the second stage constant (i.e., using 2 × 32 cells instead of 2 × 48). This simplifies the layout complexity and reduces the input/output parasitic capacitance. Moreover, since the dc current is reused between the variable trans-conductance and current-steering stages, no extra power consumption is needed. Note that  $G_{VGA}$  is PVT sensitive as it is proportional to  $G_m$ . However, the phase shift of the VMPS is defined by  $\arctan(G_Q/G_I)$ . With the digitally controlled two-stage VGA structure, the ratio of  $G_Q$  to  $G_I$  of the proposed VMPS is determined by the number of the positive and negative cells in the Q and I VGAs. Hence, the VMPS phase-shift accuracy can be largely maintained over PVT variations.

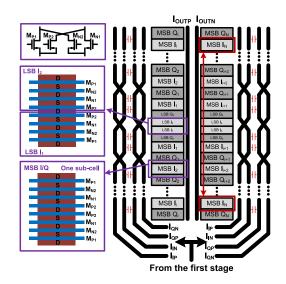

The sizes of VGA's transistors are determined based on the linearity and gain requirements. Note that the VGA's transfer function should be monotonic and without any missing codes to maintain the VMPS phase accuracy and resolution. Hence, the DNL of the VGAs is considered to determine the unit cells' size. In this work, a segmented thermometer-coded technique is also exploited in the current-steering stage to optimize the tradeoff between the VGA's DNL and layout complexity. As shown in Fig. 5 (a), the 64 unit cells are divided into four least-significant-bit (LSB) cells and 15 most-significant-bit (MSB) cells to enable the segmented thermometer-coded control. Each LSB cell consists of one unit, while each MSB cell contains four units (i.e.,  $N_{seg} = 4$ ). By applying the method in [4], and considering matching constraints, the active area ( $W \times L$ ) of each unit transistor in the current steering cells can be calculated by

$$W \times L = \frac{N_{\text{seg}} \left[ A_{\text{VTH}}^2 \left( g_{\text{m}} / I_{\text{D}} \right)^2 + A_{\beta}^2 \right]}{\text{DNL}_{\text{max}}^2}$$

(7)

where  $A_{\rm VTH} = 3 \text{ mV} \cdot \mu \text{m}$ , and  $A_{\beta} = 0.6\% \cdot \mu \text{m}$  are, respectively, the threshold-voltage and current-factor proportionality parameters in the 40-nm CMOS technology. By considering  $g_m/I_D = 5$  to optimize the device's maximum oscillation frequency ( $f_{\rm max}$ ) and using a minimum length transistor to reduce the output parasitic capacitance, Wshould be wider than 0.4 µm to achieve a maximum DNL DNL<sub>max</sub> of <0.25 LSB. On the other hand, by considering the desired voltage gain and the effective load resistance of the VMPS, the required  $G_m$ and size of the gm-cells' transistors can also be estimated.

Fig. 6. Layout floor-plan of the current-steering stage.

#### B. Layout Design of the VGA

A conventional VMPS typically uses two physically separated I and Q VGAs. However, due to gradients in the gate-oxide thickness and substrate doping, this approach results in a severe mismatch between the I and Q VGAs, thus degrading the phase-shift accuracy. Hence, as shown in Fig. 6, the I and Q current-steering cells are interleaved in the layout to alleviate this issue. Besides, the input feeding lines of I and Q current-steering cells are twisted to balance their parasitic capacitances. This alleviates the IQ gain imbalance caused by the mismatch between the load impedances of the gm stages of the I- and Q-VGAs. Each MSB cell is also divided into two subcells and placed symmetrically (see Fig. 6) to compensate for the phase shift along the input and output lines. Finally, the four transistors within one unit cell share their source and drain areas to reduce parasitic capacitance.

#### IV. IMPLEMENTATION AND MEASUREMENT

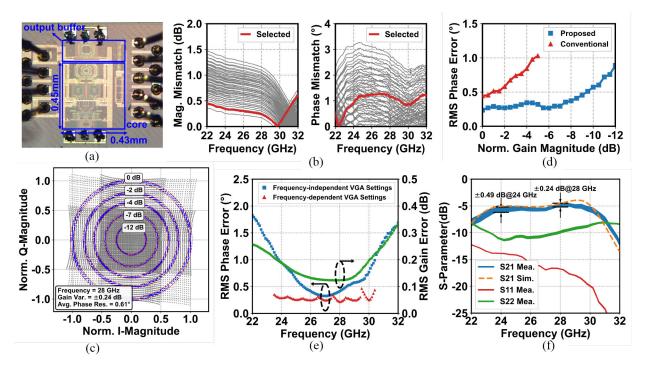

The proposed phase shifter is fabricated in 40-nm CMOS with a core area of  $0.19 \text{ mm}^2$ , as shown in Fig. 7 (a). The on-chip S-parameter measurement is done with Keysight vector network analyzer E8361A. The DC supplies and SPI control signals are wirebonded to a printed circuit board (PCB). The core circuit of the phase shifter consumes 11 mW under a 1.1-V supply voltage in all states, and the power consumption of the output buffer is 12 mW.

Before measuring the phase states, the  $R_{S1}$  and  $R_C$  are swept, and the corresponding IQ magnitude and phase mismatch of the QAF over operating frequency band are measured and shown in Fig. 7 (b). By choosing the optimum  $R_{S1}$  and  $R_C$  settings, the calibrated IQ magnitude and phase mismatch reach below 0.5 dB and 1.2° from 22 to 31.5 GHz. Note that the selected  $R_{S1}$  and  $R_C$  settings are fixed in all the following measurements.

Fig. 7 (c) shows the measured constellation diagram of the proposed VMPS at 28 GHz, resulting from sweeping all codewords of the *I* and *Q* VGAs. As expected, it shows a higher density at <6 dB gain back-off and also in the vicinity of  $0^{\circ}$ ,  $90^{\circ}$ ,  $180^{\circ}$ , and  $270^{\circ}$  rotation angles. Based on the measured constellation diagram, the RMS phase error of the proposed VMPS at different gain states is reported in Fig. 7 (d). The RMS phase error is  $0.23^{\circ}$  at the maximum gain and remains < $0.5^{\circ}$  even at a 9-dB gain back-off. In contrast, the RMS phase error of a conventional VMPS degrades drastically as its gain drops. Therefore, the reduced phase error of the proposed VMPS at lower gains improves the beam nulling in phased-array systems and thus increases the interference rejection by ~9 dB, according to [5].

Fig. 7 (e) shows the measured RMS phase and gain errors versus frequency in two different scenarios. In the first case, to minimize phase error and keep the gain error <0.24 dB, the VGAs settings

Fig. 7. (a) Chip micrograph; measured (b) IQ magnitude and phase mismatch for different  $R_{S1}$  and  $R_C$  settings. (c) Constellation diagram at 28 GHz. (d) RMS phase error versus the VMPS normalized gain. (e) RMS phase and gain errors. (f) S-parameters for all phase states.

TABLE I

COMPARISON OF STATE-OF-ART ACTIVE VMPSs

|                                                                                           | This Work                  | [2]<br>TMTT 20 | [6]<br>TCAS2 19 | [7]<br>TMTT 22            | [8]<br>TCAS2 22     |

|-------------------------------------------------------------------------------------------|----------------------------|----------------|-----------------|---------------------------|---------------------|

| Tech. (nm)                                                                                | 40                         | 65             | 45 (SOI)        | 65                        | 65                  |

| Freq. (GHz)                                                                               | 23.8~30.4                  | 51~66.3        | 27~33           | 55~65                     | 24~28               |

| Phase res. (°)                                                                            | 0.61                       | 11.25          | 5               | 11.25                     | 5.625               |

| RMS phase                                                                                 | 0.23~0.5*                  | 3~7            | 0.5~0.8         | 1.09                      | 1.4                 |

| error (º)                                                                                 | 0.32~1                     |                |                 |                           |                     |

| RMS gain                                                                                  | 0.13*                      | 0.25~          | 0.1             | 0.12                      | 0.25                |

| error (dB)                                                                                | 0.12~0.24                  | 0.72           |                 |                           |                     |

| Gain (dB)                                                                                 | -4.9 (-2.3 <sup>\$</sup> ) | -3.8           | -5.8            | 6.2 (-7.9 <sup>\$</sup> ) | -6.1                |

| Core area (mm <sup>2</sup> )                                                              | 0.19                       | 0.3            | 0.27            | 0.38                      | 0.27                |

| P <sub>DC</sub> (mW)                                                                      | 23 (11#)                   | 5              | 25              | 25.2 (10.6#)              | 31.9                |

| FoM1                                                                                      | 911 (1228 <sup>\$</sup> )  | 380.9          | 703.8           | 465.1                     | 214.6 <sup>\$</sup> |

| FoM <sub>2</sub>                                                                          | 39.6 (111 <sup>s</sup> )   | 76.18          | 28.15           | 18.46                     | 6.72 <sup>\$</sup>  |

| * Frequency-dependent control, # excluding the buffer, \$ VMPS only, simulated gain used. |                            |                |                 |                           |                     |

$F_{OM_{1}} = \frac{f_{0}(GHz) \times BW(GHz) \times Gain_{PS}(lin.) \times n_{PS}(bits)}{\theta_{error,RMS}(^{\circ}) \times A_{error,RMS}(lin.)} \\ F_{OM_{2}} = \frac{f_{0}(GHz) \times BW(GHz) \times Gain_{PS}(lin.) \times n_{PS}(bits)}{\theta_{error,RMS}(^{\circ}) \times A_{error,RMS}(lin.) \times n_{PS}(bits)} \\ + \frac{f_{0}(GHz) \times BW(GHz) \times Gain_{PS}(lin.) \times n_{PS}(bits)}{\theta_{error,RMS}(^{\circ}) \times A_{error,RMS}(lin.) \times n_{PS}(bits)}$

$n_{PS}(bits) = log_{2}[360/\theta_{res}(^{\circ})]$

for each phase-shift state are optimized in every 1-GHz band from 23.5–30.5 GHz. The minimum and maximum RMS phase errors (red curve) are  $0.23^{\circ}$ , and  $0.5^{\circ}$  over the operational bandwidth. Then, the VGAs settings for each phase-shift state are kept fixed over the bandwidth. In this case, the RMS phase/gain errors (blue and green curves) are, respectively, lower than  $1^{\circ}/0.24$  dB over a bandwidth of 23.8–30.4 GHz, according to which the VMPS's bandwidth is defined. The minimum RMS phase error is  $0.32^{\circ}$  at ~27 GHz. The measured S-parameters of the corresponding 585 phase states are also shown in Fig. 7 (f). The measured peak gain of the VMPS is -4.9 dB at 28 GHz, while the simulated gains of the VMPS core and the output buffer are -2.3 and -1.5 dB, respectively. In addition, the measured input P1dB of the VMPS is 1 dBm at 28 GHz. Compared with the prior art in Table I, our work demonstrates the best phase resolution and lowest RMS phase error.

### V. CONCLUSION

It is proved that the phase-shift error of a conventional VMPS is higher in the vicinity of  $0^{\circ}$  and  $90^{\circ}$  rotation angles. To tackle

this issue, a VMPS structure with a two-stage current-reused VGA is introduced. With a negligible increase in the number of gm and current-steering cells, the proposed VGA offers  $2\times$  better resolution at low-gain states, thus improving the VMPS phase resolution considerably without compromising the gain and power consumption. Moreover, the proposed VMPS maintains its phase-shift accuracy even up to 9-dB gain back-off. Fabricated in 40-nm CMOS, the prototype demonstrates an RMS phase/gain error of 1°/0.24 dB over a bandwidth of 23.8–30.4 GHz while the core consumes 11 mW.

### REFERENCES

- S. Mondal, R. Singh, A. I. Hussein, and J. Paramesh, "A 25–30 GHz fully-connected hybrid beamforming receiver for MIMO communication," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1257–1287, May 2018.

- [2] G. H. Park, C. W. Byeon, and C. S. Park, "A 60-GHz low-power active phase shifter with impedance-invariant vector modulation in 65nm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 12, pp. 5395–5407, Dec. 2020.

- [3] S. Y. Kim *et al.*, "An improved wideband all-pass I/Q network for millimeter-wave phase shifters," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 11, pp. 3431–3439, Nov. 2012.

- [4] M. Mortazavi, Y. Shen, D. Mul, L. C. N. de Vreede, M. Spirito, and M. Babaie, "A four-way series doherty digital polar transmitter at mm-Wave frequencies," *IEEE J. Solid-State Circuits*, vol. 57, no. 3, pp. 803– 817, Mar. 2022.

- [5] O. Bakr and M. Johnson, "Impact of phase and amplitude errors on array performance," EECS Dept, Univ. California, Berkeley, CA, USA, Rep. UCB/EECS-2009-1, Jan. 2009.

- [6] J. Xia and S. Boumaiza, "Digitally assisted 28 GHz active phase shifter with 0.1 dB/0.5° RMS magnitude/phase errors and enhanced linearity," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 6, pp. 914–918, Jun. 2019.

- [7] E.-T. Sung, C. So, and S. Hong, "A 60-GHz variable-gain phase shifter with particular-sized digital-RF cells," *IEEE Trans. Microw. Theory Techn.*, vol. 70, no. 2, pp. 1302–1313, Feb. 2022.

- [8] N. Wei et al., "A calibration scheme for 24–28-GHz variable-gain phase shifter in 65-nm CMOS," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 4, pp. 1996–2000, Apr. 2022.