### A Dynamically Reconfigurable Recursive Switched-Capacitor DC-DC Converter with Adaptive Load Ability Enhancement

Lu, Qi; Li, Shuangmu; Zhao, Bo; Jiang, Junmin; Chen, Zhiyuan; Du, Sijun

DOI

10.1109/TPEL.2023.3235305

**Publication date**

**Document Version** Final published version

Published in

**IEEE Transactions on Power Electronics**

Citation (APA)

Lu, Q., Li, S., Zhao, B., Jiang, J., Chen, Z., & Du, S. (2023). A Dynamically Reconfigurable Recursive Switched-Capacitor DC-DC Converter with Adaptive Load Ability Enhancement. *IEEE Transactions on Power Electronics*, *38*(4), 5032-5040. https://doi.org/10.1109/TPEL.2023.3235305

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## A Dynamically Reconfigurable Recursive Switched-Capacitor DC–DC Converter With Adaptive Load Ability Enhancement

Qi Lu, Shuangmu Li, Bo Zhao, *Senior Member, IEEE*, Junmin Jiang , *Member, IEEE*, Zhiyuan Chen, *Member, IEEE*, and Sijun Du, *Senior Member, IEEE*

Abstract-Multiple voltage conversion ratio (VCR) recursive switched-capacitor (SC) dc-dc converters, based on several basic 2:1 converters, are widely used for on-chip power supplies due to their flexible VCRs for higher energy efficiency. However, conventional multiple VCR SC converters usually have one or more 2:1 converters unused for some VCRs, which results in lower power density and chip area wastage. This article presents a new recursive dc-dc converter system, which can dynamically reconfigure the connection of all on-chip 2:1 converter cells so that the unused converters in the conventional designs can be reused in this new architecture for increasing the load-driving capacity, power density, and power efficiency. To validate the design, a 4-bit-input 15-ratio system was designed and fabricated in a 180-nm BCD process, which can support a maximum load current of 0.71 mA and achieves a peak power efficiency of 93.1% with 105.3  $\mu$ A/mm<sup>2</sup> chip power density from a 2-V input power supply. The measurement results show that the load-driving capacity can become  $6.826 \times, 2.236 \times,$  and  $2.175 \times$  larger than the conventional topology when the VCR is 1/2, 1/4, and 3/4, respectively. In addition, the power efficiency under these specific VCRs can also be improved considerably.

*Index Terms*—DC-DC converters, fully integrated, multiple voltage conversion ratios (VCRs), recursive switched capacitor (RSC), switched-capacitor (SC).

### I. INTRODUCTION

NRECENT years, fully integrated power conversion systems have been favored by designers because of their smaller area and lower cost. Inductor, as a traditional energy storage device first caught the attention but soon the on-chip inductive power converter encountered some fatal problems. First,

Manuscript received 25 October 2022; revised 10 December 2022 and 21 December 2022; accepted 4 January 2023. Date of publication 9 January 2023; date of current version 14 February 2023. Recommended for publication by Associate Editor X. Ruan. (Corresponding author: Sijun Du.)

Qi Lu, Shuangmu Li, and Sijun Du are with the Department of Microelectronics, Delft University of Technology, 2628CD Delft, The Netherlands (e-mail: q.lu-7@student.tudelft.nl; s.li-53@student.tudelft.nl; sijun.du@tudelft.nl).

Bo Zhao is with the Institute of VLSI Design, Zhejiang University, Hangzhou 310058, China (e-mail: zhaobo@zju.edu.cn).

Junmin Jiang is with the Department of Electronic and Electrical Engineering, Southern University of Science and Technology, Shenzhen 518000, China (e-mail: jiangjm@sustech.edu.cn).

Zhiyuan Chen is with the State Key Laboratory of ASIC and System, Fudan University, Shanghai 201203, China (e-mail: chen\_zy@fudan.edu.cn).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2023.3235305.

Digital Object Identifier 10.1109/TPEL.2023.3235305

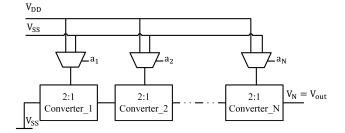

Fig. 1. Conventional recursive SC DC-DC converter [7].

on-chip inductive converters require high-Q inductor for good efficiency, necessitating special masks and increasing manufacturing costs [1]. Second, integrating the inductor will introduce the large inductor's parasitic resistance and parasitic capacitance between the inductor and the silicon substrate, and also the skin effect in the windings [2], [3], [4]. Third, since the inductor-based converter requires complex control systems when supplying low power loads, the load power scaling is challenging, which limits the power efficiency. Capacitor, as another energy storage element, has shown better performance and it has been proved that capacitor-based dc-dc converters can achieve better power conversion efficiencies than integrated inductive converters [5], [6]. Hence, switched-capacitor (SC) power converters have successfully emerged as the best candidate to become the next generation of fully integrated on-chip power converters.

However, the SC converters are only efficient at discrete ratios of input-to-output voltages, constricting efficient dynamic voltage scaling (DVS) to a small voltage range [8]. Using standard topologies to increase the voltage conversion ratio (VCR) numbers results in increased system complexity, power consumption, and extra switching elements [1]. Designing a circuit that can offer multiple VCRs has been proven to be a good solution (large DVS). In [9], a recursive switched-capacitor (RSC) dc–dc converter topology was proposed, which could realize high efficiency across a wide output voltage range by providing  $(2^N-1)$  conversion ratios using N 2:1 SC converter cells with minimal hardware overhead (VCR =  $A/2^N$ , A is the N-bit binary input VCR control signal and N is the cascaded stage number). Fig. 1 shows the principle diagram of the basic recursive SC converter. Based on this topology, Jung et al. [10] proposed a feedback

0885-8993 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

| Cascaded   | VCR    | Reconfigurable VCR Number |  |  |

|------------|--------|---------------------------|--|--|

| Number (N) | number |                           |  |  |

| 1          | 1      | 0                         |  |  |

| 2          | 3      | 1                         |  |  |

| 3          | 7      | 1                         |  |  |

| 4          | 15     | 3                         |  |  |

| •••        |        |                           |  |  |

| N. 7       | 0N 1   | oint(N/2) 1               |  |  |

TABLE I

RECONFIGURABLE VCR NUMBER OF DIFFERENT CASCADED STAGES

loop using two separate sets of N-bit input control signals A and B, generating VCR = A/(8+B). This design could have much more VCRs than the prior work. The aforementioned multi-VCR converter topologies can be employed in the modern System-on-Chips and Internet-of-Things devices to solve the battery degradation problem and then extend the battery lifetime.

Nevertheless, the 2:1 converter cells in an RSC-based dc-dc converter are typically not fully used under some specific VCRs; as a result, load-driving ability, power density, and power efficiency are limited. Considering the commonly used VCR = 1/2 condition as an example, only the Nth converter operates, whereas the remaining (N-1) converters are not in use. To address this problem, this article proposes a novel topology to make full use of every on-chip 2:1 converter in different VCRs. The connection of all on-chip 2:1 converters can be dynamically reconfigured, which means the unused converters in the conventional RSC designs can be reused and no converter cell is wasted. Compared with the conventional RSC converter, the equivalent output impedance of the proposed system can be improved significantly, resulting in a higher output power under some specific VCRs. The proposed converter has been designed and fabricated in a 180-nm BCD process. The measurement results show the dramatically increased load-driving capability and improved power conversion efficiency under certain VCRs.

The rest of this article is organized as follows. Section II gives the operation principle of the proposed system. Section III describes the detailed implementation of building blocks and highlights the theoretical analysis results. Then, the measurement results are presented in Section IV. Finally, Section V concludes this article.

### II. PROPOSED TOPOLOGY

### A. Operation Principle

This proposed topology aims to reconfigure the cascaded recursive converter topology into a paralleled converter circuit to make full use of every single-stage 2:1 converter. That means the more cascaded converter stages there are, the more VCR can be dynamically reconfigured. The relationship between the cascaded stage number and the reconfigurable VCR number is presented in Table I. For N cascaded stages, the reconfigurable VCR number could be generalized as follows:

$$RVN = 2^{\inf(N/2)} - 1.$$

(1)

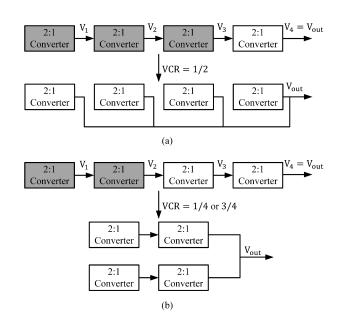

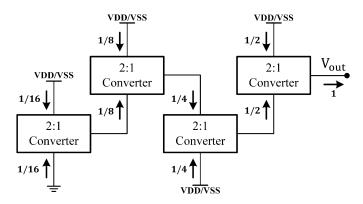

Fig. 2. Proposed dynamic reconfiguration scheme for (a) VCR = 1/2 and (b) VCR = 1/4 or 3/4.

Taking a four-stage cascaded recursive SC converter as an example, according to Table I, three VCRs can be dynamically reconfigured, which are VCR = 1/2, 1/4, and 3/4, respectively. In these three specific VCRs in conventional RSC converters, only the last stage (VCR = 1/2) or the last two stages (VCR = 1/2) 1/4 or 3/4) can be used, whereas the other converter cells are idle. Fig. 2 shows the reconfiguration process of the proposed system at these three VCRs, with the unused converter cells colored in gray. When VCR = 1/2, this proposed converter is able to reconfigure the four-stage-series-connected converter system into a four-stage-parallel-connected converter system so that the previously unused converters can be fully used and, therefore, the load-driving capacity could be enhanced by at least four times. Similarly, when VCR = 1/4 or 3/4, the topology also switches the series-connected system into a new parallel-connected system, and the load-driving capacity can be increased by at least two times. However, the real enhancement factor calculation is much more complicated because the unused converters affect the effective output impedance, although they are not outputting any power. Theoretically, if the unused converters are connected in parallel for VCR = 1/4, 1/2, and 3/4cases, the load-driving capacity should be enhanced by  $2.125 \times$ ,  $5.3125\times$ , and  $2.125\times$ , respectively. The detailed analysis is given in Section III-B.

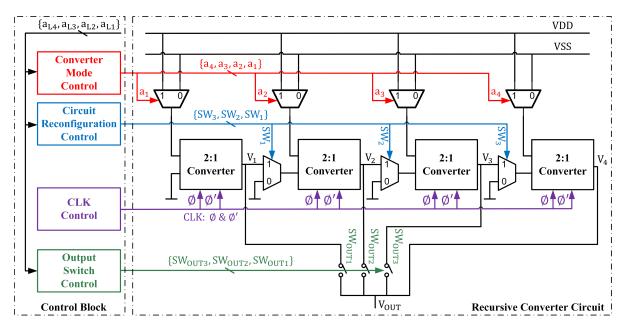

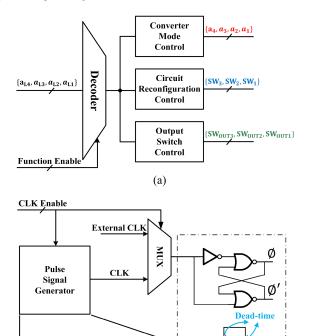

A 4-bit 15-VCR converter system consisting of four 2:1 converter cells is designed to validate the proposed design. The top-level system architecture is shown in Fig. 3. The proposed system contains five main blocks: a four-level series 2:1 converter system, a converter-mode control block (VCR reconfiguration), a circuit reconfiguration control block, an output switch control block, and a CLK control block. The VCR of the system is controlled by an external 4-bit binary global input signal  $\{a_{L4}, a_{L3}, a_{L2}, a_{L1}\}$ . In these cases, the circuit reconfiguration control block produces a MUX control signal  $\{SW_3, SW_2, SW_1\}$  to make the unused converter cells form new

<sup>\*</sup> int means round down.

Fig. 3. Proposed system architecture.

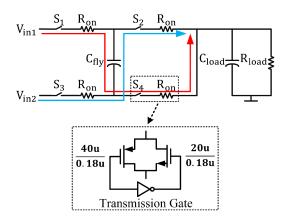

Fig. 4. 2:1 Converter cell.

submodules. Then, the converter-mode control block generates a new VCR control signal  $\{a_4, a_3, a_2, a_1\}$  to control the conversion ratio of the new submodules. These processes could guarantee that all submodules have the same desired VCRs so that they can be reconfigured in parallel. The outputs of all 2:1 converters are connected to the total output  $V_{\rm out}$  through a 3-bit controllable selecting signal  $\{SW_{\rm out3}, SW_{\rm out2}, SW_{\rm out1}\}$  to increase the total output current at specific VCRs, thus improving the system's load-driving capacity.

### III. CIRCUIT IMPLEMENTATION AND ANALYSIS

### A. 2:1 SC Converter

1) Concept of the 2:1 SC Converter: In this section, the 2:1 SC converter unit is depicted in Fig. 4, which consists of a flying capacitor  $C_{\rm fly}$  and four power switches with ON-state resistance  $R_{\rm on}$ . The output consists of a decoupling capacitor  $C_{\rm load}$  in parallel with the load resistor  $R_{\rm load}$  [11]. Typically, the SC dc–dc converter operates in two phases under a pair of nonoverlapping

Fig. 5. Charge distribution of the conventional recursive SC [7].

gate control signals with a 50% duty cycle (could be slightly less than 50%, but the duty cycle of two phases should remain the same); the flying capacitor is switched between the charging phase 1 and the discharging phase 2 [12].

During the charging phase 1 shown as the red line in Fig. 4, the flying capacitor is in series between the input  $V_{\rm in1}$  and the output  $V_{\rm out}$  (switches S1 and S4 are ON). The charge from the input goes through  $C_{\rm fly}$  that charges this capacitor up to  $V_C = (V_{\rm in1} - V_{\rm out})$  and flows to the output [11].

During the discharging phase 2 shown as the blue line in Fig. 4, the flying capacitor is in parallel between another input  $V_{\rm in2}$  and the output  $V_{\rm out}$  (switches S2 and S3 are ON). The charge stored on  $C_{\rm fly}$  in the previous phase is now transferred to the output. The  $V_{\rm out}$  becomes the sum of the input and the capacitor voltage  $(V_{\rm in2}+V_C)$ . Then, the overall output voltage can be determined as follows:

$$V_{\text{out}} = \frac{1}{2}(V_{\text{in}1} + V_{\text{in}2}). \tag{2}$$

Since the two inputs of the converter cell do not maintain the polarity during operations in this topology, transmission

|                    |                                |                      | 1tour C         | I TOTAL STSTEW                                                                                                        |                                    |

|--------------------|--------------------------------|----------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------|

|                    | VCR                            | $R_{SSL}$            | $R_{FSL}$       | $R_{out} = \sqrt{R_{SSL}^2 + R_{FSL}^2}$                                                                              | Enhancement factor $$M_{Enhance}$$ |

| Original Recursive | $\frac{1\sim15}{16}$           | $\frac{85}{256f_sC}$ | $2.65625R_{on}$ | $\sqrt{\left(\frac{85}{256f_sC}\right)^2 + \left(2.65625R_{on}\right)^2}$                                             | none                               |

|                    | $\frac{1}{2}$                  | $\frac{16}{256f_sC}$ | $0.5R_{on}$     | $\sqrt{\left(\frac{1}{5.3125}\right)^2\left(\left(\frac{85}{256f_sC}\right)^2 + \left(2.65625R_{on}\right)^2\right)}$ | 5.3125                             |

| Proposed Design    | $\frac{1}{4}$ or $\frac{3}{4}$ | $\frac{40}{256f_sC}$ | $1.25R_{on}$    | $\sqrt{(\frac{1}{2.125})^2((\frac{85}{256f_sC})^2 + (2.65625R_{on})^2)}$                                              | 2.125                              |

|                    | others                         | $\frac{85}{256f_sC}$ | $2.65625R_{on}$ | $\sqrt{\left(\frac{85}{256f_sC}\right)^2 + (2.65625R_{on})^2}$                                                        | 1                                  |

| VDD<br>T           |                                | VDD                  |                 | VDD VI                                                                                                                | DD/VSS                             |

| 1/8                |                                | 1/8 ↓                |                 | 1/8 1/4                                                                                                               | $\downarrow$                       |

| 2:1                | 1/4                            | 2:1                  | ,               | 2:1                                                                                                                   | 2:1                                |

| Converter          | 1                              | Conver               | ter             | Converter   Co                                                                                                        | nverter                            |

### $\begin{array}{c} {\rm TABLE~II} \\ R_{\rm OUT}~{\rm OF~TOTAL~SYSTEM} \end{array}$

Fig. 6. Charge distribution of this reconfigurable recursive SC at (a) VCR = 1/2 and (b) VCR = 1/4 or 3/4.

gates with NMOS and PMOS switches, as shown in Fig. 4, are employed in this design to handle the different voltage polarities across the switches.

2) Analysis of Output Impedance: With the switching frequency  $f_s$  changes, the 2:1 converter will work in two asymptotic operating regions: the fast switching limit (FSL) and the slow switching limit (SSL) [13], [14]. By evaluating the power loss of these two operating regions when providing  $I_{\text{load}} \neq 0$ , the equivalent output impedance  $R_{\text{out}}$  can be found.

Assuming that the charge flows to the output in phase 1 and phase 2 is the same, equal to  $0.5q_{\rm out}$ , the charge flowing through the flying capacitor  $C_{\rm fly}$  and the load capacitor  $C_{\rm load}$  is  $q_C$  and  $q_L$ , respectively. In the charging phase, the input  $V_{\rm in1}$  charges these two capacitors and also contributes some charge to the output  $q_{\rm in}=q_C=0.5q_{\rm out}+q_L$ . Note that, in steady state, the charge flowing through each of the capacitors must be of equal magnitude but opposite in both clock phases. That means in discharging phase, both of these two capacitors in this topology  $C_{\rm fly}$  and  $C_{\rm load}$  will contribute charge to the output as  $0.5q_{\rm out}=q_C+q_L$ . Finally, the charge stored and released in the flying capacitor can be easily obtained as follows:

$$q_C = \frac{1}{2}q_{\text{out}}. (3)$$

When analyzing the output impedance, here, the FSL would be considered first. That means the system is working in a very high switching frequency  $f_s$ , which will make the phase time much smaller than the time constant  $\tau$  of this topology. In this mode, the flying capacitors only have a little time to be charged and discharged that means the capacitor's voltage can be modeled as constant and so does the current. The circuit power loss is related only to the conduction loss  $P_{R_{\rm SW}}$  when the charge flows through the ON-state resistance of the power switches [13]. By normalizing the conduction loss  $\left(\sum_{i=1}^4 2R_iq_C^2f_s\right)$  by the squared output current  $I_{\rm out}^2$ , i.e.,  $(q_{\rm out}f_s)^2$ , the equivalent output impedance  $R_{\rm FSL}$  could be given as (4). It is obvious that it is independent of switching frequency  $f_s$  and flying capacitance  $C_{\rm fly}$

$$R_{\rm ESL} = 2R_{\rm on}.\tag{4}$$

The SSL is just the opposite situation of the FSL. In this mode, the phase time is much larger than the time constant  $\tau$  so that the capacitor could have enough time to be fully charged and discharged. In steady state, the current flowing through the capacitor becomes zero, so the energy loss when charging and discharging a capacitor is not related to the ON-state resistance of the power switch  $R_{\rm on}$  anymore [13]. The total energy loss

Fig. 7. Output voltage waveform.

Fig. 8. Control block diagram. (a) Digital logic control signal generation block. (b) Gate-drive signal generation block.

(b)

Nonoverlapping CLK

CLK GENERATOR

through the converter can be found by adding the charge-sharing loss across each flying capacitor.

The practical flying capacitor used in circuits is not an ideal component with only capacitance. However, they can be treated to a very good approximation as being an ideal capacitor in series with a resistance and this resistance is defined as the equivalent series resistance  $R_{\rm ESR}$  [15]. The charge-sharing loss  $P_{C_{\rm fly}}$  happens due to the conduction loss of the equivalent series

TABLE III DIGITAL CONTROL BLOCK LOGIC

| Voltage    | Global | Converter | Circuit         | Output |

|------------|--------|-----------|-----------------|--------|

| Conversion | Input  | Mode      | Reconfiguration | Switch |

| Ratio(VCR) | Signal | Signal    | Signal          | Signal |

| 1/16       | 0001   | 0001      | 111             | 000    |

| 1/8        | 0010   | 0010      | 111             | 000    |

| 3/16       | 0011   | 0011      | 111             | 000    |

| 1/4        | 0100   | 0101      | 101             | 010    |

| 5/16       | 0101   | 0101      | 111             | 000    |

| 3/8        | 0110   | 0110      | 111             | 000    |

| 7/16       | 0111   | 0111      | 111             | 000    |

| 1/2        | 1000   | 1111      | 000             | 111    |

| 9/16       | 1001   | 1111      | 000             | 111    |

| 5/8        | 1010   | 1111      | 000             | 111    |

| 11/16      | 1011   | 1111      | 000             | 111    |

| 3/4        | 1100   | 1111      | 101             | 010    |

| 13/16      | 1101   | 1111      | 000             | 111    |

| 7/8        | 1110   | 1111      | 000             | 111    |

| 15/16      | 1111   | 1111      | 000             | 111    |

|            |        |           |                 |        |

resistance  $R_{\rm ESR}$  during converter operation [16], [17]. For the 2:1 converter topology, the charge-sharing loss can be simplified as  $q_C^2/C_{\rm fly}$ . By also normalizing this loss by the squared output current  $I_{\rm out}^2$ , the equivalent output impedance in SSL mode could be defined as follows:

$$R_{\rm SSL} = \frac{1}{4f_s C_{\rm fly}}. (5)$$

### B. Total System Analysis

The conventional recursive SC converter is based on a multistage 2:1 converter cascaded. Each flying capacitor,  $C_i$ , in the 2:1 converter cell has at least one input node connected to  $V_{DD}$  or  $V_{SS}$ . So, each converter has to load half of its output charge  $q_C=0.5q_{\rm out}$  on the input from the previous converter cell and the power supply  $V_{DD}$  or  $V_{SS}$ . For an N-stage cascaded recursive converter, each converter stage is loaded with an output charge  $q_{\rm out,}i$  that is divided by a binary weight of the total output charge  $q_{\rm out}$ , which is  $q_{\rm out,}i=q_{\rm out}/\left(2^{N-i}\right)$ [9]. By using the same analysis method from Section III.A-2, the SSL mode  $R_{\rm SSL}$  and the FSL mode  $R_{\rm FSL}$  of an N stage RSC system could be summarized as (6) and (7), respectively

$$R_{\text{SSL}} = \sum_{i=1}^{N} \sum_{j=1}^{4} \left(\frac{1}{2^{N-i+1}}\right)^2 \frac{1}{f_s C_i} \tag{6}$$

$$R_{\text{FSL}} = \sum_{i=1}^{N} \sum_{j=1}^{4} \frac{1}{2} \left( \frac{1}{2^{N-i}} \right)^{2} R_{i,j}. \tag{7}$$

It is worth noting that for the conventional RSC converter system, as long as the number of recursion depth N is determined, the charge distribution of each stage can be fixed as Fig. 5. That means, no matter how the VCR changes, the equivalent output impedance would theoretically remain the same, which is presented in Table II.

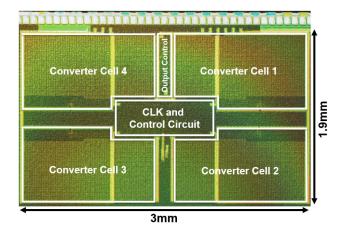

Fig. 9. Chip micrograph.

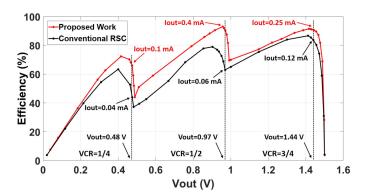

Fig. 10. Efficiency versus  $V_{\text{out}}$ .

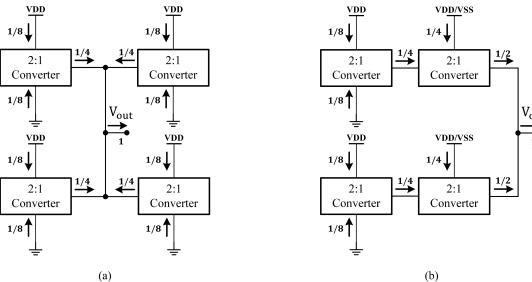

While for the proposed design in this article, the originally fixed charge distribution is now changed by reconfiguring the circuit structure under some specific VCRs. Fig. 6 shows the new charge distribution at VCR = 1/2 (left) and VCR = 1/4 or 3/4 (right) when recursion depth N=4. Through the identical equivalent impedance analysis method, the  $R_{\rm SSL}$  and  $R_{\rm FSL}$  of the reconfigured circuit can be calculated, as shown in Table II, where  $M_{\rm Enhance}$  is the enhancement factor, which refers to the ratio of the equivalent output resistance between the conventional RSC system and this reconfigurable one.  $M_{\rm Enhance}$  directly reflects the enhancement of the load-driving capacity under these three VCRs. Theoretically, for VCR = 1/2, the load-driving capacity is improved to  $5.3125\times$ , whereas for VCR = 1/4 or 3/4, a  $2.125\times$  increment is realized.

### C. Control Block

1) Logic Control Block: The logic control blocks include the converter-mode control, the circuit reconfiguration control, and the output switch control blocks, as shown in Fig. 3. The output control signals of these three blocks are generated from the 4-bit global input signal  $\{a_{L4}, a_{L3}, a_{L2}, a_{L1}\}$ . This 4-bit global input gives the desired VCR for the proposed system. The three logic control blocks translate this 4-bit VCR signal into different configuration signals to determine the actual VCR for each 2:1 converter cell, the parallel-series circuit connections,

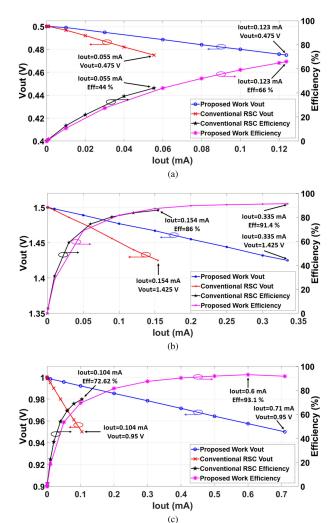

Fig. 11.  $V_{\text{out}}$  and efficiency versus load current.

TABLE IV MEASUREMENT OF OVERALL OUTPUT IMPEDANCE  $R_{

m OUT}$

|           | VCR | Conventional | Proposed       | Theoretical | Measured |

|-----------|-----|--------------|----------------|-------------|----------|

|           | VCR | RSC          | RSC            | Factor      | Factor   |

|           | 2:1 | 485Ω         | 71.05Ω         | 5.3125      | 6.826    |

| $R_{out}$ | 4:1 | 451Ω         | $201.7\Omega$  | 2.125       | 2.236    |

|           | 4:3 | 486Ω         | $223.45\Omega$ | 2.125       | 2.175    |

and which converter cells are connected to the global output  $V_{\mathrm{out}}$ , respectively.

Table III presents the signal translation of each logic control block for different VCRs. In this 15-VCR four-stage converter architecture, this proposed system can be dynamically reconfigured under three specific VCRs in bold to achieve higher load-driving ability.

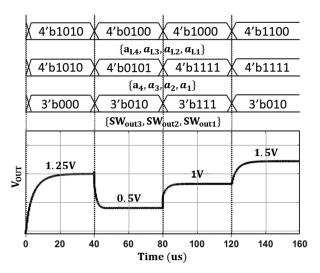

The simulated waveform of the global 4-bit input signals, some key control signals, and the output voltage are shown in Fig. 7. At the first period, the global input signal is  $\{a_{L4}, a_{L3}, a_{L2}, a_{L1}\} = 4'b1010$  (VCR = 10/16,  $V_{\rm out} = 1.25$  V), the output switching signal is  $\{{\rm SW}_{\rm out3}, {\rm SW}_{\rm out2}, {\rm SW}_{\rm out1}\} = 3'b000$ , and only the fourth 2:1 converter is connected to the global output and all the converter

| Design                                       | This Work                | 2019 [18]             | 2018 [19]      | 2016 [10]      | 2015 [20]                      | 2014 [9]       | 2013 [21]                    |

|----------------------------------------------|--------------------------|-----------------------|----------------|----------------|--------------------------------|----------------|------------------------------|

| Technology                                   | 180 nm                   | 250 nm                | 130 nm         | 180 nm         | 250 nm                         | 250 nm         | 180 nm                       |

| Topology                                     | Reconfigurable Recursive | Asymmetrical<br>Shunt | Fixed          | Rational       | Gear Train+<br>Charge Feedback | Recursive      | Successive-<br>approximation |

| Number of Ratios                             | 15                       | 187                   | 3              | 79             | 24                             | 15             | 117                          |

| Circuit Dynamical<br>Configuration           | Yes                      | No                    | No             | No             | No                             | No             | No                           |

| Maximum Converter<br>Reuse Times             | 4                        | 1                     | 1              | 1              | 1                              | 1              | 1                            |

| Input Voltage                                | 2 V                      | 3.3 V                 | 1.2 - 2.3 V    | 2 V            | 2.5 - 5 V                      | 2.5 V          | 3.4 - 4.3 V                  |

| Output Voltage                               | 0.12 - 1.8 V             | 0.4 - 2.8V            | 0.9 V          | 0.13 - 1.87 V  | 0.2 - 2 V                      | 0.1 - 2.18 V   | 0.9 - 1.5 V                  |

| Max. Load Current                            | 0.71 mA                  | 10 mA                 | 0.49 mA        | N/A            | 60 mA                          | 2 mA           | 0.3 mA                       |

| Capacitor Type                               | MIM<br>On-Chip           | MIM<br>On-Chip        | MOS<br>On-Chip | MIM<br>On-Chip | SMD<br>Off-Chip                | MIM<br>On-Chip | MIM+MOS<br>On-Chip           |

| Peak Efficiency $(\eta_{peak})$              | 93.1%                    | 87%                   | 80.4%          | 95%            | 95.5%                          | 85%            | 72%                          |

| Power Density @ $\eta_{peak}$ $(\mu A/mm^2)$ | 105.3                    | 1120.4                | 3550           | 71.4           | 2881.8<br>(Off-chip caps)      | 430.6          | 5.9                          |

| Chip Area (mm <sup>2</sup> )                 | 5.7                      | 7.14                  | 0.138          | 3.36           | 3.47                           | 4.645          | 1.69                         |

TABLE V STATE-OF-THE-ART COMPARISON

cells are connected in series. Then, the global input signal  $\{a_{L4}, a_{L3}, a_{L2}, a_{L1}\}$  turns to 4'b0100 (VCR = 1/4,  $V_{\text{out}}$  = 0.5 V),  $\{\text{SW}_{\text{out3}}, \text{SW}_{\text{out2}}, \text{SW}_{\text{out1}}\}$  switches into 3'b010, indicating that the system is split into two submodules (each submodule has a two-cascaded converter) and the output of the second and fourth converter cells  $V_2$  and  $V_4$  is connected to the global output. Finally, the converter-mode control signal  $\{a_4, a_3, a_2, a_1\}$  becomes 4'b0101 to make sure that the two new submodules could realize VCR = 1/4. Therefore, the load-driving capacity could be enhanced by  $2.125\times$  theoretically. The system should now operate as the reconfiguration, as shown in Fig. 2(b).

Then,  $\{a_{L4}, a_{L3}, a_{L2}, a_{L1}\}$  becomes 4'b1000 (VCR = 1/2,  $V_{\text{out}} = 1 \text{ V}$ ). The converter-mode control block creates a new input control signal  $\{a_4, a_3, a_2, a_1\} = 4'b1111$  so that each converter achieves the VCR = 1/2. And  $\{\text{SW}_{\text{out3}}, \text{SW}_{\text{out2}}, \text{SW}_{\text{out1}}\}$  changes into 3'b111, which means all reconfiguration switches are used now. As a result, the proposed design makes full use of each 2:1 converter to increase the load-driving capacity by  $5.3125 \times$ . This is the case shown in Fig. 2(a).

2) CLK Control Block: Fig. 8 bottom part presents the CLK control block that includes a pulse signal generator, CLK selector, and a nonoverlapping CLK generator. The pulse signal generator contains a ring oscillator and a D flip-flop. After the ring oscillator generates a sine wave with a suitable frequency  $f_s$ , the D flip-flop is used to shape it into a square wave with a duty cycle of 50%. Also, the D flip-flop only consumes very little energy, which is good for energy efficiency. In addition to the internal CLK from by pulse generator, this block also has an external CLK. These two CLKs can be selected by a 1-bit CLK Enable signal at the MUX. In the nonoverlapping CLK generation circuit, the selected CLK is translated into a pair of interleaved signals  $\phi$  and  $\phi'$  with sufficient deadtime to control the operation of the entire system. This can avoid the simultaneous conduction of power transistors during switching transitions so that the short-circuit power loss in converters can be eliminated.

### IV. MEASUREMENT RESULTS

Fig. 9 shows the chip micrograph. The proposed system has been fabricated in a 180-nm BCD process, occupying  $5.7~\mathrm{mm}^2$  active chip area  $(1.9~\mathrm{mm}\times3~\mathrm{mm})$ . The proposed system has been made fully on-chip integrated, and on-chip metal-insulatormetal (MIM) capacitors are used for flying capacitors, which are  $4~\mathrm{nF}$  in total (1 nF in each 2:1 converter cell). Finally, all measurements were tested under a clock frequency of 1 MHz and the overall input was a dc voltage of 2 V.

Fig. 10 illustrates the power transfer efficiency versus the output voltage change. Since the figures for the proposed design and conventional design are the same for the VCRs not needing reconfiguration, this figure only focuses on the reconfigurable VCRs, which are 1/4, 1/2, and 3/4. It can be seen from the curve that when the output voltage is the same, the load current of this work is much larger than that of the conventional RSC because the idle converter cells are fully used through reconfiguration. Besides, for these three VCRs, the power conversion efficiency of the proposed design has been comprehensively improved over the entire output voltage range. This is because the input and output power has been significantly improved while the energy loss of the entire system remains unchanged; as a result, the impact of nonideal energy loss on efficiency becomes smaller in this case.

The figures of the power transfer efficiency and the output voltage versus the change of the load current under VCR = 1/4, 1/2, and 3/4 are plotted in Fig. 11. Here, we define that the valid output should be larger than 95% of the desired output voltage. In Fig. 11(a), VCR = 1/4, when the efficiency reaches peak value and the output voltage is drawn down to near 95% of preferred output voltage (0.5 V), the load current of the proposed and conventional RSC converters are  $123~\mu\text{A}$  and  $55~\mu\text{A}$ , respectively. It can be seen that the load-driving capacity becomes almost  $2.236 \times \text{larger}$  with the proposed design in this case. The VCR = 3/4 has a similar condition to the previous VCR, which is shown

in Fig. 11(b), but the measured load-driving enhancement is  $2.175\times$ . Fig. 11(c) gives the results when VCR = 1/2. When the efficiency achieves the peak value, the proposed work can attain 93.1% efficiency under  $I_{\rm out}=600\,\mu{\rm A}$  and the conventional RSC can only have 72.62% efficiency under  $I_{\rm out}=104\,\mu{\rm A}$ . In addition, when output voltage deteriorates to 950 mV (95% of preferred output voltage, 1 V), the load current of the proposed work is  $710\,\mu{\rm A}$ , which is larger than  $104\,\mu{\rm A}$  when using the conventional RSC. It can be seen that the load-driving capacity under VCR = 1/2 is improved by around  $6.826\times$ , thanks to the four converter cells reconfigured to be connected in parallel.

The load-driving capacity can be reflected by the equivalent output impedance  $R_{\text{out}}$  of the entire circuit. Based on the measurement results of  $V_{\text{out}}$  versus  $I_{\text{out}}$  in the previous paragraph, the equivalent output impedance under these three VCRs can be calculated and shown in Table IV. The factor, referring to the ratio of the equivalent output impedance between the conventional and proposed RSC converter, indicates the enhancement of the load-driving capacity. It can be found that for VCR = 1/4 and 3/4, the measured factors 2.236 and 2.175 are slightly larger than the theoretical factor 2.125, but they are still close. While for VCR = 1/2, the measured factor 6.826 is much larger than 5.3125. The reasons for these variations are explained as follows: First, in the total equivalent output impedance analysis, the ON-resistance of all switches used for the reconfiguration function must also be taken into account and will dramatically influence the overall impedance. In addition, in the layout design, the wire resistance and the parasitic capacitor introduced between different metal layers will also have a great impact on the final equivalent output

Table V gives the comparison of key performance between this work and conventional designs. One improvement of the proposed design is the dynamically reconfigurable connection of all 2:1 converter cells according to the desired VCR. The conventional RSC designs were fixed topology using four 2:1 converter cells in series, which results in lower load-driving capacity and unused on-chip area. In addition, the proposed design has a peak efficiency of 93.1%, which is among the highest in all fully on-chip integration designs. Only Jung et al. [10] realized a higher peak efficiency, but the output power at peak efficiency of the proposed design achieves almost four times larger than that design, thanks to the circuit reconfiguration function.

### V. CONCLUSION

This article proposes a dynamically reconfigurable RSC dcdc converter with adaptive load ability enhancement. The presented topology can make full use of each 2:1 converter of a multi-VCR system by dynamically reconfiguring the connection of all the 2:1 converter cells. The reconfigurable VCR number can be determined as  $(2^{\text{int}(N/2)}-1)$  for N cascaded recursive converter system. Through this method, the load-driving capacity under specific VCRs can be significantly enhanced; in addition, the power transfer efficiency can also be further improved.

A fully integrated dynamically reconfigurable four-stage recursive SC converter was designed and fabricated in a 180-nm

BCD process to experimentally validate the enhancement of the load-driving ability and power efficiency. The measurement results show that the maximum load-driving current is around 0.71 mA and the power density of this converter system under a peak efficiency of 93.1% is  $105.3\,\mu\text{A/mm}^2$ . In addition, the proposed circuit has an energy efficiency greater than 80% over a wide output range. Most importantly, the load-driving capacity under some VCRs is significantly increased by up to  $6.826\times$  compared with the conventional RSC topology.

#### ACKNOWLEDGMENT

The authors would like to thank EUROPRACTICE for MPW and design tool support.

### REFERENCES

- [1] S. Bang, D. Blaauw, and D. Sylvester, "A successive-approximation switched-capacitor dc-dc converter with resolution of v<sub>in</sub>/2<sup>N</sup> for a wide range of input and output voltages," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 543–556, Feb. 2016.

- [2] J. Wibben and R. Harjani, "A high efficiency dc-dc converter using 2nh on-chip inductors," in *Proc. IEEE Symp. VLSI Circuits*, 2007, pp. 22–23.

- [3] M. Wens and M. Steyaert, "A fully-integrated 130nm CMOS DC-DC step-down converter, regulated by a constant on/off-time control system," in *Proc. IEEE Eur. Solid-State Circuits Conf.*, 2008, pp. 62–65.

- [4] T. M. van Breussegem and M. S. J. Steyaert, "Monolithic capacitive DC-DC converter with single boundary–multiphase control and voltage domain stacking in 90 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1715–1727, Jul. 2011.

- [5] T. van Breussegem and M. Steyaert, "A 82% efficiency 0.5% ripple 16-phase fully integrated capacitive voltage doubler," in *Proc. Symp. VLSI Circuits*, 2009, pp. 198–199.

- [6] H.-P. Le, M. Seeman, S. R. Sanders, V. Sathe, S. Naffziger, and E. Alon, "A 32nm fully integrated reconfigurable switched-capacitor DC-DC converter delivering 0.55 W/mm<sup>2</sup> at 81% efficiency," in *Proc. IEEE Int. Solid-State Circuits Conf.*, 2010, pp. 210–211.

- Y.-T. Lin et al., "Unsymmetrical parallel switched-capacitor (UP-SC) regulator with fast searching optimum ratio technique," in *Proc. IEEE 43rd Eur. Solid State Circuits Conf.*, 2017, pp. 287–290.

Y. Lei and R. C. N. Pilawa-Podgurski, "A general method for ana-

- [8] Y. Lei and R. C. N. Pilawa-Podgurski, "A general method for analyzing resonant and soft-charging operation of switched-capacitor converters," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5650–5664, Oct. 2015.

- [9] L. G. Salem and P. P. Mercier, "A recursive switched-capacitor DC-DC converter achieving 2<sup>N</sup> 1 ratios with high efficiency over a wide output voltage range," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2773–2787, Dec. 2014.

- [10] W. Jung, D. Sylvester, and D. Blaauw, "12.1 A rational-conversion-ratio switched-capacitor DC-DC converter using negative-output feedback," in *Proc. IEEE Int. Solid-State Circuits Conf.*, 2016, pp. 218–219.

- [11] T. M. Andersen et al., "A 4.6 W/mm<sup>2</sup> power density 86% efficiency onchip switched capacitor DC-DC converter in 32 nm SOI CMOS," in *Proc. IEEE 28th Annu. Appl. Power Electron. Conf. Expo.*, 2013, pp. 692–699.

- [12] H.-P. Le, S. R. Sanders, and E. Alon, "Design techniques for fully integrated switched-capacitor DC-DC converters," *IEEE J. Solid-State Circuits*, vol. 46, no. 9, pp. 2120–2131, Sep. 2011.

- [13] M. D. Seeman and S. R. Sanders, "Analysis and optimization of switched-capacitor DC–DC converters," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 841–851, Mar. 2008.

- [14] S. R. Sanders, E. Alon, H.-P. Le, M. D. Seeman, M. John, and V. W. Ng, "The road to fully integrated DC–DC conversion via the switched-capacitor approach," *IEEE Trans. Power Electron.*, vol. 28, no. 9, pp. 4146–4155, Sep. 2013.

- [15] J. W. Kimball, P. T. Krein, and K. R. Cahill, "Modeling of capacitor impedance in switching converters," *IEEE Power Electron. Lett.*, vol. 3, no. 4, pp. 136–140, Dec. 2005.

- [16] W.-H. Ki, F. Su, and C.-Y. Tsui, "Charge redistribution loss consideration in optimal charge pump design," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2005, vol. 2, pp. 1895–1898.

- [17] A. M. Mohey, S. A. Ibrahim, I. M. Hafez, and H. Kim, "Design optimization for low-power reconfigurable switched-capacitor DC-DC voltage converter," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 10, pp. 4079–4092, Oct. 2019.

- [18] Y.-T. Lin et al., "A fully integrated asymmetrical shunt switched-capacitor dc-dc converter with fast optimum ratio searching scheme for load transient enhancement," *IEEE Trans. Power Electron.*, vol. 34, no. 9, pp. 9146–9157, Sep. 2019.

- [19] R. Madeira, J. P. Oliveira, and N. Paulino, "A 130 nm CMOS power management unit with a multi-ratio core SC DC–DC converter for a supercapacitor power supply," *IEEE Trans. Circuits Syst. II, Express Briefs*, vol. 65, no. 10, pp. 1445–1449, Oct. 2018.

- [20] L. G. Salem and P. P. Mercier, "A battery-connected 24-ratio switched capacitor PMIC achieving 95.5%-efficiency," in *Proc. Symp. VLSI Circuits*, 2015, pp. C340–C341.

- [21] S. Bang, A. Wang, B. Giridhar, D. Blaauw, and D. Sylvester, "A fully integrated successive-approximation switched-capacitor DC-DC converter with 31mV output voltage resolution," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2013, pp. 370–371.

**Qi Lu** received the B.Sc. degree in microelectronic science and engineering from the University of Electronic Science and Technology of China, Chengdu, China, in 2020, and the M.Sc. degree in microelectronics from the Delft University of Technology (TU Delft), Delft, The Netherlands, in 2022.

His research interests include fully integrated power management, energy-efficient dc-dc conversion and near-field communication system.

Shuangmu Li received the B.Sc. degree in electronic information engineering from Zhejiang University, Hangzhou, China, in 2019, and the first M.Sc. degree in microelectronic system design from The University of Southampton, Southampton, U.K., in 2020. He is currently working toward the second M.Sc. degree in microelectronics with TU Delft, Delft, The Netherlands.

From 2020 to 2021, he was an Analog Integrated Circuit Design Engineer in Hangzhou, China. His current research interests include integrated dc-dc converters.

**Bo Zhao** (Senior Member, IEEE) received the Ph.D. degree from the Department of Electronic Engineering, Tsinghua University, Beijing, China, in 2011.

He was a Research Fellow with the National University of Singapore, Singapore, from 2013 to 2015. From 2015 to 2018, he was an Assistant Project Scientist with Berkeley Wireless Research Center, Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA, USA. Since 2018, he has been a Professor with the Institute of VLSI Design, Zhejiang University,

Hangzhou, China. He has authored or coauthored more than 60 articles and book chapters, and he holds more than 30 Chinese patents. His research interests include IoT radios, wireless power transfer, and wearable/implantable radios.

Dr. Zhao was a recipient of the 2017 IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS Darlington Best Paper Award and the Design Contest Award of the 2013 IEEE International Symposium on Low Power Electronics and Design. He serves as an Associate Editor for IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS and IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: REGULAR PAPERS. He also serves as a Committee Member of IEEE/C/SM. He was the Publication Chair of the 2016 IEEE Biomedical Circuits and Systems Conference. In 2022, he was elected to be the Chair Elect of Biomedical and Life Science Circuits and Systems Society.

Junmin Jiang (Member, IEEE) received the B.Eng. degree in electronic and information engineering from Zhejiang University, Hangzhou, China, in 2011, and the Ph.D. degree in electronic and computer engineering from The Hong Kong University of Science and Technology (HKUST), Hong Kong, in 2017.

He was a Visiting Scholar with the State Key Laboratory of AMSV, University of Macau, Macau, China, in 2015, and was a Postdoctoral Fellow with HKUST, in 2017. He was an Analog Design Engineer with Kilby Labs Silicon Valley, Texas Instruments,

Santa Clara, CA, USA, from 2018 to 2021. In 2021, he joined the Southern University of Science and Technology (SUSTech), Shenzhen, China, where he is currently an Associate Professor. His current research interests include power management IC design, especially in switched-mode power converter design.

Dr. Jiang was a recipient of the IEEE Solid-State Circuits Society Student Travel Grant Award 2015, the Analog Devices Inc. Outstanding Student Designer Award in 2015, the Solomon Systech Scholarship in 2017, the IEEE Solid-State Circuits Society Predoctoral Achievement Award in 2016–2017, the ASP-DAC University LSI Design Contest Special Feature Award in 2018, and the Texas Instruments Patent Awards in 2019-2020. He serves as a Review Committee Member of IEEE ISCAS from 2021 to 2023 and serves as an Associate Editor and Guest Editor for IEEE TRANSACTIONS OF CIRCUITS AND SYSTEMS II: EXPRESS BRIEFS.

**Zhiyuan Chen** (Member, IEEE) received the B.Sc., M.Sc., and Ph.D. degrees from the University of Macau, Macao, China, in 2011, 2013, and 2018, respectively.

Since 2018, he has been with the School of Microelectronics, Fudan University, Shanghai, China, where he is currently an Associate Professor. His research interests include ultralow power management systems, and solar and piezoelectric energy harvesting systems.

Dr. Chen is a member of the Technical Committee of Power and Energy Circuits and Systems in IEEE Circuits and Systems Society and has been the Review Committee Member of the IEEE International Symposium on Circuits and Systems since 2021. He was a recipient of the Macau Science and Technology Development Fund Postgraduates Award and Shanghai Super Postdoctoral Award.

Sijun Du (Senior Member, IEEE) received the First Class in B.Eng. degree in electrical engineering from University Pierre and Marie Curie (UPMC), Paris, France, in 2011, the M.Sc. degree (with distinction) in electrical and electronics engineering from Imperial College, London, U.K., in 2012, and the Ph.D. degree in electrical engineering from the University of Cambridge, Cambridge, U.K., in 2018.

He worked with the Laboratoire d'Informatique de Paris 6, UPMC, Paris, France, and then worked as a Digital IC Engineer in Shanghai, China, between

2012 and 2014. He was a Summer Engineer Intern with Qualcomm Technology, Inc., San Diego, CA, USA, in 2016. He was a Visiting Scholar with the Department of Microelectronics, Fudan University, Shanghai, China, in 2018. He was a Postdoctoral Researcher with Berkeley Wireless Research Center, Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA, USA, between 2018 and 2020. In 2020, he joined the Department of Microelectronics, Delft University of Technology (TU Delft), Delft, The Netherlands, where he is currently a tenured Assistant Professor. His current research is focused on energy-efficient integrated circuits and systems, including power management integrated circuits, energy harvesting, wireless power transfer, and dc/dc converters used in Internet-of-Things wireless sensors, wearable electronics, biomedical devices, and microrobots.

Dr. Du was a recipient of the Dutch Research Council (NWO) Talent Program-VENI Grant in the 2021 round. He was a corecipient of the Best Student Paper Award in IEEE ICECS 2022. He is a technical committee member of the IEEE Power Electronics Society and IEEE Circuits and Systems Society. He served as a subcommittee Chair of IEEE ICECS 2022, a review committee member of IEEE ISCAS from 2021 to 2023, and a committee member of the 2023 IEEE ISSCC Student Research Preview.