Delft University of Technology

## 3.1 A 120.9dB DR, -111.2dB THD+N Digital-Input Capacitively-Coupled Chopper Class-D Audio Amplifier

Zhang, Huajun; Berkhout, Marco; Makinwa, Kofi A.A.; Fan, Qinwen

DOI 10.1109/ISSCC42615.2023.10067400

Publication date 2023 **Document Version**

Final published version Published in

2023 IEEE International Solid-State Circuits Conference, ISSCC 2023

Citation (APA)

Zhang, H., Berkhout, M., Makinwa, K. A. A., & Fan, Q. (2023). 3.1 A 120.9dB DR, -111.2dB THD+N Digital-Input Capacitively-Coupled Chopper Class-D Audio Amplifier. In *2023 IEEE International Solid-State Circuits Conference, ISSCC 2023* (pp. 54-56). (Digest of Technical Papers - IEEE International Solid-State Circuits Conference; Vol. 2023-February). Institute of Electrical and Electronics Engineers (IEEE). https://doi.org/10.1109/ISSCC42615.2023.10067400

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

#### Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

# 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## ISSCC 2023 / SESSION 3 / AMPLIFIERS AND OSCILLATORS / 3.1

### 3.1 A 120.9dB DR, -111.2dB THD+N Digital-Input Capacitively-Coupled Chopper Class-D Audio Amplifier

Huajun Zhang<sup>1</sup>, Marco Berkhout<sup>2</sup>, Kofi A. A. Makinwa<sup>1</sup>, Qinwen Fan<sup>1</sup>

<sup>1</sup>Delft University of Technology, Delft, The Netherlands <sup>2</sup>Goodix Technology, Nijmegen, The Netherlands

Class-D amplifiers (CDAs) are widely used in audio applications where a high power efficiency is required. As most audio sources are digital nowadays, implementing digitalinput CDAs results in higher levels of integration and lower cost. However, prior open-loop digital-input CDAs suffer from high jitter sensitivity and output-stage distortion. In [1], jitter sensitivity at small signal levels is mitigated using a buck-boost converter that adaptively lowers the supply at the expense of extra external components and reduced power efficiency. Prior closed-loop digital-input CDAs employing multi-bit current-steering [2] or resistive [3] DACs are less sensitive to jitter, but their DR is limited to about 115dB. DAC non-idealities and intermodulation distortion are also challenges, and prior works only achieved a peak THD+N of about –98dB [2,3]. This paper presents a digital-input CDA that achieves high DR by combining a low-noise capacitive DAC (CDAC) with dedicated techniques to mitigate DAC mismatch, ISI, and intermodulation distortion. A prototype implemented in a 0.18μm BCD process achieves 120.9dB DR and 9–111.2dB peak THD+N. Furthermore, it can deliver 13W/23W at 10% THD into an 8Ω/4Ω T load with a 90%/86% efficiency.

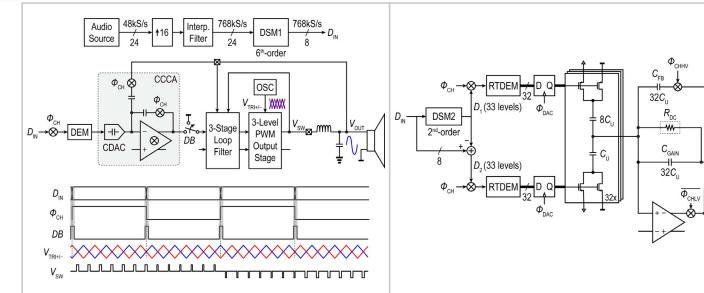

5.2023.100 To avoid the thermal and/or 1/f noise of current-steering or resistive DACs, a CDAC can  ${f ar {a}}$  be used to drive a closed-loop CDA based on the capacitively-coupled chopper-amplifier (CCCA) topology presented in [4]. Potential intermodulation between the DAC output waveform, which contains DAC images around multiples of fs as well as shaped quantization noise, and the various chopping and PWM tones must then be carefully mitigated. Figure 3.1.1 (top) shows an architectural overview of this capacitively-coupled chopper digital-input CDA. A 24-bit digital input is up-sampled to f<sub>s</sub>=768kHz (16×48kHz), reduced to 8 bits by a 6<sup>th</sup>-order digital  $\Delta\Sigma$  modulator (DSM1), and then converted into  $\overline{2}$  the analog domain by a CDAC. The latter drives a closed-loop CDA with an embedded CCCA front-end, a 14.4V 3-level PWM-based output stage, and feedback after the LC Hilter, enabling low noise and suppressing LC filter nonlinearity [4]. To compensate for the LC filter's phase shift, the loop filter must implement at least one zero, which inevitably causes some overshoot in its response to DAC transitions. At large signal levels, this will saturate the output stage and thus reduce the CDA's linear output range. S To keep the overshoot small, an 8-bit DAC is used, resulting in only a 0.5dB loss in the CDA's linear output range. Together with DSM1, the DAC achieves an SQNR of 136dB, ☆ CDA's linear output range. Together with Down, the Driv ushields an entry of a signal-to-jitter-noise ratio (SJNR) ≪a maximum stable amplitude (MSA) of 0.99FS, and a signal-to-jitter-noise ratio (SJNR) of 131.5dB when driven by a 768kHz clock with 100ps of white clock jitter.

9016 Chopping mitigates the CDA's 1/f noise and is performed at  $f_{CHOP}=f_S/2$  to exploit the spectral nulls in the shaped quantization noise at multiples of f<sub>s</sub> and, thus, avoid noise B folding. As shown in Fig. 3.1.1 (bottom), the chopping and DAC input transitions are aligned. After each transition, the CCCA will slew briefly before settling. To eliminate the eresulting nonlinearity and DAC ISI, a dead-band (DB) is introduced, which starts just before the chopping and DAC code transitions. During the DB, the CCCA is briefly disconnected from the rest of the loop filter. However, the resulting sample-and-hold ISSCC) operation also folds down (thermal) noise around integer multiples of fs. A 20ns DB is chosen as a compromise between CCCA settling and noise folding. The loop filter output  $\overset{9}{\bowtie}$  is re-modulated by a 3-level analog PWM modulator switching at  $f_{\text{PWM}}\text{=}4.992\text{MHz},$  which is an odd (13<sup>th</sup>) harmonic of  $f_{CHOP}$ . This avoids intermodulation distortion between the chopping and PWM sidebands [4]. However, this also means that  $f_{PWM}$  (=6.5 $f_s$ ) is not  $\frac{3}{2}$  located at a multiple of f<sub>s</sub> so some quantization noise folding will occur. Fortunately, the quantization noise around  $f_{PWM}$  is attenuated by the sinc roll-off of the DAC spectrum Circuits and the lowpass characteristics of the CDA's STF, so the folded noise is negligible (< -150dBFS). State

To reduce the complexity of the DEM scheme needed to achieve high linearity, the 8-bit pDAC is segmented. As shown in Fig. 3.1.2, the input of the MSB segment  $(D_1)$  is produced by a second digital modulator (DSM2), while the LSB segment is driven by the shaped quantization error  $(D_2)$  [5]. Ideally, no input-related content should be present in  $D_2$  such that the gain mismatch of the two DAC segments contributes only shaped noise. In [2,5], a 1<sup>st</sup>-order DSM is used, which could produce idle tones at small signal levels, leading to harmonic content in  $D_2$ . The gain mismatch between the segments will then allow some of this content to leak into the output. In this work, a 2<sup>nd</sup>-order DSM is used to 2008 allowing to a ls<sup>st</sup>-order DSM2. A 2-bit overlap is introduced between the 2 segments to 2 accommodate the extra swing caused by the shaped quantization noise of DSM2.  $D_1$  and

$D_2$  thus drive two sub-DACs with 8× and 1× weights, respectively. The (digitally) chopped DAC output  $D_{IN}\phi_{CH}V_{REF}$  is applied to a CCCA, which forms the loop filter's error amplifier.

The CCCA amplifies  $V_{ERR}$  (= $D_{IN}V_{REF}$ - $V_{OUT}$ /8) with a gain of 8× (=32×8 $C_U$ / $C_{GAIN}$ , since  $D_2$  does not contain the input signal), which attenuates the noise contribution from the rest of the loop filter by 18dB, while also ensuring that the CCCA does not clip due to the DAC images when a 20kHz full-scale input is applied. A total DAC capacitance (288 $C_U$ ) of 3.5pF is used such that the parasitic capacitance at the summing node does not degrade the feedback factor around the CCCA opamp. This implies a unit capacitance  $C_U$  of 12fF, which, together with  $C_{FB}$  and  $C_{GAIN}$ , is implemented with MOM capacitors due to their high voltage rating.

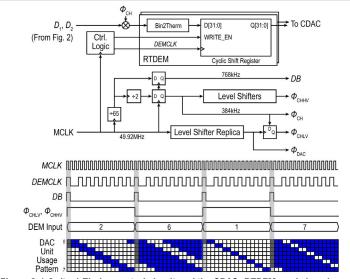

Unit-element mismatch within the two sub-DACs is addressed with real-time (RT) DEM [6], which produces no idle tones and achieves better SNDR at the chosen OSR (=19.2) than data-weighted averaging (DWA). Furthermore, since the DAC elements are driven by a PWM-like signal, their individual mismatch contribution is reduced at small input levels as the dutycycle of their PWM inputs approaches 50%. With RTDEM, however, code changes larger than 1 may cause nonlinear ISI [6], which will happen quite often since the DAC input is chopped. In this work, this source of nonlinearity is also eliminated by the DB. The timing control scheme to align RTDEM, DB, and chopping in both LV and HV domains is shown in Fig. 3.1.3. A 49.92MHz (=65f<sub>s</sub>) master clock (MCLK) is employed to define the DB and control the timing of RTDEM, where 1 MCLK cycle is allocated to the DB and 64 cycles to RTDEM. The number of transitions in the remaining time is signal-independent and thus distortion-free. RTDEM is realized using a cyclic shift register that loads thermometer-coded input data in parallel, which is then rotated to ensure that every DAC element is used equally outside the DB. Since the CDA has a nominal full-scale output of ±14.4V, the feedback chopper is realized with LDMOS switches that must be driven through level shifters, which have ~2ns delay. To avoid high-voltage transients, timing skew between the feedback chopper and DAC is minimized using a replica level shifter [4]. As a result, the DAC code transition ( $\phi_{DAC}$ ), HV, and LV chopping transitions ( $\phi_{CHHV}$  and  $\phi_{CHLV}$ ) are aligned and fully covered by the DB

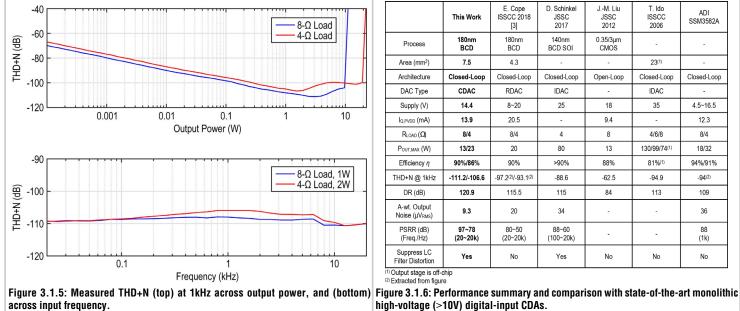

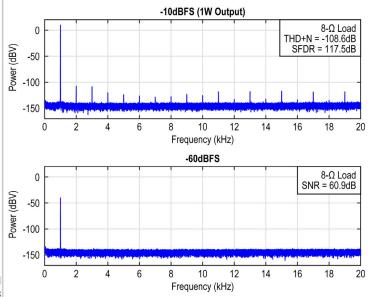

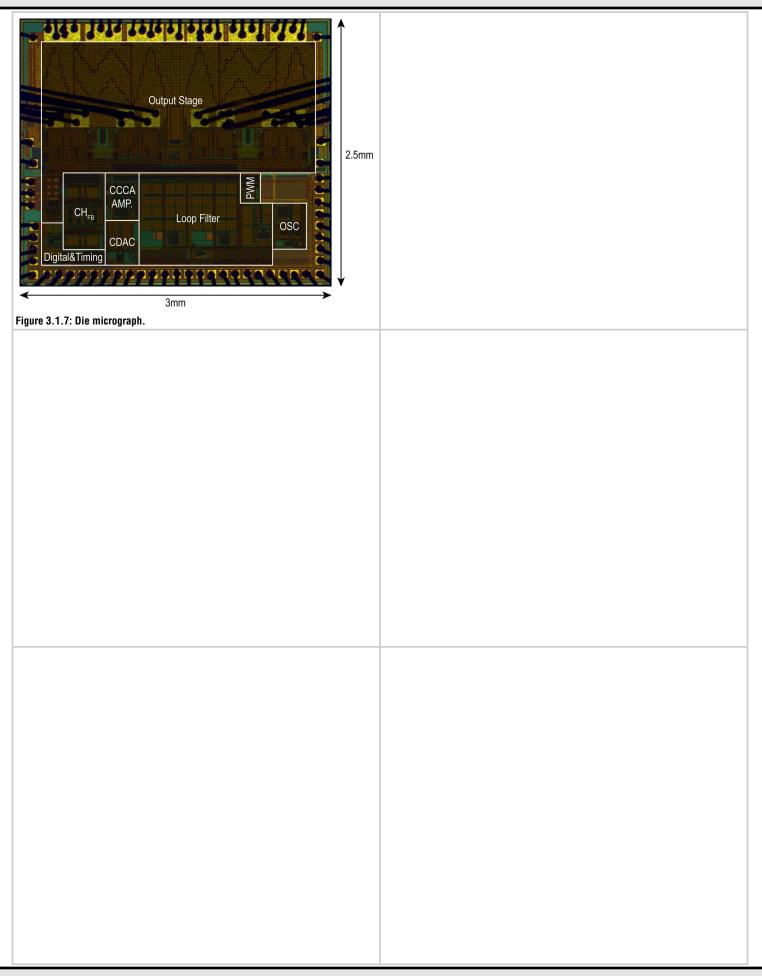

The capacitively-coupled digital-input CDA is prototyped in a 0.18µm BCD process and occupies an area of 7.5mm<sup>2</sup> (Fig. 3.1.7). An Audio Precision APx555 audio signal analyzer provides the 24-bit digital input and captures the CDA output. For flexibility, the interpolation filter and digital DSMs are implemented in an FPGA. The RTDEM and timing logic (Fig. 3.1.3) is implemented on-chip and consumes about 460µW from a 1.8V supply. Figure 3.1.4 (top) plots the output spectrum when the CDA drives an 8 $\Omega$  load with a –10dBFS sinewave input at 1kHz, corresponding to 1W of output power. The measured THD+N is –108.6dB. The output spectrum at –60dBFS is shown in Fig. 3.1.4 (bottom), where an SNR of 60.9dB is achieved, indicating that this CDA has a DR of 120.9dB. Figure 3.1.5 (top) shows the measured THD+N across output power or a 1kHz input. The peak THD+N is –111.2dB and –106.6dB for 8 $\Omega$  load and 4 $\Omega$  load, respectively. The output power at 10% THD is 13W and 23W for 8 $\Omega$  load and 4 $\Omega$  load, respectively. Figure 3.1.5 (bottom) plots the THD+N vs. input frequency.

Figure 3.1.6 compares the performance of this work with other state-of-the-art digitalinput CDAs. It is the only capacitively-coupled digital-input CDA. Compared to other high-voltage (>10V) CDAs, it achieves the best peak THD+N (14B lower than [3]), the highest dynamic range (5.4dB higher than [3]), and the lowest A-weighted integrated output noise (2× lower than [3]).

#### Acknowledgement:

The authors would like to thank Z. Chang, L. Pakula, and R. van Puffelen from the Delft University of Technology for measurement assistance.

#### References:

[1] W. H. Sun et al., "A 121dB DR, 0.0017% THD+N, 8× Jitter-Effect Reduction Digital-Input Class-D Audio Amplifier with Supply-Voltage-Scaling Volume Control and Series-Connected DSM," *ISSCC*, pp. 486-487, Feb. 2022.

[2] A. Matamura et al., "An 82mW  $\Delta\Sigma$ -Based Filter-Less Class-D Headphone Amplifier with -93dB THD+N, 113dB SNR and 93% Efficiency," *ISSCC*, pp. 432-433, Feb. 2021.

[3] E. Cope et al., "A 2×20W 0.0013% THD+N Class-D Audio Amplifier with Consistent Performance up to Maximum Power Level," *ISSCC*, pp. 56-57, Feb. 2018.

[4] H. Zhang et al., "A 121.4dB DR, -109.8dB THD+N Capacitively-Coupled Chopper Class-D Audio Amplifier," *ISSCC*, pp. 484-485, Feb. 2022.

[5] R. Adams et al., "A 113 dB SNR Oversampling DAC with Segmented Noise-Shaped Scrambling," *IEEE JSSC*, vol. 33, no. 12, pp. 1871-1878, Dec. 1998.

[6] S. -H. Wen et al., "A -117dBc THD (-132dBc HD3) and 126dB DR Audio Decoder with Code-Change-Insensitive RT-DEM Algorithm and Circuit Technique for Relaxing Velocity Saturation Effect of Poly Resistors," *ISSCC*, pp. 482-483, Feb. 2022.

## ISSCC 2023 / February 20, 2023 / 1:30 PM

3

$\phi_{\rm CHLV}$

Figure 3.1.1: Architecture of the proposed capacitively-coupled digital-input Figure 3.1.2: Simplified schematic of the 8-bit CDAC with noise-shaped segmentation Class-D audio amplifier. and the capacitively-coupled summing node of the loop filter.

Figure 3.1.3: (top) Timing control circuitry of the CDAC, RTDEM, and chopping, and (bottom) its timing diagram (for a 9-level sub-DAC, the actual implementation uses two 33-level sub-DACs).

|                                            | This Work         | E. Cope<br>ISSCC 2018<br>[3] | D. Schinkel<br>JSSC<br>2017 | JM. Liu<br>JSSC<br>2012 | T. Ido<br>ISSCC<br>2006 | ADI<br>SSM3582A |

|--------------------------------------------|-------------------|------------------------------|-----------------------------|-------------------------|-------------------------|-----------------|

| Process                                    | 180nm<br>BCD      | 180nm<br>BCD                 | 140nm<br>BCD SOI            | 0.35/3µm<br>CMOS        | -                       |                 |

| Area (mm <sup>2</sup> )                    | 7.5               | 4.3                          | -                           | -                       | 23(1)                   | -               |

| Architecture                               | Closed-Loop       | Closed-Loop                  | Closed-Loop                 | Open-Loop               | Closed-Loop             | Closed-Loop     |

| DAC Type                                   | CDAC              | RDAC                         | IDAC                        | -                       | IDAC                    | -               |

| Supply (V)                                 | 14.4              | 8~20                         | 25                          | 18                      | 35                      | 4.5~16.5        |

| Iq,pvdd (mA)                               | 13.9              | 20.5                         | -                           | 9.4                     | -                       | 12.3            |

| R <sub>LOAD</sub> (Ω)                      | 8/4               | 8/4                          | 4                           | 8                       | 4/6/8                   | 8/4             |

| POUT,MAX (W)                               | 13/23             | 20                           | 80                          | 13                      | 130/99/74(1)            | 18/32           |

| Efficiency $\eta$                          | 90%/86%           | 90%                          | >90%                        | 88%                     | 81%(1)                  | 94%/91%         |

| THD+N @ 1kHz                               | -111.2/-106.6     | -97.2(2)/-93.1(2)            | -88.6                       | -62.5                   | -94.9                   | -94(2)          |

| DR (dB)                                    | 120.9             | 115.5                        | 115                         | 84                      | 113                     | 109             |

| A-wt. Output<br>Noise (µV <sub>RMS</sub> ) | 9.3               | 20                           | 34                          | -                       | -                       | 36              |

| PSRR (dB)<br>(Freq./Hz)                    | 97~78<br>(20~20k) | 80~50<br>(20~20k)            | 88~60<br>(100~20k)          | -                       | -                       | 88<br>(1k)      |

| Suppress LC<br>Filter Distortion           | Yes               | No                           | Yes                         | No                      | No                      | No              |

high-voltage (>10V) digital-input CDAs.

## **ISSCC 2023 PAPER CONTINUATIONS**

• 2023 IEEE International Solid State Gir Guits Conference ownloaded on April 18,2023 at 13:40:55 UTC from 728 1x 6654 12016 rol 23/\$3.1.00 2023 IEEE