**Delft University of Technology**

## A Self Bias-flip Piezoelectric Energy Harvester Array without External Energy Reservoirs achieving 488% Improvement with 4-Ratio Switched-PEH DC-DC Converter

Li, Zhen; Chen, Zhiyuan; Law, Man-Kay; Du, Sijun; Cheng, Xu; Zeng, Xiaoyang; Han, Jun

DOI 10.1109/CICC57935.2023.10121219

**Publication date** 2023 **Document Version** Final published version

Published in Proceedings of the 2023 IEEE Custom Integrated Circuits Conference (CICC)

**Citation (APA)** Li, Z., Chen, Z., Law, M.-K., Du, S., Cheng, X., Zeng, X., & Han, J. (2023). A Self Bias-flip Piezoelectric Energy Harvester Array without External Energy Reservoirs achieving 488% Improvement with 4-Ratio Switched-PEH DC-DC Converter. In Proceedings of the 2023 IEEE Custom Integrated Circuits Conference (CICC) (pp. 1-2). IEEE. https://doi.org/10.1109/CICC57935.2023.10121219

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

## 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

### A Self Bias-flip Piezoelectric Energy Harvester Array without External Energy Reservoirs achieving 488% Improvement with 4-Ratio Switched-PEH DC-DC Converter

Zhen Li<sup>1</sup>, Zhiyuan Chen<sup>1</sup>, Man-Kay Law<sup>2</sup>, Sijun Du<sup>3</sup>, Xu Cheng<sup>1</sup>, Xiaoyang Zeng<sup>1</sup>, Jun Han<sup>1</sup>

<sup>1</sup>State Key Laboratory of ASIC and System, Fudan University, Shanghai, China

<sup>2</sup>State Key Laboratory of Analog and Mixed-Signal VLSI, University of Macau, Macau, China <sup>3</sup>Department of Microelectronics, Delft University of Technology, Delft, Netherlands

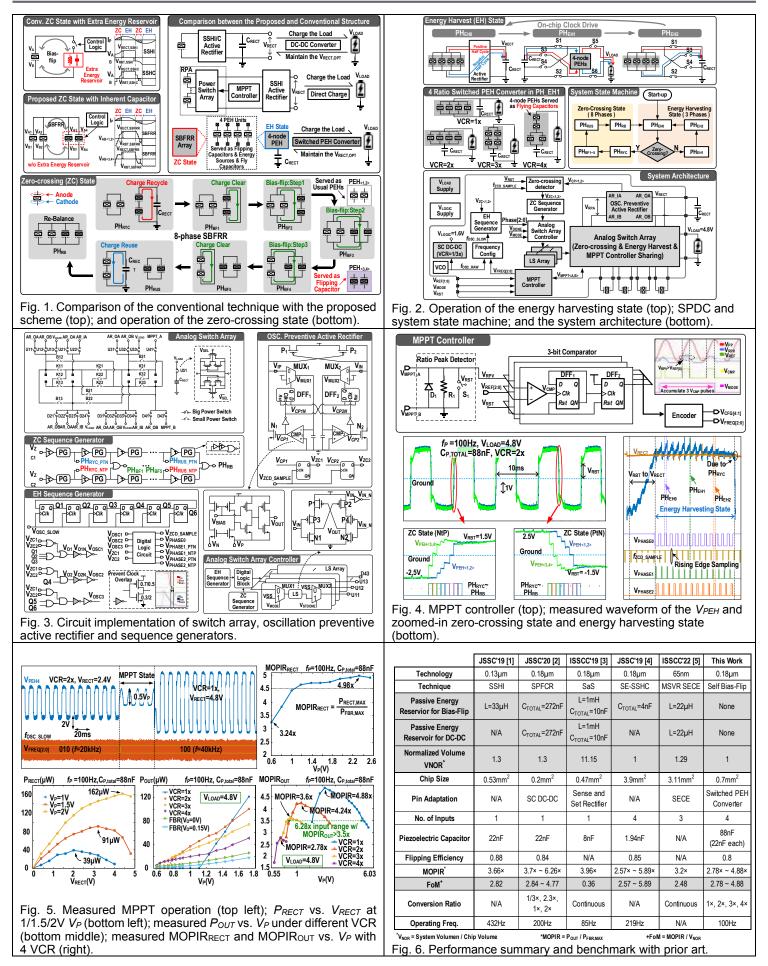

With the advent of the Internet-of-Things (IoT) era, sensor nodes are required in almost all fields to achieve a better interaction between humans and the environment. Piezoelectric energy harvester (PEH), which exhibits an equivalent electrical model of an AC current source  $I_P$  in parallel with the inherent capacitor  $C_P$ , is a promising technology to resolve the energy problem of such sensor nodes. Recently, inductor-based rectifiers, capacitor-based rectifiers and hybrid rectifiers have been proposed to improve the energy extraction efficiency of PEH devices [1-5]. However, these structures all require the aid of additional capacitors or inductors to achieve bias-flip operation, as illustrated in Fig. 1. These extra passive devices are typically large, which can be a major bottleneck in system-volumeconstrained applications such as MEMS [4]. In response to the above problem, this work proposes a novel 8-phase self bias-flip PEH interface with charge recycling and reusing (SBFRR). By using the C<sub>P</sub> of 4 PEHs as flipping capacitors, this scheme achieves a high voltage flipping efficiency without using extra energy reservoirs. The 4 CP can also serve as flying capacitors to achieve switched-PEH DC-DC (SPDC) conversion for MPPT, while maintaining a MOPIR of >3.5× with a PEH input voltage ( $V_p$ ) from 0.78V to 4.9V.

Fig. 1 shows the proposed system using 4 PEHs, with three operating states including energy harvesting (EH), zero-crossing (ZC), and MPPT. During the EH state, the 4 PEHs work as normal harvesters and flipping capacitors alternately to extract vibration power. The ZC state consists of the recycle phase (PH<sub>RYC</sub>), bias-flip phase (PH<sub>BF1~5</sub>), reuse phase (PH<sub>RUS</sub>) and rebalance phase (PH<sub>RB</sub>). For illustration purpose, we assign PEH<1,2> serve as conventional PEHs, and configure PEH<3,4> as flipping capacitors. Starting from  $PH_{RYC}$ ,  $PEH_{3,4}$  transfer half of the charge to  $C_{RECT}$ , followed by PH<sub>BF1</sub> where the residual charge is completely discharged. The charge on PEH<1,2> is gradually flipped in 3 steps from PHBF2 to PHBF4, and then finally cleared in PHBF5. To improve the energy extraction efficiency, the previously recovered charge at C<sub>RECT</sub> is re-injected to PEH<sub><1,2></sub> in PH<sub>RUS</sub>, and the PEH voltage is then equalized in PH<sub>RB</sub>. As the duration of the ZC state is about 80µs which accounts for only 1.6% of half the excitation cycle, PEH<3,4> can be regarded as flipping capacitors during this period without sacrificing the energy harvesting efficiency. The involvement of the charge recycle and reuse phases (i.e., PH<sub>RYC</sub> and PH<sub>RUS</sub>) can also theoretically improve the MOPIR from 3.88× to 5.13×.

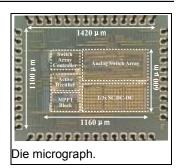

Fig. 2 presents the operation of the proposed SPDC at EH state, where the 4 PEHs serve as flying capacitors for DC-DC conversion to extend the input power range. It is composed of 3 phases (PHEH0~PHEH2). During PHEH0, the 4 PEHs transfer charges to CRECT through the active rectifier (AR), which is also responsible for zerocrossing detection and IP polarity determination. At PHEH1, the PEH array and CRECT together form a SPDC to deliver charge to the load, with a total 4 possible voltage conversion ratios (VCRs) through SPDC reconfiguration. To prevent error during zero-crossing detection at  $PH_{EH0}$ , the voltages on  $PEH_{<1,4>}$  and  $C_{RECT}$  are rebalanced in PHEH2. This can also prevent the PEH from deviating from the MPP. In this work, the time duration ratio of PH<sub>EH0</sub>~PH<sub>EH2</sub> is 3:1:2. The proposed system typically transits between the ZC and EH states. Upon the triggering of the external signal V<sub>MODE</sub>, the system will temporarily switch to the MPPT state. As observed in the system diagram, the AR outputs  $V_{CP<1,2>}$  serve to generate the corresponding ZC/EH pulse sequences to control the analog switch array. Dual supply domains are employed in order to reduce power consumption. The chip occupies an active area of ~0.7mm<sup>2</sup> as illustrated in the die micrograph.

Fig. 3 depicts the schematics of the key circuit modules. The analog switches are sized according to the path current to increase the power density. In order to prevent oscillation of  $V_{CP<1,2>}$  as induced by the comparator offsets, the proposed anti-oscillation technique

ensures that only one transition of  $V_{CP<1,2>}$  can occur per half excitation cycle.  $V_{CP<1,2>}$  will be sampled at 2/3 the duration of PH<sub>EH0</sub> to obtain  $V_{ZC<1,2>}$ , which is then processed by the ZC and EH sequencer to generate the required control sequence. The digital sequence generation blocks operate at 1.6V, and level shifters (LS) are employed to convert the 4.8-V supply for driving the switch

array. Each LS only consumes 0.53pJ per cycle.

We explore the fractional open-circuit voltage (FVOC) method for MPPT, and employ a ratioed peak detector to prevent detection error or overshoot. Here, D<sub>1</sub> is responsible for rectifying the PEH output, and R<sub>1</sub> for reducing the impedance across the PEH terminals. The detected peak voltage  $V_{RPV}$  is scaled to about 0.5V<sub>P</sub>. The 3-bit comparator outputs pulses according to  $V_{RPV}$  for triggering DFF<sub>1</sub> and DFF<sub>2</sub>, with the results further processed by the encoder to configure the VCR and  $f_{OSC_{SLOW}}$ .

Fig. 4 shows the measured waveform across the PEH terminals with VCR=2 at an excitation frequency of 100Hz. During the ZC state, after 8 phases of SBFRR operation, the PEH voltage is flipped from [2.5V] to [1.5V], corresponding to a voltage flipping efficiency of 80%. At EH state,  $V_{PEH<1,4>}$  is charged from the rebuilt voltage ( $V_{RBT}$ ), with the clock signal ( $f_{ZCD\_SAMPLE}$ ) triggering the sampling of  $V_{CP<1,2>}$ . When  $V_{PEH<1,4>}$  exceeds  $V_{RECT}$ , AR is turned on, and the system starts to operate among the EH phases (PH<sub>EH0</sub>~PH<sub>EH2</sub>). If  $V_{PEH<1,4>}$  is lower than  $V_{RECT}$ , the system will reenter the ZC state, leading to a droop at  $V_{RECT}$  as observed in Fig. 4 as induced by the charge injection in the PH<sub>RYC</sub> phase. This droop will be recovered in the PH<sub>RUS</sub> phase due to the connection to  $C_{RECT}$ .

Fig. 5 presents the MPPT results, where the system automatically switches from VCR=2 to VCR=1, with the driving clock fosc sLOW also adaptively updated. Fig. 5 also depicts the relationship between PRECT VERSUS VRECT under different VP, as well as POUT VERSUS VP under different VCR. The test results show that the energy loss caused by the vibration mismatches of four PEHs can be ignored. The measured MOPIR<sub>RECT</sub> can be up to 4.98× when  $V_P \sim 2.3$ V. The MOPIR is obtained by comparing the measured maximum output power with the calculated output power for an ideal full-bridge rectifier (with diode drop  $V_D=0$ ). When VCR=1, the MOPIR of the system can reach 4.88×. As VCR increases, the MOPIR reduces due to the reduction of the zero-crossing accuracy. However, when VCR=4, the MOPIR can still reach 2.78×, which is a 39% improvement compared to the ideal switch-only rectifier. The entire system can maintain a MOPIR of >3.5× when V<sub>P</sub> is from 0.78V to 4.9V. Fig. 6 shows the comparison of the proposed design with the state of the art. Compared to [4], this work achieves MPPT by using switched PEH converter while requesting a much smaller chip area. Compared to [1-3, 5], this work achieves the highest FoM without using external energy reservoirs, which is imperative to applications requiring an ultra-compact system volume.

## Acknowledgments:

The authors thank National Natural Science Foundation of China under Grant 61934002 and 62004041 for financial support.

#### **References:**

[1] S. Javvaji, *et al*, "Analysis and Design of a Multi-Step Bias-Flip Rectifier for Piezoelectric Energy Harvesting," JSSC, Sept. 2019.

[2] Z. Chen *et al.*, "Piezoelectric Energy-Harvesting Interface Using Split-Phase Flipping-Capacitor Rectifier With Capacitor Reuse for Input Power Adaptation," JSSC, Aug. 2020.

[3] Y. Peng *et al.*, "27.2 An Adiabatic Sense and Set Rectifier for Improved Maximum-Power-Point Tracking in Piezoelectric Harvesting with 541% Energy Extraction Gain," ISSCC, Feb.2019.

[4] S. Du, *et al*, "A Fully Integrated Split-Electrode SSHC Rectifier for Piezoelectric Energy Harvesting," JSSC, June 2019.

[5] S. Li, *et al*, "A 32nA Fully Autonomous Multi-Input Single-Inductor Multi-Output Energy-Harvesting and Power-Management Platform with 1.2×105 Dynamic Range, Integrated MPPT, and Multi-Modal Cold Start-Up," ISSCC, Feb. 2022.

## **IEEE CICC 2023**