Bottom-Up and Top-Down Approaches for the Design of Neuromorphic Processing Systems: Tradeoffs and Synergies Between Natural and Artificial Intelligence

Frenkel, C.; Bol, David; Indiveri, Giacomo

DOI

10.1109/JPROC.2023.3273520

**Publication date**

**Document Version** Final published version

Published in

Proceedings of the IEEE

Citation (APA)

Frenkel, C., Bol, D., & Indiveri, G. (2023). Bottom-Up and Top-Down Approaches for the Design of Neuromorphic Processing Systems: Tradeoffs and Synergies Between Natural and Artificial Intelligence. *Proceedings of the IEEE*, 111(6), 623-652. https://doi.org/10.1109/JPROC.2023.3273520

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## **Bottom-Up and Top-Down** Approaches for the Design of **Neuromorphic Processing** Systems: Tradeoffs and Synergies Between Natural and Artificial Intelligence

This article provides a comprehensive overview of bottom-up and top-down approaches, surveying key design choices and implementation strategies.

By Charlotte Frenkel<sup>®</sup>, Member IEEE, David Bol<sup>®</sup>, Senior Member IEEE, AND GIACOMO INDIVERI<sup>©</sup>, Senior Member IEEE

ABSTRACT | While Moore's law has driven exponential computing power expectations, its nearing end calls for new avenues for improving the overall system performance. One of these avenues is the exploration of alternative brain-inspired computing architectures that aim at achieving the flexibility and computational efficiency of biological neural processing systems. Within this context, neuromorphic engineering represents a paradigm shift in computing based on the implementation of spiking neural network architectures in which processing and memory are tightly colocated. In this article, we provide a comprehensive overview of the field,

paradigm shift is realized and comparing design approaches that focus on replicating natural intelligence (bottom-up) versus those that aim at solving practical artificial intelligence applications (top-down). First, we present the analog, mixed-signal, and digital circuit design styles, identifying the boundary between processing and memory through time multiplexing, in-memory computation, and novel devices. Then, we highlight the key tradeoffs for each of the bottom-up and top-down design approaches, survey their silicon implementations, and carry out detailed comparative analyses to extract design guidelines. Finally, we identify necessary synergies and missing elements required to achieve a competitive advantage for neuromorphic systems over conventional machine-learning accelerators in edge computing applications and outline the key ingredients for a framework toward neuromorphic intelligence.

highlighting the different levels of granularity at which this

Manuscript received 21 October 2022; revised 24 March 2023; accepted 28 April 2023. Date of publication 5 June 2023; date of current version 14 June 2023. This work was supported in part by the CHIST-ERA Grant CHIST-ERA-18-ACAI-004 under Grant SNSF 20CH21186999/1, in part by the European Research Council (ERC) through the European Union's Horizon 2020 Research and Innovation Program under Grant 724295, in part by the fonds européen de développement régional (FEDER), in part by the Wallonia within the "Wallonie-2020.EU" Program, in part by the Plan Marshall, and in part by the National Foundation for Scientific Research (F.R.S.-FNRS) of Belgium. (Corresponding author: Charlotte Frenkel.)

Charlotte Frenkel was with the Institute of Neuroinformatics. University of Zurich and ETH Zurich, 8057 Zurich, Switzerland. She is now with the Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS), Department of Microelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: c.frenkel@tudelft.nl).

David Bol is with the ICTEAM Institute, Université catholique de Louvain, 1348 Louvain-la-Neuve, Belgium (e-mail: david.bol@uclouvain.be).

Giacomo Indiveri is with the Institute of Neuroinformatics, University of Zurich and ETH Zurich, 8057 Zurich, Switzerland (e-mail: giacomo@ini.uzh.ch).

Digital Object Identifier 10.1109/JPROC.2023.3273520

KEYWORDS | Adaptive edge computing; event-based processing; low-power integrated circuits; neuromorphic engineering; on-chip online learning; spiking neural networks (SNNs); synaptic plasticity.

#### I. INTRODUCTION

Together with the development of the first mechanical computers came the ambition to design machines that can think, with first essays dating back to 1949 [1], [2]. The advent of the first silicon computers in the 1960s, together with the promise for exponential transistor integration (i.e., Moore's law, as first coined by Carver Mead [3]), further fuelled that ambition toward the development of embedded artificial intelligence (AI). As a key step toward brain-inspired computation, artificial neural networks (ANNs) were introduced based on the observation that the brain processes information with densely interconnected and distributed computational elements: the neurons. The successful deployment of the backpropagation of error (BP) learning algorithm, backed by steep progress in CPU and GPU computing resources, recently enabled a massive scaling of ANNs, allowing them to outperform many classical optimization and pattern recognition algorithms [4], [5]. Today, deep neural networks form a significant part of AI research [6], with applications ranging from machine vision (e.g., [6], [7], and [8]) to natural language processing (e.g., [9], [10], and [11]), often nearing or outperforming humans in complex benchmarking datasets, games of chance, and even medical diagnosis [12], [13], [14]. Yet, most of these AI successes focus on specialized problem areas and tasks, which can be referred to as narrow AI [15]. Although recent efforts aim at the development of an AI that is both more general and multimodal [15], [16], [17], [18], [19], current application-specific AI solutions deployed on centralized computing backends show a lack of both versatility and efficiency when compared to biological brains.

Versatility Gap: Despite the wide diversity of the abovementioned applications, task versatility is limited as each use case requires a dedicated and optimized network. Porting such networks to new tasks would at best require retraining with new data and at worst imply a complete redesign of the neural network architecture, besides retraining. The need to tailor and retrain networks for each use case is problematic as the amount of both data and computation needed to tackle state-of-the-art complex tasks has been growing by an order of magnitude approximately every year in the last decade. This growth rate is much faster than that of technology scaling and outweighs the efforts to reduce the network computational footprint [20]. To improve the ability of ANN-based AI to scale, diversify, and generalize from limited data while avoiding catastrophic forgetting, fewshot learning approaches based on meta-learning techniques are being investigated [21], [22], [23], [24], [25], [26]. These approaches aim at building systems that are tailored to their environment and can quickly adapt once deployed, just as evolution shapes the degrees of versatility and online adaptation of biological brains [27]. These are key aspects of the human brain, which excels at learning a model of the world from few examples [28].

Efficiency Gap: For tasks that animals need to solve, such as sensory processing, classification, or pattern recognition, the power and area efficiencies of current AI systems lag behind biological ones at all levels of complexity. Taking the game of Go as a well-known proxy for complex

applications, both task performance and efficiency ramped up quickly. From AlphaGo Fan [29], the first computer to defeat a professional player, to AlphaGo Zero [30], the one now out of reach from any human player, power consumption went from 40 kW to only about 1 kW [31]. However, even in its most efficient version, AlphaGo still lags two orders of magnitude behind the 20-W power budget of the human brain. While most of this gap could potentially be recovered with a dedicated hardware implementation, AlphaGo would still be limited to a single task. On the other end of the spectrum, for low-complexity tasks, a centralized cloud-based AI approach is not suitable to endow resource-constrained distributed wireless sensor nodes with intelligence, as data communication would dominate the power budget [32]. The trend is thus shifting toward decentralized near-sensor data processing, i.e., edge computing [33]. Shifting processing to the edge requires the development of dedicated hardware accelerators tailored to low-footprint ANN architectures, recently denoted as tinyML [34], [35], [36]. However, state-of-theart ANN accelerators currently burn on the order of milliwatts for basic image classification on small pixel patches, 1 thereby still lagging orders of magnitude behind biological efficiency. As a point of comparison, the honey bee brain has about one million of neurons for a power budget of 10  $\mu$ W only, yet it is able to perform tasks ranging from real-time navigation to complex pattern recognition while constantly adapting to its environment [39]. In order to minimize the energy footprint of edge computing devices, state-of-the-art techniques include minimizing accesses to centralized memories [40] and in-memory computing [41], advanced always-on wake-up controllers [42], [43], as well as weight and activation quantization [44], [45]. The field is thus naturally trending toward key properties of biological neural processing systems: processing and memory colocation, event-driven processing, and low-precision computation with binary spike encoding, respectively.

Therefore, to reach the goal of versatile and efficient computing electronic technologies, taking biological brains as a guide appears as a natural research direction. This strategy started in the late 1980s with neuromorphic engineering. The term "neuromorphic" was coined by Carver Mead with the observation that direct emulation of the brain ion channel dynamics could be performed by the MOS transistor operated in the subthreshold regime [46]. The field of neuromorphic engineering lies at the crossroads of neuroscience, computer science, and electrical engineering. It encompasses the study and design of bioinspired systems following the biological organizing principles and information representations. Therefore, at least in principle, the field of neuromorphic engineering aims at a twofold paradigm shift. First, while conventional

$<sup>^1</sup>$ As for the CIFAR-10 dataset [37], comprising ten classes of animal and vehicle images in a format of 32  $\times$  32 pixels. Hardware accelerator from [38] taken as a reference.

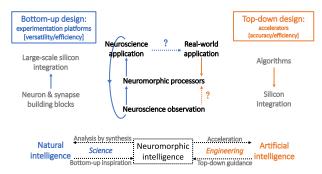

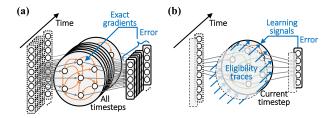

Fig. 1. Summary of the bottom-up and top-down design approaches toward neuromorphic intelligence. Bottom-up approaches optimize a tradeoff between versatility and efficiency; their key challenge lies in stepping out from analysis by synthesis and neuroscience-oriented applications toward demonstrating a competitive advantage on real-world tasks. Top-down approaches optimize a tradeoff between task accuracy and efficiency; their key challenge lies in optimizing the selection of bioinspired elements and their abstraction level. Each approach can act as a guide to address the shortcomings of the other.

von Neumann processor architectures rely on separated processing and memory, the brain organizing principles rely on distributed computation that colocates processing and memory with neuron and synapse elements, respectively [47]. This first paradigm shift therefore aims at releasing the von Neumann bottleneck in data communication between processing and memory, a point whose criticality is further emphasized by the recent slow down in the pace of Moore's law, especially for off-chip dynamic random-access memory (DRAM) [48]. Second, conventional von Neumann processor architectures encode data as multibit words that are processed sequentially by instructions, orchestrated by a global clock. Time is thus a by-product of computation and the resolution is determined by the number of bits used for encoding. On the contrary, the brain processes information by encoding data both in space and time with all-or-none binary spike events, each single axon potentially encoding arbitrary precision in the interspike time interval [49], [50], where time represents itself. This second paradigm shift aims at sparse event-driven processing toward reduced power consumption, especially if spikes are used all the way from sensing to computation. However, these paradigm shifts are often not fully attained in actual neuromorphic hardware: the granularity at which they are realized depends on the implementation choices and the design strategy that is followed, the latter being of two types: either bottom-up or top-down (see Fig. 1).

The former design strategy takes neuroscience as the starting point: it is a basic research approach toward understanding natural intelligence, backed by the design of experimentation platforms optimizing a trade-off between the versatility of the biophysical behaviors that can be reproduced and the system-level efficiency (i.e., versatility/efficiency tradeoff). The latter one departs from the selected use case: it is an applied research

approach grounded on today's ANN successes toward solving AI applications, backed by the design of dedicated hardware accelerators optimizing a tradeoff between the task-level accuracy and the system-level efficiency (i.e., accuracy/efficiency tradeoff). At the crossroads of both approaches, we argue that neuromorphic intelligence can form a unifying substrate toward the design of low-power bioinspired neural processing systems. Extending from [51], this article surveys key design choices and implementation strategies, thereby complementing previous circuit-, algorithm-, or system-level reviews [52], [53], [54], [55], [56]. We will first cover the different styles of analog and digital design, together with tradeoffs brought by time multiplexing and novel devices (Section II). Next, we will survey bottom-up design approaches in Section III, from the building blocks to their silicon implementations. We will then survey top-down design approaches in Section IV, from the algorithms to their silicon implementations. For both bottom-up and top-down implementations, detailed comparative analyses will be carried out so as to extract key insights and design guidelines. Finally, in Section V, we will outline the key synergies between both approaches, the open challenges and the perspectives toward on-chip neuromorphic intelligence for autonomous agents that efficiently and continuously adapt to their environment.

### II. NEUROMORPHIC CIRCUIT DESIGN STYLES

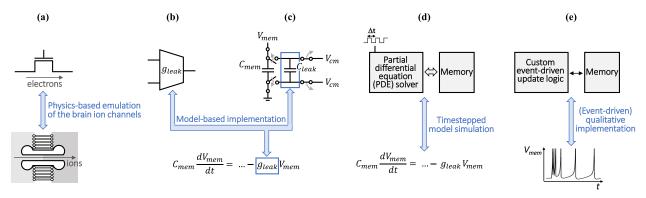

Regardless of the chosen bottom-up or top-down approach to the design of neuromorphic systems, different circuit design styles can be adopted, as shown in Fig. 2. Usually, a key question consists in choosing whether an analog or a digital circuit design style should be selected. In this section, we provide a principled analysis for choosing the circuit design style that is appropriate for a given use case.

Analog and digital neuromorphic circuit design each come in different flavors with specific tradeoffs. A qualitative overview is shown in Table 1. The tradeoffs related to analog and mixed-signal design are analyzed in Section II-A, and those of digital design are analyzed in Section II-B. Important aspects related to memory and computing colocation, such as time multiplexing and inmemory computation, are discussed in Section II-C. This highlight of the key drivers behind each circuit design style is then illustrated in Sections III and IV, where actual neuromorphic circuit implementations are presented and compared.

#### A. Analog and Mixed-Signal Design

Subthreshold or weak-inversion analog circuit design [Fig. 2(a)] allows leveraging an emulation approach directly grounded on the physics of the silicon substrate. Indeed, in the subthreshold regime, the current flow in the MOS transistor channel is governed by a diffusion mechanism, which is the same mechanism as for the

Fig. 2. Overview of the different neuromorphic circuit design styles, together with their key implementation strategies. (a) Subthreshold analog design offers a direct emulation of the brain ion channel dynamics directly grounded on the device physics of the MOS transistor, as the ion (resp. electron) flow in the brain ion channels (resp. the channels of MOS transistors in subthreshold regime) is governed by a diffusion mechanism. (b) and (c) Above-threshold analog design and SC mixed-signal design rely on a circuit implementation that corresponds one-to-one with the selected neuron mathematical model, respectively. (d) Solver-based digital design offers a straightforward approach based on PDE solvers, which can solve the chosen neuron mathematical model. This comes at the expense of time discretization and large data movement, given that the PDE solver has to fetch/update from/to memory the model state at discrete mathematical integration timesteps  $\Delta t$ . (e) These penalties can be reduced by following a phenomenological digital design approach, which implements specific neuron behaviors qualitatively using custom update logic, which can accommodate for sparse event-driven updates instead. Note that (b)–(e) focus on neuron models, but all design strategies can be applied to synapse or other biological computational primitives without loss of generality.

ion flow in the brain ion channels [46]. This emulation approach allows for the design of compact and low-power neuromorphic circuits that lie close to the brain biophysics. Considering voltage swings of 1 V for capacitors and currents on the order of 1 pF and 1 nA, respectively, the resulting time constants are on the order of milliseconds [57], close to those observed in biology. Subthreshold analog designs are thus inherently adapted for real-time and closed-loop processing of natural signals, using time constants that are well-matched to those of environmental and biological stimuli. Therefore, device-level biophysical modeling makes subthreshold analog designs suited for efficient brain emulation and basic research through analysis by synthesis. Subthreshold analog design allows for the emulation of a large range of neuronal behaviors and synaptic dynamics with few transistors, which we denote as an excellent versatility/efficiency tradeoff at the building block level, i.e., individual neurons and

synapses. However, these circuits are characterized by high sensitivity to noise, mismatch, and power, voltage, and temperature (PVT) variations. Ensuring reliable computation at the system level thus requires applying circuit calibration procedures [58], [59], [60] or increasing redundancy in neuronal resources so as to combine robust computational primitives [61], [62], [63]. Although these compensation techniques currently appear to degrade the versatility/efficiency tradeoff at the system level, they might provide additional benefits if variability can be exploited for computation and learning. Recent trends include variability-aware training (see Section IV-A) and exploiting neural parameter variability to support efficient and robust learning with temporal data [64], [65], [66], [67], [68], [69].

Above-threshold analog design [Fig. 2(b)] is suited for accelerated-time modeling of biological neural networks. Indeed, compared to subthreshold analog designs, even

Table 1 Properties and Tradeoffs of the Different Neuromorphic Circuit Design Styles. Elements Usually Representing Key Design Drivers Are Highlighted in Bold

| Implementation                                         | Ar<br>Subthreshold                                      | nalog<br>Above-threshold       | Mixed-signal Switched-capacitor              | Mixed-signal D<br>Switched-capacitor Solver-based            |                                |

|--------------------------------------------------------|---------------------------------------------------------|--------------------------------|----------------------------------------------|--------------------------------------------------------------|--------------------------------|

| Dynamics Versatility/efficiency tradeoff Time constant | Physics-based<br>(Excellent) <sup>‡</sup><br>Biological | Model-based Medium Accelerated | Model-based  Good  Biological to accelerated | Timestepped Event-driven* Bad Good Biological to accelerated |                                |

| Noise, mismatch, PVT sensitivity                       | High                                                    | Medium                         | Medium to low                                | δ                                                            | _                              |

| Indirect overhead                                      | Bias g                                                  | eneration                      | Clocked digital control                      |                                                              | tree (sync)<br>support (async) |

| Design time                                            | High                                                    |                                | High                                         | Low (sync)<br>Medium (async)                                 |                                |

| Technology scaling potential                           | Low                                                     |                                | Medium                                       | High                                                         |                                |

| Programmability                                        | I                                                       | ow                             | Low                                          | High                                                         |                                |

<sup>\*</sup> Although phenomenological digital designs can also implement timestepped updates, event-driven updates are the preferred choice to reduce data movement.

† Degrades at the system level if variability is not exploited and requires compensation.

when the capacitor size is of the same order (e.g., 1 pF), higher currents and reduced voltage swings produce acceleration factors ranging from 10<sup>3</sup> to 10<sup>5</sup> compared to biological time, thus mapping year-long biological developmental timescales to day-long runtimes [70], [71], [72]. However, as the current flow in the channel of the MOS transistor operated in the above-threshold regime is governed by a drift mechanism instead of diffusion, emulation of neural processes cannot take place anymore at the level of the device physics. Instead, the implementation of neural processes is done at a higher level by following the selected neuron/synapse mathematical model: following a structured analog design approach, appropriate analog circuits with tunable parameters are designed for each term of the equations in the chosen models [73]. Although transistors operated in the above-threshold regime have an improved robustness to noise, mismatch, and PVT variations compared to the ones operated in subthreshold, device mismatch is still a critical problem that requires mitigation at the circuit and system levels. Therefore, calibration procedures are also common and sometimes directly integrated in the hardware [74].

Designs based on switched-capacitor (SC) circuits [Fig. 2(c)] exhibit an interesting blend between specific properties of subthreshold and above-threshold analog designs. Similar to the above-threshold designs, they follow a higher-level implementation; however, computation is carried out in the charge domain instead of the current domain. SC neuromorphic designs are thus able to achieve not only accelerated time constants but also biologically realistic ones. Furthermore, replacing nanoampere-scale currents by the equivalent accumulated charge has the advantage of reducing the sensitivity to noise, mismatch, and PVT variations [75], [76]. The price to pay, however, is the overhead added by the clocked digital control of SC circuits, which can take up a significant portion of the system power consumption. As the digital part of this overhead can benefit from technology scaling, an overall good versatility/efficiency tradeoff for SC circuits in advanced technology nodes is possible [76]. Switched capacitors can also be used to implement time multiplexing (see Section II-C).

#### B. Digital Design

As opposed to their analog counterparts, digital designs forgo the emulation approach. Instead, they simulate neural processes, thereby relying on circuit implementations that lie far from the biophysics, which does not allow exploiting the dynamics of the silicon substrate. More circuit resources are thus needed to reproduce a large repertoire of neural behaviors and synaptic dynamics, thereby degrading the versatility/efficiency tradeoff. In exchange, digital designs are robust to noise, mismatch, and PVT variations, can leverage technology scaling, and can offer high programmability with the support of different models and functions. The former ensures a predictable behavior and

possibly a one-to-one correspondence with the simulation software, while the latter ensures competitive power and area efficiencies with deep sub-micron technologies.

The most straightforward starting point for digital neuromorphic design is to implement solvers for the partial differential equations (PDEs) modeling the biophysical behavior of neurons and synapses, which requires retrieving and updating all model states at every integration timestep [77], [78], [79], [80] [Fig. 2(d)]. This implies an extensive and continuous amount of data movement and computation, including when no relevant activity is taking place in the network. Therefore, these approaches have poor power and area efficiencies, especially at accelerated time constants. Piecewise linear approximations of neuron models have been proposed to reduce the complexity and resource usage [81], [82]; however, they still require an update of all model states after each discrete mathematical integration timestep of the PDEs. In order to minimize updates, some studies analyzed the maximum integration timestep values for a given neuron model [83]. In any case, the extensive data movement implied by solver-based digital implementations makes them difficult to match with a low-power event-driven neuromorphic approach.

Phenomenological digital design [Fig. 2(e)] aims at reducing the timestepped data movement overhead of its solver-based counterpart by carrying out updates when and where relevant in the neural network. To do so, two strategies can be followed: either the detail level of biophysical modeling can be reduced and the model simplified or key behaviors of complex models can be qualitatively implemented using custom update logic, thereby forgoing the underlying mathematical model and the exact dynamics. While referring to Section III-A1 for the neuron models mentioned in the following, key examples on each side can be seen in:

- for the former, the popular leaky integrate-andfire neuron model, which eliminates all biophysical details of ion channels and only keeps the leaky integration property of the neuron membrane;

- 2) for the latter, the design of [84] that sidesteps the Izhikevich neuron model equations and instead aims at a low-cost reproduction of its firing behaviors.

In both examples given above, the model requirements are sufficiently relaxed so as to allow for event-driven state updates, thus strongly reducing data movement and the associated overhead. As the strategy to be pursued and the approximations that can be made depend on the chosen application, phenomenological digital design is a codesign approach trading off model complexity, biophysical accuracy, and implementation efficiency.

Finally, for both solver-based and phenomenological approaches, a significant source of overhead is the clock tree, which for modern synchronous digital designs represents 20%–45% of the total power consumption [85]. Although clock gating techniques can help, this leads to a tradeoff between power and complexity that is a severe

issue for neuromorphic circuits, whose activity should be event-driven. Asynchronous digital circuits avoid this clock tree overhead and ideally support the event-driven nature of spike-based processing. This is the reason why asynchronous logic is a widespread choice for the onand off-chip spike communication infrastructures of neuromorphic systems, both analog and digital. However, asynchronous circuit design currently suffers from a lack of native support in standard industrial computer-aided design (CAD) tools. Indeed, all neuromorphic systems embedding asynchronous logic rely on a custom tool flow (e.g., see [63], [86], [87], [88], [89], and [90]), which increases the design time and requires support from a team experienced in asynchronous logic design. The custom flows employed in these designs all derive from the asynchronous digital design tools initially developed at Caltech in the 1990s [91], which are now mainly maintained at Yale University, New Haven, CT, USA, and have recently been made open source [92]. Another emerging solution consists in applying specific constraints to standard industrial digital CAD tools so as to automatically optimize the timing closure of asynchronous bundleddata circuits [93], [94], [95]. This idea was recently applied in the context of networks-on-a-chip (NoCs), where Bertozzi et al. [96] demonstrated significant powerperformance-area improvements for asynchronous NoCs compared to synchronous ones while maintaining an automated flow based on standard CAD tools. Leveraging the efficiency of asynchronous circuits with a standard digital tool flow may soon become a key element to support the large-scale integration of neuromorphic systems.

## C. Defining the Boundary Between Memory and Processing—Time Multiplexing, In-Memory Computation, and Novel Devices

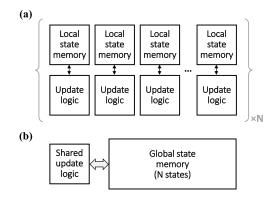

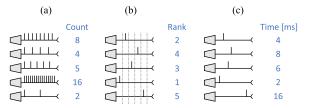

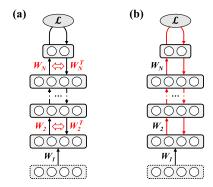

Neuromorphic engineering aims at a paradigm shift from von-Neumann-based architectures to distributed and cointegrated memory and processing elements. However, the granularity at which this paradigm shift is achieved in practice strongly depends on the selected memory storage and on the level of resource sharing. Indeed, a key design choice for neuromorphic architectures consists in selecting between a fully parallel resource instantiation and the use of a time multiplexing scheme (i.e., shared update logic and centralized state storage), as shown in Fig. 3(a) and (b), respectively. A summary of the tradeoffs between both approaches is shown in Table 2. An important benefit of time multiplexing is the substantial reduction of area footprint, usually by one to three orders of magnitude, at the expense of a reduction in the maximum throughput. This throughput reduction is usually not problematic, unless when targeting acceleration factors higher than one order of magnitude compared to biological time. Importantly, regarding the power consumption, the penalty for fully parallel implementations is in static power (through the duplication of circuit resources with leakage

Fig. 3. Qualitative illustration of (a) fully parallel and (b) timemultiplexed architectures for N elements (e.g., neurons or synapses) and of their memory access bottleneck.

power), while the penalty for time-multiplexed designs is in dynamic power (through an increase in memory accesses to centralized state storage). Therefore, minimizing leakage is necessary for fully parallel designs, while state updates should be minimized for time-multiplexed ones, thereby highlighting the energy efficiency penalty of time-multiplexed PDE solvers carrying out updates at every integration timestep.

While time multiplexing based on on-chip static random-access memory (SRAM) is applied to nearly all digital designs due to its ease of implementation for a minimized area footprint, this technique is not applied to analog designs if a fully parallel emulation of the network dynamics is to be maintained. Otherwise, time multiplexing can be applied to analog designs as well, as shown in [71], [76], [97], and [98]. It can be either SRAM-based or capacitor-based, and the former is a mixed-signal approach that minimizes the storage area for large arrays but requires digital-to-analog (DAC) converters, while the latter avoids DACs at the expense of a higher footprint for storage. In both cases, the addition of digital control logic is required. Furthermore, time multiplexing can also be applied selectively to different building blocks. As synapses are usually the limiting factor (Section III-A2), a good example consists of time-multiplexed synapses and fully parallel neurons, as in [97], which represents an interesting tradeoff to minimize the synaptic footprint while keeping continuous parallel dynamics at the neuron level.

Finally, an important aspect of fully parallel implementations is to enable synergies with in-memory computation, where computation takes place in the memory itself, a trend that is popular not only in neuromorphic engineering [99] but also in conventional machine-learning accelerators based on SRAM [41], DRAM [100], and novel devices [101]. A recent comparative analysis by Peng et al. [102] shows that, at normalized resolution and compared to six different memristor technologies, SRAM still offers the highest accuracy, throughput, density, and power efficiency for deeply scaled processes. However,

Table 2 Properties and Tradeoffs of Fully Parallel and Time-Multiplexed Designs. Elements Usually Representing Key Design Drivers Are Highlighted in Bold

| Implementation       | Fully-parallel                                  | Time-multiplexed                                         |  |  |

|----------------------|-------------------------------------------------|----------------------------------------------------------|--|--|

| Time                 | Analog: represents itself<br>Digital: simulated | Simulated                                                |  |  |

| Continuous dynamics  | Intrinsic ✓                                     | Timestepped updates: ✓ (power ↑) Event-driven updates: ✗ |  |  |

| Mem/proc co-location | Highest granularity                             | SRAM: Cache-level granularity Off-chip DRAM: X           |  |  |

| Maximum throughput   | High                                            | Low                                                      |  |  |

| Power penalty        | Static                                          | Dynamic                                                  |  |  |

| Area footprint       | High                                            | Low                                                      |  |  |

while SRAM-based in-memory computation allows for efficient matrix–vector product acceleration, it is not typically encountered in spiking neural network (SNN) accelerators due to a lack of proper sparsity support, as opposed to fully parallel memristor arrays.

Instead, fully parallel memristor crossbar arrays are a promising avenue for in-memory computation in neuromorphic systems [103], [104], [105]. Beyond the usual prospects for improvement in density and power efficiency linked with in-memory computation, memristors offer specific synergies for neuromorphic engineering with characteristics similar to those of biological synapses [106], e.g., learning dynamics, stochastic readout, few-bit device resolution, and dense nanoscale integration. Furthermore, a neuromorphic approach exploiting nonidealities instead of mitigating them could be particularly appropriate to alleviate the high levels of noise and mismatch encountered in these devices [103] or to take advantage of parasitic effects such as the conductance drift [107]. However, high-yield large-scale cointegration with CMOS is still at an early stage [108], [109].

#### III. BOTTOM-UP DESIGN APPROACH— TRADING OFF BIOPHYSICAL VERSATILITY AND EFFICIENCY

The vast majority of neuromorphic designs follow a bottom-up strategy, which is also the historic one adopted since the first neuromorphic chips from the late 1980s. It takes its roots in neuroscience observations and then attempts at: 1) replicating these observations in silico and 2) integrating them at scales ranging from hundreds or thousands [76], [90], [98], [110], [111], [112], [113], [114] to millions of neurons [71], [86], [87], [88], [89], leading to a tradeoff between versatility and efficiency. Integrations reaching a billion neurons can be achieved when racks of neuromorphic chips are assembled in a supercomputer setup. The simulation in real time of about 1% of the human brain is currently possible [115] and of the full human brain within a few years [116]. Bottomup approaches thus allow designing experimentation platforms that support acceleration of neuroscience simulations [71], brain reverse engineering through analysis by synthesis [47], [117], and even the exploration of hybrid setups between biological and artificial neurons [118], [119]. Their application to brain-machine

interfaces [120], [121] and closed sensorimotor loops for autonomous cognitive agents [122], [123], [124], [125] is also under investigation. However, the inherent difficulty of bottom-up approaches lies in applying the resulting hardware to real-world problems beyond the scope of neuroscience-oriented applications, a point that is further emphasized by the current lack of appropriate and widely accepted neuromorphic benchmarks [126]. Therefore, bottom-up designs have so far been mostly used for basic research. In this section, as highlighted in Fig. 1, we follow the steps of the bottom-up approach by surveying neuromorphic designs from the building block level (Section III-A) to their silicon integration (Section III-B).

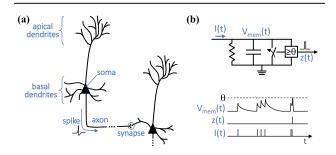

#### A. Building Blocks

As the key computational elements of biological systems, the neurons carry out nonlinear transformations of their inputs, both in space and time, and are divided into three stages (Fig. 4): the dendrites act as an input stage, the core computation takes place in the soma, and the outputs are transmitted along the axon, which connects to dendrites of other neurons through synapses. The soma, often simply referred to as a neuron in neuromorphic systems, is covered in Section III-A1. The synapses, dendrites, and axons are then covered in Sections III-A2, III-A3, and III-A4, respectively. The neural tissue also contains glial cells, which are believed to take a structuring and stabilizing role [128] with a few silicon implementations [129], [130], but whose study is beyond the scope of this survey.

#### 1) Neurons (Soma):

One of the simplest neuron models, which originates from the work of Lapicque [131], describes biological neurons as integrating synaptic currents into a membrane potential and firing a spike (i.e., action potential) when the membrane potential exceeds a firing threshold, after

Fig. 4. Simplified neuron morphology and modeling. (a) Neurons are composed of a soma, an axon, and dendrites (in pyramidal neurons, apical dendrites receive feedback from higher order brain areas, and basal dendrites are close to the soma and receive feedforward sensory inputs). Adapted and extended from [127]. (b) The LIF neuron model is a first-order approximation of the biological neuron as an RC filter with a spiking nonlinearity and a reset mechanism. The firing threshold is denoted as  $\theta$ , the membrane potential is denoted as  $V_{mem}(t)$ , the input dendritic current is denoted as I(t), and the spiking output is denoted as Z(t).

which the membrane potential is reset. It is thus referred to as the integrate-and-fire (I&F) model, while the addition of a leakage term leads to the integrate-and-fire (LIF) model, which emphasizes the influence of recent inputs over past activity [132]. This basic linear-filter operation can be modeled by an RC circuit. The widespread I&F and LIF models are phenomenological models: they aim at computational efficiency while exhibiting, from an input-output point of view, a restricted repertoire of biophysical behaviors chosen for their prevalence or relevance for a specific application. On the other end of the neuron models spectrum, conductance-based models aim at a faithful correspondence with the biophysics of biological neurons. The Hodgkin-Huxley (H&H) model [133] lies the closest to the biophysics but is computationally intensive as it consists of four nonlinear ordinary differential equations. The Izhikevich model is a 2-D reduction of the H&H model [134] that can still capture the 20 main behaviors of biological spiking neurons found in the cortex [135], but whose parameters have lost correspondence with the biophysics. The adaptiveexponential (AdExp) 2-D model is similar to the Izhikevich model and differs by the nonlinearity in the spiking mechanism, which is exponential instead of quadratic [136]. Due to this exponential, the AdExp neuron model suits well a subthreshold analog design approach and can be seen as a generalized form of the Izhikevich model. We refer the reader to [135] for a detailed neuron model summary.

The choice of the neuron model is also intrinsically tied to the target neural coding approach. As the I&F neuron model only behaves as an integrator, it does not allow leveraging complex temporal information [137]. Therefore, the I&F model is usually restricted to the use of the rate code [Fig. 5(a)], a standard spike coding approach directly mapping continuous values into spike rates [50]. It is a popular code due to its simplicity, which also allows for straightforward mappings from ANNs to SNNs [138], [139], [140], at the expense of a high power penalty as each spike only encodes a marginal amount of information. This aspect can be partly mitigated with the use of the rank order code [Fig. 5(b)], sometimes used as an early stopping variant of the rate code, without considering relative timings between spikes. Behavior versatility is thus necessary to explore codes that embed higher amounts of data bits per spike and favor sparsity by leveraging time, such as the timing code [50], [141], [142], [143], where the popular time-to-first-spike (TTFS) variant encodes information in the time taken by a neuron to fire its first spike [Fig. 5(c)]. In order to efficiently exploit temporal codes, neurons must capture time into computation [135]. We discuss in [111] how the 20 Izhikevich behaviors of biological cortical spiking neurons offer a variety of ways to do so.

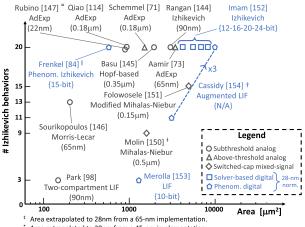

Therefore, the tradeoff between biophysical versatility and implementation efficiency of silicon neurons is strongly dependent on the underlying model, the target

Fig. 5. Main encodings in SNNs, as defined in [50]. The neuron axons represent a time axis, the most recent spikes being closest to the soma. (a) Conventional rate code, easy to use, and accurate but inefficient in its spike use. (b) Rank order code, efficient in its spike use but with limited representational power. (c) Timing code in the specific case of TTFS encoding, both efficient in its spike use and accurate, illustrated for an arbitrary resolution of 1 ms.

code, and whether an emulation or a simulation implementation strategy is pursued (Table 1). An overview of the current state of the art for analog, mixed-signal, and digital neurons is shown in Fig. 6. Only standalone non-time-multiplexed neuron implementations are shown for a fair comparison of their versatility/efficiency tradeoff, measured here by the number of Izhikevich behaviors and the silicon area, respectively. The physics-based emulation approach pursued with subthreshold analog design achieves overall excellent versatility/efficiency tradeoffs [114], [144], [145], [146], [147], followed closely by model-based above-threshold analog designs [71], [73]. By their similarity with the Izhikevich model, which is implemented in [144], AdExp neurons are believed to reach the 20 Izhikevich behaviors [148], although it has not been demonstrated in their silicon implementations in [71], [73], [114], and [147]. The conductance- and Hopf-bifurcation-based neuron of [145] is also able to reproduce the full repertoire of Izhikevich behaviors. Neuron implementations from [87] and [149] should provide similar tradeoffs, but no information is provided as to their number of Izhikevich behaviors. With a reduced number of behaviors, mixed-signal SC implementations of the Mihalas-Niebur model in [150] and [151] were demonstrated to exhibit 9 and 15 out of the 20 Izhikevich behaviors, respectively, although with relatively high area due to their older technology node. The Morris-Lecar model is also explored in [146] and is believed to reach 13 out of the 20 Izhikevich behaviors [135]. The phenomenological approach is followed in [98] with LIF neurons in an extended two-compartment version that models separate dendritic voltages. On the other hand, digital designs release the constraints on design time and sensitivity to noise, mismatch, and PVT variations at the expense of going for a simulation approach lying further from the biophysics, thus inducing overall large area penalty compared to analog designs. This is illustrated in the neuron implementation from [152] that implements a timestepped solver for the differential equations of the Izhikevich neuron model, while the phenomenological approach is followed in [153] with a 10-bit LIF neuron. Between both

- Area extrapolated to 28nm from a 45-nm implementation

- Area estimated from TrueNorth's layout in 28nm, excluding on-chip memory storage [88]

- Standalone version (pre-silicon), later time-multiplexed and implemented in ODIN [111].

- Contributions from shared neuron soma and threshold adaptation circuits are excluded

Fig. 6. State of the art of analog and digital neuron implementations: versatility (measured in the number of Izhikevich behaviors) against area tradeoff. The area of digital designs has been normalized to a 28-nm node using the node factor. This normalization has not been applied to analog designs as they require redesign to compensate for performance degradation during technology scaling: original area and technology node are reported. All neurons presented in this figure are standalone (i.e., not time-multiplexed), except in [154] for which only the update logic area is reported and in [150] for which contributions from shared soma and threshold adaptation circuits are excluded. The designs from [71], [73], [114], and [147] emulate an AdExp neuron model and are thus believed to reach the 20 Izhikevich behaviors [148], though not demonstrated. Adapted and extended from [84].

approaches lies the neuron model of Cassidy et al. [154], it is based on an LIF neuron model to which configurability and stochasticity are added. This model is used in the TrueNorth chip [88] and exhibits 11 Izhikevich behaviors, while the 20 behaviors can be reached by coupling three neurons together, showing a configurable versatility/efficiency tradeoff. Finally, the event-driven phenomenological Izhikevich neuron proposed in [84] alleviates the efficiency gap of digital approaches by pursuing a direct implementation of the Izhikevich behaviors, not of the underlying mathematical model [134].

#### 2) Synapses:

Biological synapses embed the functions of memory and plasticity in extremely dense elements [47], allowing neurons to connect with 100-to-10k incoming synapses per neuron (i.e., fan-in) [155]. Optimizing the versatility/efficiency tradeoff appears as especially critical for the synapses, as they often dominate the area of neuromorphic processors, sometimes by more than one order of magnitude [114]. In order to achieve large-scale integrations, designers often either move synaptic resources off-chip (e.g., [86] and [87]), which comes at the expense of an increase in the system power and latency [48], or drop the key feature of synaptic plasticity, thereby relying on static synaptic weights that

are frozen once initialized (e.g., [88] and [90]). However, retaining embedded online learning is important for three reasons. First, it allows low-power autonomous agents to collect knowledge and adapt to new features in uncontrolled environments, where new training data are presented on-the-fly in real time [39], [125]. Second, from a computational efficiency point of view, neuromorphic designs deprived from synaptic plasticity rely on off-chip optimizers, thus precluding deployment in applications that are power- and resource-constrained not only in the inference phase but also in the training phase. Finally, exploring biophysically realistic silicon synapses embedding spike-based plasticity mechanisms may help unveil how they operate in the brain and support cognition [156]. This bottom-up analysis-by-synthesis step (Fig. 1) may also ideally complement top-down research in bioplausible BP algorithms (see Section IV-A). Therefore, a careful hardware-aware selection of spike-based synaptic plasticity rules is necessary for the design of efficient silicon synapses.

A wide range of plasticity mechanisms are believed to take place at different timescales in the brain, where it is common to segment them into four types [47], [157], [158], [159], listed hereafter starting with the shortest timescales. First, short-term plasticity (STP) operates over milliseconds and covers short-term synaptic adaptation mechanisms, such as short-term facilitation (STF) and short-term depression (STD), which have useful properties for efficient coding and multiplexing of spiking signals [160], [161], [162]. A few analog CMOS implementations of STP have been proposed, e.g., in [76] and [114]. Second, long-term plasticity mechanisms operate over tens to hundreds of milliseconds and cover spike-based plasticity rules, as well as working memory dynamics [163]. Third, homeostatic plasticity operates over tens to hundreds of seconds and allows scaling synaptic weights to stabilize the neuron firing frequency ranges and, thus, the network activity [164]. There is a particular interest for homeostatic plasticity in analog designs so as to compensate for PVT variations at the network level [165]. The design of efficient strategies for circuit implementations of homeostaticity is not yet mature: achieving long homeostatic timescales in analog CMOS design is challenging, although solutions have been proposed for subthreshold design in [166], while it incurs high control and memory access overheads in time-multiplexed digital designs. Finally, structural plasticity operates over days to modify the network connectivity [167]. It is usually applied to the mapping tables governing system-level digital spike routers (see Section III-A4).

As the timescale of long-term plasticity rules is usually appropriate to perform training on spike-based image and sound classification tasks, an important body of work covers their silicon implementations, whose implementations in the mixed-signal domain have recently been reviewed in [168]. Being one of the first formulations of a long-term spike-based plasticity mechanism relying on experimental

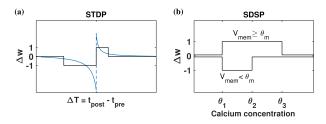

Fig. 7. Illustration of the STDP and SDSP spike-based learning rules. In order to highlight their suitability for digital design, the amplitude scaling factors of SDSP and the digital version of STDP have been normalized for unit weight updates  $\Delta w$ . (a) STDP learning rule (blue) with the popular approximation proposed by Cassidy et al. [175] (black). (b) SDSP learning rule from [178]. Adapted from [111] and [181].

data derived by Bi and Poo [169], pair-based spike-timingdependent plasticity (STDP) is a conceptually simple and popular learning rule for silicon synapses [110], [141], [170], [171], [172], [173], [174]. STDP is a two-factor Hebbian learning rule relying on the relative timing of presynaptic and postsynaptic spikes occurring at times  $t_{\rm pre}$  and  $t_{\rm post}$ , respectively. STDP strengthens correlation in the presynaptic and postsynaptic activities by increasing (resp. decreasing) the synaptic weight for causal (resp. anti-causal) orderings between presynaptic and postsynaptic spikes. It follows an exponential shape shown as a blue line in Fig. 7(a). A phenomenological implementation is proposed by Cassidy et al. [175] for digital implementations and is shown in black in Fig. 7(a). The STDP learning rule has been declined in various shapes and has been formulated either based on spike times or on spike order (see [176] for a recent overview). Although a spike-order-based formulation allows reducing hardware requirements by eliminating the need for precise spike times [176], [177], it does not solve the main hardware efficiency issue of the STDP rule: its nonlocality in time. Indeed, computing spike time differences will always imply buffering overhead.

The spike-driven synaptic plasticity (SDSP) learning rule proposed by Brader et al. [178] led to several silicon implementations [76], [111], [112], [114], [179], [180], [181]. Instead of relying on relative presynaptic and postsynaptic spike timings, SDSP computes synaptic weight updates based on the internal state of the postsynaptic neuron at the time of the presynaptic spike, thereby leading to a learning rule that is local in both space and time. If the postsynaptic membrane voltage  $V_{\text{mem}}$  is above (resp. below) a given threshold  $\theta_m$ , the synaptic weight undergoes a step increase (resp. decrease) upon the arrival of a presynaptic spike [Fig. 7(b)]. Similar to STDP, SDSP strengthens the correlation between presynaptic and postsynaptic activities as the membrane potential indicates whether or not the postsynaptic neuron is about to spike. In order to improve the recognition of highly correlated patterns, Brader et al. [178] added a stop-learning mechanism based on the calcium concentration of the postsynaptic neuron. The calcium concentration provides an image of the recent postsynaptic firing activity: if it is beyond average ranges [thresholds  $\theta_1$ ,  $\theta_2$ , and  $\theta_3$  in Fig. 7(b)], there is evidence that learning already took place and that further potentiation or depression is likely to result in overfitting. The learning ability of SDSP is similar to that of STDP but presents better biophysical accuracy and generalization properties [178]. Both STDP and SDSP require careful hyperparameter tuning to achieve acceptable performance levels [111], [112], [182].

Overall, the specific learning rule and resolution selected for the design determines the synapse circuit size, the learning ability, and the memory lifetime of the network as a function of the number of new stimuli received (i.e., how long a learned pattern can be reliably retrieved as synaptic weights adapt, also known as the palimpsest property) [183]. A particularly important aspect for the choice of the spike-based learning rule is its impact on the memory architecture, which will in turn define how tightly memory and computation can be cointegrated (see Section II-C). In particular, current high-density integrations with on-chip synaptic weight storage usually rely on SRAM (see Section III-B). Indeed, standard single-port foundry SRAMs currently have densities as high as 0.120  $\mu$ m<sup>2</sup>/bit in 28-nm FDSOI CMOS [184] or 0.031  $\mu$ m<sup>2</sup>/bit in the recent Intel 10-nm FinFET node [185]. Foundry SRAMs are thus an efficient substrate for low-cost synapse array design, which suits well a time-multiplexed approach. However, the memory access patterns required by the considered learning rule might imply the use of custom SRAMs instead of single-port foundry SRAMs, thus automatically inducing design time and density penalties as the layout design rule checking (DRC) for logic must be used instead of the foundry bitcell pushed rules [186]. This is a known issue for spike-timingbased rules as their nonlocality in time implies complex memory access patterns (e.g., see [110], where a custom dual-port SRAM with both row and column accesses was designed), while SDSP-derived rules were shown to be compatible with single-port foundry SRAMs as they only rely on information available locally in both space and time [111], [112], [181].

However, purely local learning rules relying on local presynaptic and postsynaptic activities (i.e., two-factor rules) are unable to accommodate for dependence on higher order feedback: adding a third modulation factor is necessary to represent global information (output-prediction agreement, reward, surprise, novelty, or teaching signal) and to relate it to local input and output activities for synaptic credit assignment [187], thereby leading to three-factor rules. Just as the calcium concentration in SDSP corresponds to a third factor modulating the presynaptic and postsynaptic activities, several other third-factor learning rules have been proposed, including the Bienenstock–Cooper–Munro (BCM) model [188], the triplet-based STDP [189], and several other variants of STDP and SDSP, e.g., [190], [191], from

which the silicon synapse design introduced in [192] is inspired. Furthermore, as the global modulation signal may be delayed over second-long behavioral timescales, there is a need for synapses to maintain a memory of their past activity, which may be achieved through local synaptic eligibility traces [193]. While the computation of eligibility traces is already supported by some neuromorphic platforms with the help of von Neumann coprocessors [86], [89], [194], a time-multiplexed digital implementation was recently demonstrated in [195]. A fully parallel implementation was also proposed in [107] by exploiting the conductance drift nonideality of phase change memory (PCM) devices. This growing complexity in synaptic learning rules is closely related to dendritic computation (Section III-A3).

#### 3) Dendrites:

While the theory of synaptic plasticity focused first on point spiking neuron models (i.e., single-compartment neurons consisting only of the soma and the synapses, without dendrites, as defined in Fig. 4) and two-factor learning rules driven by the correlation between the presynaptic and postsynaptic spike timings, it now appears that STDP-based learning rules emerge as a special case of a more general plasticity framework [196], [197]. Although not fully characterized yet, several important milestones toward this general plasticity framework appear to involve dendritic functions. First, correlating presynaptic spikes with the postsynaptic membrane voltage and its low-passfiltered version, which could correspond to a local dendritic voltage, allows accommodating for most experimental effects that cannot be explained by STDP alone [198]. Second, the local dendritic potentials in multicompartment neuron models are shown to predict activity in the soma (i.e., predictive coding), with implications in supervised, unsupervised, and reinforcement learning setups [191]. Finally, combining a detailed dendritic model of a cortical pyramidal neuron with a single general plasticity rule strongly grounded on the biophysics (i.e., local lowpass-filtered voltage traces at the presynaptic and postsynaptic sites) could unify previous theoretical models and experimental findings [197]. Therefore, dendrites emerge as a key ingredient that allows generalizing STDP, providing neuron-specific feedback and potentially enabling error-based synaptic credit assignment in the brain. Furthermore, new top-down algorithms mapping onto dendritic primitives also give a strong incentive for neuromorphic hardware supporting dendritic processing (see Section IV-A). For these reasons, although only a few earlier works investigated the design of dendritic circuits [199], [200], [201], [202], silicon implementations of dendrites and multicompartment neuron models are now receiving an increasing interest [89], [203], [204], [205].

#### 4) Axons:

Neurons communicate spikes through their axon, which covers both short- and long-range connectivities. While the

neuron and synapse implementation can be analog, mixedsignal, or digital, the spike distribution infrastructure is always implemented digitally to allow for high-speed communication of spike events on shared bus resources with a minimized footprint [206]. The standard protocol for spike communication is the asynchronous address-event representation (AER) [207], [208], from simple point-to-point links in small-scale designs [76], [111], [114] to complex NoC infrastructures allowing for large-scale on- and offchip integration [71], [87], [88], [89], [90], [112], [209], [210]. While point-to-point links cannot scale efficiently as they require the use of dedicated external routers, large-scale infrastructures ensure that several chips can be interconnected directly through their on-chip routers. We refer the reader to [210] for a review on linear, mesh-, torus-, and tree-based router types.

Given constraints on the target network structure, such as the fact that biological neural networks typically follow a dense local and sparse long-range connectivity (i.e., small-world connectivity [211]), an efficient routing infrastructure must maximize the fan-in and fan-out connectivity while minimizing its memory footprint. Common techniques to optimize this tradeoff include a twoor three-level hierarchical combination of different router types (e.g., [90], [112], [210], and [212]) and of sourceand destination-based addressing. In the former, source neurons are agnostic of the implemented connectivity, and only the source neuron address is sent over the NoC. In exchange, this scheme requires routers to implement mapping tables and thus to have access to dedicated memory resources, which can be either off-chip [87], [210] or on-chip [90], [209] depending on the target tradeoff between efficiency and flexibility. On the other hand, in the latter, the source neuron sends a destination-encoded packet over the NoC. This allows for low-cost high-speed memory-less routers, at the expense of moving the connectivity memory overhead at the neuron level [88], [112]. These different hierarchical combinations of router types and of source- and destination-based addressing allow reaching different tradeoffs between scalability, flexibility, and efficiency, which will become apparent when quantitatively comparing experimentation platforms in Section III-B2.

#### **B.** Silicon Integration

Based on the neuron, synapse, dendrite, and axon building blocks described in Section III-A, small-to-large-scale integrations in silico have been achieved with a wide diversity of design styles and use cases. Here, we review these designs, first qualitatively to outline their applicative land-scape (Section III-B1) and then quantitatively to assess the key versatility/efficiency tradeoff that bottom-up designs aim at optimizing (Section III-B2). Finally, we highlight the challenges faced by a purely bottom-up design approach when efficient scaling to real-world tasks is required (Section III-B3).

Table 3 Bottom-Up Neuromorphic Experimentation Platforms Overview. (S) Denotes Small-Scale Chips Embedding Up to 512 Neurons. (M) Denotes Medium-Scale Chips Embedding 1k-to-2k Neurons With a Large-Scale Communication Infrastructure. (L) Denotes Large-Scale Chips or Systems, From 10k-to-100k Neurons (Single Chip/Wafer) to Millions of Neurons (Multichip Setups), With Up to a Billion Neurons for Supercomputer Setups

| Impl                   | ementation                  | Key designs‡                                                                                                                                                  | Main application                                                            |  |

|------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

|                        | Subthreshold                | ROLLS (S) [114]<br>DYNAPs (M) [90]<br>Neurogrid (L) [87]                                                                                                      | Brain emulation,<br>basic research and<br>edge computing (S-M)              |  |

| Analog<br>mixed-signal | Above-threshold             | HICANN (S) [71]<br>HICANN-X (S) [72]<br>BrainScaleS (L) [71]<br>(BrainScaleS 2) (L)* [214]                                                                    | Neuroscience<br>simulation<br>acceleration                                  |  |

|                        | Switched- or time-muxed-cap | Mayr et al. (S) [76]<br>IFAT (L) [98]                                                                                                                         | Bio-inspired edge to cognitive computing                                    |  |

|                        | Software-based <sup>†</sup> | GENESIS [223]<br>NEURON [224]<br>NEST [225]<br>Auryn [227]<br>EDEN [228]<br>Brian 1, 2 [226], [231]<br>ANNarchy [229]<br>GeNN [230]                           | Low-cost and<br>flexible neuro-<br>science simulation                       |  |

|                        | Distributed<br>von Neumann  | SpiNNaker (L) [86]<br>(SpiNNaker 2) (L)* [234]                                                                                                                | Neuroscience<br>simulation<br>acceleration                                  |  |

| Digital                | Full-custom                 | Seo et al. (S) [110]<br>ODIN (S) [111]<br>μBrain (S) [113]<br>MorphIC (M) [112]                                                                               | Bio-inspired edge computing                                                 |  |

|                        |                             | TrueNorth (L) [88]<br>Loihi (L) [89]                                                                                                                          | Cognitive computing                                                         |  |

|                        | FPGA-based                  | μCaspian (S) [237]<br>Minitaur (L) [238]<br>Cassidy et al. (L) [77]<br>Wang et al. (L) [239]<br>RANC (L) [240]<br>Luo et al. (L) [78]<br>Yang et al. (L) [80] | Low-cost, flexible<br>neuroscience<br>simulation and<br>cognitive computing |  |

<sup>&</sup>lt;sup>‡</sup> Not exhaustive. We refer the reader to [56] for a more extensive list.

1) Overview of Neuromorphic Experimentation Platforms:

Depending on their implementation and chosen circuit design styles, bottom-up neuromorphic experimentation platforms can be used as testbeds for neuroscience-oriented applications if they aim at replicating the biophysics, either through emulation or simulation of detailed models (see Section II). Small-scale systems can also support bioinspired edge computing applications, which will be further discussed in Section V. Finally, large-scale systems usually target high-level functional abstractions of neuroscience, i.e., cognitive computing. In the following, we review the applicative landscape of analog and mixed-signal designs, followed by digital ones. A qualitative overview is provided in Table 3.

#### a) Analog/mixed-signal designs:

The physics-based emulation approach based on subthreshold analog design is pursued in three main designs, which primarily target basic research and also allow for the exploration of edge computing use cases in small- to medium-scale designs. First, the 0.18- $\mu$ m ROLLS

chip [114] is a neurosynaptic core that embeds 256 AdExp neurons (Section III-A1), 64k synapses with STP, and 64k synapses with SDSP (Section III-A2). Second, the  $0.18-\mu m$ DYNAPs chip [90] is a quad-core 2k-neuron 64k-synapse scale-up of ROLLS whose focus is put on the spike routing and communication infrastructure, at the expense of synaptic plasticity, which has been removed. A 28-nm version of the DYNAPs chip has been designed, which includes a plastic core embedding 64 neurons and 8k 4-bit digital STDP synapses, with preliminary results reported in [213]. Finally, the Neurogrid, a 1-million-neuron system based on 16 0.18- $\mu$ m Neurocore chips, was designed in order to emulate the biophysics of cortical layers [87]. However, large-scale integration is achieved at the expense of synaptic weight storage, which has been moved offchip, thus inducing power and latency overheads. Importantly, by aiming at a direct reproduction of biophysical phenomena, these subthreshold analog designs mainly aim at understanding by building.

The model-based above-threshold analog design approach allows accelerating neuroscience simulations and is pursued in the BrainScaleS wafer-scale design. It relies on 0.18-μm HICANN chips with 512 AdExp neurons and 112k 4-bit STDP synapses integrated at a scale of 352 chips per wafer [71]. BrainScaleS thus embeds 180k neurons and 40M synapses per wafer for large-scale simulation and exploration of cortical functions, with acceleration factors ranging from 10<sup>3</sup> to 10<sup>5</sup> compared to biological time. The secondgeneration 65-nm HICANN-X chips [72] will be used for BrainScaleS 2, whose wafer-scale integration is still in development [214]. HICANN-X embeds 512 AdExp neurons, 128k 16-bit synapses, a programmable plasticity processor, as well as multicompartment neuron models for dendritic computation and structural plasticity [215], [216]. In contrast with subthreshold analog designs, the BrainScaleS platform aims at providing a tool for neuroscientists and thus follows a building-to-understand approach.

Approaches based on SC and capacitor-based time multiplexing have been proposed in [76] and [98]. The 28-nm chip from Mayr et al. [76] is an interesting attempt at leveraging technology scaling by using digital control and SRAM-based weight storage while maintaining the higher biophysical accuracy of analog designs for synaptic plasticity through SC circuits. Capacitor-based time multiplexing is used for neuron membrane potential storage. This small-scale chip embeds 64 neurons and 8k 4-bit synapses with both STP and SDSP, as per the implementation described in [217]. It is thus suitable for near-sensor applications at the edge, where the power and area footprints should be minimized [32], [33]. The 65-nm integrate-andfire array transceiver (IFAT) chip from Park et al. [98] relies on conductance-based neuron and synapse models with capacitor-based time multiplexing, embedding as high as 65k two-compartment I&F neurons per chip. However, synapses do not embed synaptic plasticity and their

<sup>\*</sup> The second-generation BrainScaleS and SpiNNaker large-scale systems are currently in development. For SpiNNaker 2, only proof-of-concept prototype chips have been reported so far, which embed 4 ARM cores out of the 152 planned. For BrainScales 2, the main chip HICANN-X is already available while the wafer-scale integration is currently in development.

<sup>†</sup> Software-based approaches run on CPU and/or GPU hardware. The implementation scale depends on available resources and the granularity of the biophysical modeling.

weights are stored off-chip. This chip is thus appropriate for large-scale cognitive computing experiments with relaxed synaptic requirements.

Finally, solutions based on nonvolatile memory and emerging devices have been proposed. As mentioned in Section II-C, cointegration of memristors with CMOS is still at an early stage. A first proof-of-concept chip has recently been proposed in [218], though only demonstrated for very small problems (e.g., classification of 5×5pixel binary patterns). It embeds 5k memristor synapses at a density of 10  $\mu$ m<sup>2</sup> per synapse, which is an order of magnitude larger than state-of-the-art digital integrations. Successful implementations based on resistive memory devices were later reported with 256-neuron 64k-synapse cores in 0.15- [219] and 0.13- $\mu$ m [220] technology nodes at a density of 1.6  $\mu$ m<sup>2</sup> per synapse. Although promising, significant work is still required to alleviate the aspects of synaptic resolution control, mismatch, and fabrication costs toward large-scale memristor-based neuromorphic systems. However, progress in this direction is likely to benefit from the recent release of open-source process design kits (PDKs) that include resistive memory devices [221]. As an alternative with more mature technologies, a  $0.35-\mu m$ flash-based STDP design has also been proposed in [222], but embedded flash memory is difficult to scale beyond 28nm CMOS and requires high programming voltages.

#### b) Digital designs:

While neuromorphic engineering aims at a paradigm shift from von-Neumann-based architectures to distributed ones that colocate processing and memory, the granularity at which this paradigm shift is achieved in digital implementations strongly varies between three main approaches: software-based, distributed von Neumann, or full-custom, from high to low processing and memory separation.

Software-based approaches run on conventional von Neumann hardware. Dedicated SNN simulators, such as GENESIS [223], NEURON [224], NEST [225], Brian [226], Auryn [227], and EDEN [228], allow running experiments on conventional CPUs, while simulators, such as ANNarchy [229], GeNN [230], and Brian 2 [231], provide GPU support. Software-based approaches provide the highest flexibility and control over the neuron and synapse models and the scale of the experiments. However, using von Neumann hardware to simulate SNNs comes at the cost of power and simulation time overheads, although recent work has demonstrated that GPUs can compare favorably to a SpiNNaker-based system for cortical-scale simulations [232], [233].

SpiNNaker follows a distributed von Neumann approach. It was fabricated in a 0.13- $\mu$ m CMOS technology and embeds 18 ARM968 cores per chip in a globally asynchronous locally synchronous (GALS) design for efficient handling of asynchronous spike data, spanning biological to accelerated time constants [86]. SpiNNaker has been optimized for large-scale SNN experiments while keeping a high degree of flexibility, with the

current supercomputer-scale setup reaching the billion of neurons, i.e., about 1% of the human brain [115]. The second-generation SpiNNaker system is in development. Current 28-nm prototype chips embed four ARM Cortex M4F cores out of the 152 per chip planned for the final 22-nm SpiNNaker 2 system [234]. The objective is to simulate two orders of magnitude more neurons per chip compared to the first-generation SpiNNaker: when integrated at supercomputer scale, real-time simulations at the scale of the human brain will be within reach [235]. Therefore, similar to BrainScaleS, SpiNNaker also follows a building-to-understand approach.

Full-custom digital hardware allows for high-density and energy-efficient neuron and synapse integrations, due to memory being moved closer to computation compared to the two abovementioned digital approaches. As full-custom digital designs rely on SRAM-based time multiplexing, this can be related to the efficiency improvement brought by caches in conventional von Neumann processors [236]. Full-custom designs can usually be configured to span biological to accelerated time constants. The 45-nm small-scale design by Seo et al. [110] embeds 256 LIF neurons and 64k binary synapses based on a stochastic version of STDP (S-STDP). It achieves high neuron and synapse densities compared to mixedsignal designs, despite the use of a custom SRAM (Section III-A2). Its scale thus makes it ideal for edge computing. In line with this small-scale edge computing use case, the ODIN chip embeds 256 neurons with the 20 Izhikevich behaviors and 64k SDSP-based 4-bit synapses in 28-nm CMOS [111]. The 65-nm MorphIC chip scales up the neurosynaptic core of ODIN in a quad-core design allowing for large-scale multichip setups with a total of 2k LIF neurons and more than 2M binary synapses with stochastic SDSP (S-SDSP) per chip [112]. Being based on SDSP, ODIN and MorphIC can leverage the density advantage of standard single-port foundry SRAMs to achieve record neuron and synapse densities (Section III-A2). One notable exception to the SRAM-based time-multiplexed approaches in the digital domain is  $\mu$ Brain [113], which implements a recurrent 256-64-16 LIF-based network in a fully parallel fashion with distributed flip-flop-based memories. Combined with asynchronous event-driven processing,  $\mu$ Brain tackles the von Neumann bottleneck at the highest granularity, at the expense of an increase in static power and silicon area (Table 2), as well as the introduction of a technology-specific delay element. Finally, cognitive computing applications require large-scale platforms, which is currently offered by the 28-nm IBM TrueNorth [88] and the 14-nm Intel Loihi [89] neuromorphic chips. On the one hand, TrueNorth is a GALS design embedding as high as 1M neurons and 256M binary nonplastic synapses per chip, where neurons rely on a custom model exhibiting 11 Izhikevich behaviors, or 20 behaviors if three neurons are combined [154]. On the other hand, Loihi is a fully asynchronous design embedding up to 180k neurons and 114k (9-bit) to 1M (binary) synapses per chip. Neurons rely on an LIF model with a configurable number of compartments to which several functionalities, such as axonal and refractory delays, spike latency, and threshold adaptation, have been added. The spike-based plasticity rule used for synapses is programmable and eligibility traces are supported.