# Design of High-frequency Fast-rise Pulse Modulators for Lifetime Testing of Dielectrics

Mathew, P.; Niasar, M. G.; Vaessen, P.

10.1109/TDEI.2023.3296711

**Publication date**

**Document Version** Final published version

Published in

IEEE Transactions on Dielectrics and Electrical Insulation

Citation (APA)

Mathew, P., Niasar, M. G., & Vaessen, P. (2023). Design of High-frequency Fast-rise Pulse Modulators for Lifetime Testing of Dielectrics. IEEE Transactions on Dielectrics and Electrical Insulation, 30(6), 2798-2808. https://doi.org/10.1109/TDEI.2023.3296711

# Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Design of High-Frequency Fast-Rise Pulse Modulators for Lifetime Testing of Dielectrics

Philip Mathew<sup>®</sup>, *Graduate Student Member, IEEE*, Mohamad Ghaffarian Niasar<sup>®</sup>, and Peter Vaessen. *Member, IEEE*

Abstract - Penetration of power electronics in the grid has produced a new species of stresses, characterized by fast-rising pulsed waveforms with microsecond rise times repeating at several tens of kilohertz. Analyzing their impact on existing and future insulation systems requires pulse modulators, most often with pulse transformers (PTs), to perform aging and breakdown tests. PT design for klystron loads has been studied extensively albeit for either low repetition rates or short pulse durations. However, capacitive dielectric loads impose additional complex constraints on optimizing leakage ( $L_{\sigma}$ ) and parasitic capacitance  $(C_d)$  in order to minimize rise time  $(T_r)$  and overshoot  $(V_{pk})$ . Ensuring consistent output pulse shape is crucial since breakdown is sensitive to voltage magnitude. This article discusses these challenges through the design procedure of a modulator prototype capable of producing bipolar pulses up to 14 kV with rise times  $< 2 \mu s$ at frequencies between 10 and 50 kHz. Major challenges, especially core selection, winding design, PT parasitic optimization, breakdown detection, and failure modes, are highlighted. A new PQR equation is derived to model modulators with capacitive loads. Finally, the output pulses are applied across oil-impregnated paper samples to generate statistics on insulation breakdown strength and lifetime at 10 and 50 kHz. Results illustrate a reduction in lifetime and breakdown strength at 50 kHz. This is possibly due to the nonhomogenous distribution of dielectric losses within the oil-paper leading to local hotspots and eventual thermal breakdown. Furthermore, a critical field  $F_c = 21 \text{ kV/mm}$  is found below which the slope of the lifeline decreases dramatically, thereby indicating a shift in the aging mechanism. Potential reasons for this phenomenon are also discussed.

Index Terms—Dielectric aging, distributed capacitance, high power, leakage flux, mixed-frequency, oil-paper, pulse modulator, pulsed power, pulse transformer (PT), solid-state transformer (SST), transformer parasitics.

Manuscript received 4 February 2023; revised 22 May 2023 and 24 June 2023; accepted 11 July 2023. Date of publication 18 July 2023; date of current version 29 December 2023. This work was supported by the Dutch TKI Urban Energy Program. (Corresponding author: Philip Mathew.)

Philip Mathew was with the High Voltage Technologies Group, TU Delft, 2628 Delft, The Netherlands. He is now with Hitachi Energy HVDC, 771 80 Ludvika, Sweden (e-mail: joemat007@gmail.com).

Mohamad Ghaffarian Niasar is with the Electrical Sustainable Energy Department, High Voltage Technologies Group, TU Delft, 2628 Delft, The Netherlands (e-mail: m.ghaffarianniasar@tudelft.nl).

Peter Vaessen is with the High Voltage Technologies Group, TU Delft, 2628 Delft, The Netherlands, and also with KEMA Laboratories, 6812 Arnhem, The Netherlands (e-mail: p.t.m.vaessen@tudelft.nl).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TDEI.2023.3296711.

Digital Object Identifier 10.1109/TDEI.2023.3296711

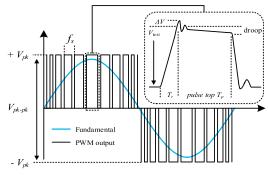

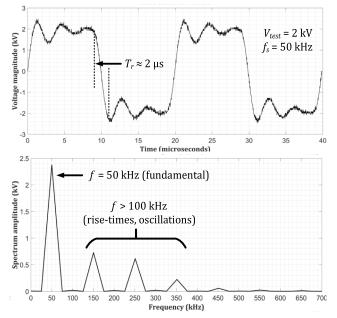

Fig. 1. Typical pulsewidth modulated output of a two-level inverter.

### I. INTRODUCTION

THE ongoing energy transition toward a greener future is facilitated by widespread application of power electronics in the grid. Increased expertise in high power and the introduction of silicon carbide has catalyzed key technologies such as solid-state transformers (SSTs). SSTs are expected to play a vital role in future power systems by offering large energy densities and flexible power flow [1] although at the cost of severe mixed frequency pulsed stresses experienced by the dielectric insulation of their inverter-fed medium frequency transformers (MFTs) [2]. These stresses are characterized by fast-rising pulsed waveforms, as shown in Fig. 1.

In contrast to pure sinusoids, the aging of dielectrics under pulsed stresses is still under investigation. The influence of such waveforms was first observed in an increase of stator winding failures during the widespread application of variable speed drives for motors in the 1980s [3], [4], [5], [6], [7], [8]. Kaufhold et al. [5] showed that time-to-failure can be predicted by an  $n_b$  number of partial discharges (PDs). Yin [6] attributed insulation failure to a combinatory effect of PD, dielectric heating, and space charge formation. Her work demonstrated that the frequency dependence of insulation lifetime differs under either pulsed or sinuous stress [7]. Montanari et al. [8] separated aging mechanisms above and below the PD inception voltage (PDIV). Cavallini et al. [9] identified pulse magnitude as the dominating aging factor apart from frequency, rise time, polarity, and duty cycle. More recent works by Wang et al. [10] studied PD characteristics under square waveforms and assessed the impact of rise time [11], frequency [12], and duty cycle [13] on aging. Koltunowicz et al. [14], [15] also studied the impact of frequency on oil-impregnated paper insulation (OIP).

TABLE I

TYPICAL PARAMETER RANGES OF INVERTER WAVEFORMS

| Parameter            | Symbol         | Typical range |

|----------------------|----------------|---------------|

| Peak-to-peak voltage | $V_{pk-pk}$    | 500 V – 20 kV |

| Switching frequency  | f <sub>s</sub> | 5 Hz – 50 kHz |

| Pulse rise time      | $T_r$          | 100 ns – 4 μs |

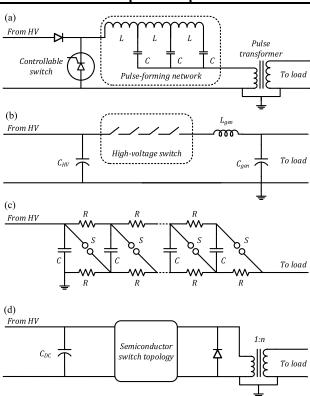

Fig. 2. Popular modulator topologies. (a) Line-type modulator. (b) Series HV-switch. (c) Marx generator. (d) LV-switch with PT.

However, despite extensive literature, lifetime statistics under pulsed waveforms are not available above a few kilohertz. Since MFT insulations experience pulses up to 50 kHz, filling this research gap forms the first core motivation of this article.

Analyzing the impact of pulsed waveforms requires pulse modulators to produce quick quasi-rectangular voltages across dielectric samples. An important modulator component is the pulse transformer (PT), the design of which has been studied in-depth such as in klystrons [16], [17], [18], treating air pollution [19], and cancer radiation therapy [20], [21]. However, the capacitive nature of dielectrics needs significantly more complex PT design criteria for lifetime tests. The derivation and description of these criteria form the second core motivation of this article.

Typical values of pulse waveform parameters for two-level SST inverters compiled from [22] and [23] are summarized in Table I. Four popular modulator choices are shown in Fig. 2. Line type is not picked due to limited pulse shaping [24]. The Marx generator is limited in repetition rate and requires many stages decreasing reliability [25], [26]. Series HV switches are suitable and have been used extensively for dielectric tests in the literature [27], [28]. However this topology requires:

- 1) a high-voltage dc source which can be quite expensive;

- 2) high-voltage switches that can be expensive to procure;

TABLE II

COMPARISON OF MODULATOR TOPOLOGIES

| Topology         | Advantage          | Disadvantage                          |

|------------------|--------------------|---------------------------------------|

| Line-type        | Relatively compact | Limited shape control                 |

| Series HV-switch | Simple design      | ↑ Cost (source, switch)               |

| Marx generator   | Sourced at LV      | ↑ N <sub>stages</sub> = ↓ reliability |

| LV-switch + PT   | Flexible control   | Transformer parasitics                |

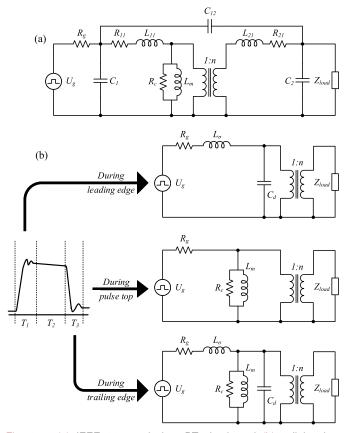

Fig. 3. (a) IEEE 390 equivalent PT circuit and (b) splitting into three separate circuits for modeling characteristics during each pulse duration.

3) series inductance to limit current after dielectric breakdown.

Considering the points mentioned in Table II, the LV-switch with PT topology was finally selected. This setup can be sourced at 230 V, implemented with inexpensive switches, produces both unipolar/bipolar pulses, and also has a short-circuit limitation from the inductance of the PT.

# II. MODULATOR MODEL

Due to their diverse application set, pulse modulators have been modeled extensively to predict the output waveform at a certain operating point. The standard IEEE 390 model [29] is shown in Fig. 3(a) with the following elements:

- 1) ideal transformer of ratio n;

- 2) ideal pulse generator  $U_g$ ;

- 3) output load impedance  $Z_{load}$ ;

- 4) winding resistances  $R_{11}$ – $R_{21}$ ;

- 5) leakage inductances  $L_{11}$ – $L_{21}$ ;

Fig. 4. Equivalent PT circuit with (a) resistive and (b) capacitive loads.

- 6) distributed winding self-capacitances  $C_1$ – $C_2$ ;

- 7) interwinding capacitance  $C_{12}$ ;

- 8) core-loss resistance  $R_c$  and magnetizing inductance  $L_m$ .

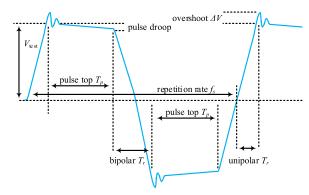

In the time domain, a pulse can be divided into three unique portions, i.e., leading edge T1, pulse top T2, and trailing edge T3. The dynamics during these durations can be studied separately as shown in Fig. 3(b) (remains applicable to the nanosecond scale [16]). In T1, shunt  $R_c$  and  $L_m$  are removed due to negligible core excitation in short rise times. In T2, series  $L_\sigma$  and shunt  $C_d$  is neglected since only low-frequency components are present. Parameters of interest are rise time  $(T_r)$  and overshoot  $(\Delta V)$  in T1 and pulse droop in T2. Since tests will be performed with bipolar pulses, T3 parameters, such as settling time will have no impact on the output. In Section II-A, a relation from  $T_r$  and  $\Delta V$  to PT parasitics  $L_\sigma$  and  $C_d$  is derived for resistive and capacitive loads.

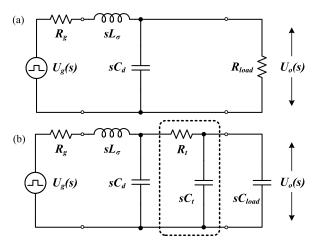

### A. For Resistive Loads

The equations for resistive-load PTs, as shown in Fig. 4(a), were first derived by Glasoe and Bostick [30] of the MIT Radiation Laboratory in 1948. This combined with [16] linked the transformer leakage flux  $L_{\sigma}$  and parasitic capacitance  $C_d$  with the parameters rise time  $T_r$  and peak overshoot  $\Delta V$  as

$$2R_{\text{load}} \cdot \sigma = \sqrt{\frac{L_{\sigma}}{C_d}} \tag{1}$$

$$T_r = 2\pi \cdot T_{10\%-90\%} \sqrt{L_\sigma C_d}$$

(2)

where  $\sigma$  is the damping coefficient and  $T_{10\%-90\%}$  is the time taken for voltage magnitude to rise from 10% to 90%. The key observation was that rise time reduction requires minimizing parasitic product  $L_{\sigma}C_d$  while peak overshoot reduction requires minimizing parasitic ratio  $(L_{\sigma}/C_d)$  causing a resulting in an inherent trade-off requiring compromise. Bortis et al. [16] showed the product depends on physical design, while the ratio depends on the choice of transformer interconnections.

### B. For Capacitive Loads

Unlike the above equations, pulse modulators for dielectric testing will instead see a load insulation sample modeled as a

capacitance. However, this  $C_{\rm load}$  would be added to parasitic  $C_d$  causing zero damping (high overshoots) and longer rise times

$$\sigma \propto \frac{1}{R_{\text{load}}} \sqrt{\frac{L_{\sigma}}{(C_d + C_{\text{load}})}} \xrightarrow{R=0} 0$$

(3)

$$T_r \propto \sqrt{L_\sigma (C_d + C_{\text{load}})}.$$

(4)

A possible solution is to add in this article is to add test elements  $R_t$  and  $C_t$ , as shown in Fig. 4(b). The inclusion of  $R_t$  decouples transformer-load dynamics, while the  $R_tC_t$  combination filters the output pulse waveform with a cutoff frequency:

$$F_c = \frac{1}{2\pi \cdot R_t C_t}. ag{5}$$

Since  $C_{\text{load}}$  depends on both electrode arrangement and insulation sample thickness and permittivity, this pulse tuning capability is necessary in order to ensure consistent waveform shape throughout all tests, considering that breakdown is most sensitive to peak voltage. Furthermore,  $R_t$  limits steady-state short-circuit current through the modulator after dielectric breakdown occurs, while the transformer inductance slows down the dynamic current-rise providing a sufficient time window to disconnect the modulator from the load. The addition of  $R_t$  and  $C_t$  thus results in a third-order circuit. After simplifications, the output voltage can be expressed as

$$U_o(s) = \frac{U_g}{sL_\sigma C_d R_t C_{eq}} \times \frac{1 + sR_t C_{eq}}{s^3 + s^2 \left(\frac{1}{R_t C_{eq}} + \frac{1}{R_t C_d}\right) + s\left(\frac{1}{L_\sigma C_d}\right) + \left(\frac{1}{L_\sigma C_d R_t C_{eq}}\right)}.$$

(6)

Setting  $C_{\rm eq} = C_t + C_{\rm load}$  and  $R_g \approx 0$ , the equation becomes:

$$U_o(s) = \frac{U_g}{s} \times PQ \times \frac{1}{s^3 + s^2R + sP + PQ}$$

(7)

$$P = \frac{1}{L_{\sigma}C_d}$$

$Q = \frac{1}{R_tC_{eq}}$   $R = \frac{1}{R_t} \left(\frac{1}{C_{eq}} + \frac{1}{C_d}\right)$  (8)

where parasitics parameter (P) represents transformer dynamics, quality parameter (Q) represents the dynamics of the  $R_tC_{eq}$  filter, and relational parameter (R) represents the coupling between P and Q.

This PQR (7) can be solved for  $u_o(t)$  with varied values of  $L_\sigma C_d R_t C_t$  from a default  $L_\sigma = 250~\mu\text{H}$ ,  $C_d = 200~\text{pF}$ ,  $R_t = 10~\text{k}\Omega$ ,  $C_t = 60~\text{pF}$ , and  $C_{\text{load}} = 50~\text{pF}$  to illustrate the impact of each element.

From Fig. 5(a), achieving faster rise times and lower overshoots clearly requires minimization in transformer parasitics. However, it also shows that even unrealistically low values of  $L_{\sigma}C_d$  produce an atmost critically damped response, further demonstrating the limitations when designing transformers for capacitive loads.

On the other hand, the advantageous effect of  $R_tC_t$  is shown in Fig. 5(b) where an increase of either results in lower cutoff frequency and lower overshoot. It is thus vital to have these test elements for tuning output pulse shape for dielectric tests with different electrode arrangements and insulation permittivities.

Fig. 5. Effect of (a) parasitics and (b) test elements on output.

TABLE III

DESIRED PULSE MODULATOR SPECIFICATIONS (SEE FIG. 7)

| Parameter               | Symbol         | Usual range                             |

|-------------------------|----------------|-----------------------------------------|

| DC link voltage         | Vin            | 230 V                                   |

| Maximum test voltage    | $V_{test}$     | $14 \text{ kV}_{\text{pk-pk}}$          |

| Transformer turns ratio | n              | 1:50                                    |

| Pulse repetition rate   | f <sub>s</sub> | 10 – 50 kHz                             |

| Pulse overshoot         | ΔV             | < 1 % V <sub>test</sub>                 |

| Pulse rise (0-100%)     | $T_r$          | < 20 % (2f <sub>s</sub> ) <sup>-1</sup> |

| Load capacitance        | $C_{load}$     | 30 pF                                   |

# III. MODULATOR PROTOTYPE

This section describes the design of a modulator with desired specifications in Table III. Input is 230 V fed from ac mains. An output of 14 kV<sub>pk-pk</sub> is required for testing samples. Load capacitance  $C_{load} = 30$  pF is calculated for a single-layer OIP sample of thickness 150  $\mu$ m and an electrode diameter of 2.54 mm. The turns ratio of n = 50was chosen to reduce primary turns. Pulse frequency should be variable from 10 to 50 kHz for studying the impact of frequency on dielectric lifetime. Minimal overshoot is imperative since sample breakdown is mostly sensitive to peak voltage magnitude. The modulator should be capable of producing sustained pulses over several hours for lifetime tests without any waveform change. There should exist a reliable method for applying a 1 kV/s ramp rise during breakdown tests. Finally, the modulator should disconnect within a short time frame to reduce electrode breakdown marks.

Unlike sine-wave transformers, PTs transmit a bandwidth of frequencies [ $f_{lower}$ ,  $f_{upper}$ ]. The frequency spectrum of a sample 50 kHz pulse is analyzed in Fig. 6. The  $f_{lower}$  is limited

Fig. 6. Fourier analysis of sample 2-kV 50-kHz pulse.

Fig. 7. Definitions of bipolar pulse waveform parameters.

TABLE IV

N87 MNZN TDK MAGNETIC CORE PARAMETERS

| Parameter               | Symbol           | Usual range         |

|-------------------------|------------------|---------------------|

| Saturation flux at 25°C | B <sub>sat</sub> | 500 mT              |

| Cross-sectional area    | $A_e$            | 840 mm <sup>2</sup> |

by the core saturation criteria, while  $f_{\rm upper}$  limited by  $L_{\sigma}$  and  $C_d$  winding parasitics. The fundamental dominates, but there also exists a significantly higher frequency content in the range of several hundreds of kilohertz corresponding to rise times. The pulse waveform parameters are defined, as shown in Fig. 7.

### A. Magnetic Core

The magnetic core tightly bundles the flux lines within itself, increases magnetic field density, and improves linking between the windings. Commonly used materials include iron-based alloys (high  $B_{\rm sat}$  but high losses) and soft ferrites (low  $B_{\rm sat}$  but low losses). The unipolar PT in [6] used an amorphous iron-based magnetic alloy from Metglas USA with a  $B_{\rm sat}=1.6$  T. However, such cores are expensive and highly lossy for faster sustained repetition rates. Instead, an N87 MnZn ferrite

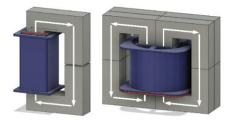

Fig. 8. Comparison of two-core (left) and eight-core (right) geometries.

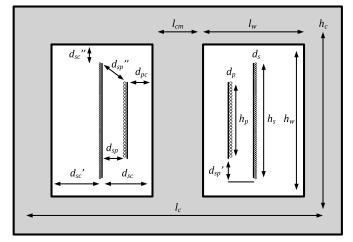

Fig. 9. Geometrical parameters of PT design (not to scale).

U-core from TDK was selected with specifications detailed in Table IV. This selection of a ferrite core now imposes limitations on the saturation prevention criteria. The maximum flux swing ( $\Delta B = 2B_{\rm max}$ ) under a bipolar excitation depends on the volt-per-turn ( $V_{\rm max}/n_1$ ), and the pulse duration  $T_p$  and core cross section are expressed as

$$B_{\text{max}} = \frac{V_{\text{max}} \cdot T_p}{2 \cdot n_1 \cdot A_e}.$$

(9)

An operating  $B_{\rm max}=400$  mT was selected considering the increase in temperature (decrease in  $B_{\rm sat}$ ) due to core losses. The required primary to prevent core saturation at 10 kHz is

$$\Rightarrow n_1^{\rm min} = \frac{230 \text{ V} \cdot 50 \text{ } \mu\text{s}}{2 \cdot 400 \text{ mT} \cdot 840 \text{ mm}^2} \approx 17 \text{ turns}.$$

However, this would lead to drastically high  $L_{\sigma}$  values, high overshoots, and slow rise times. To reduce the  $L_{\sigma}$  Klystron modulators commonly have a single turn primary  $(n_p = 1)$  to reduce the leakage flux, but this is only possible when producing pulses of short duration  $\approx 5~\mu s$  [16] or at low repetition rates [31], [32]. An eight-core structure (Fig. 8) is used instead for a fourfold increase in cross section, thereby reducing the criteria to  $n_p = 4$  This design also reduces the effective reluctance improving magnetic linkage.

### B. Winding Design

Designing an optimal winding involves balancing sufficient clearances (which cause flashovers) and transformer parasitics (which affect pulse performance). These tradeoffs are further strained due to the limited window size of the chosen N87 core. The geometrical parameters of the PT design are shown in Fig. 9.

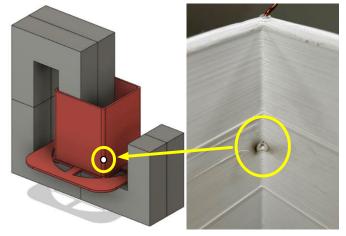

Fig. 10. Flashover at  $V_{\text{test}} = 17 \text{ kV}_{\text{pk-pk}}$  between the highest potential of HV to LV winding due to an insufficient  $d_{\text{sp}}''$  isolation distance.

Fig. 11. Structure damage due to repeated LV-core discharges.

1) Primary Winding Parameters: Foil windings are ideal for reducing leakage  $(h_p = h_s)$ , but their construction can be quite difficult for  $n_p > 1$ . Enameled wire can be used instead despite a relatively larger leakage. This  $L_{\sigma}$  can then be reduced by spreading the turns across  $h_p$ , but this also reduces  $d_{\rm sp}''$  isolation leading to severe HV–LV flashovers, as shown in Fig. 10. As a tradeoff, silicon insulated (thickness 3 mm) wire was selected.

Winding currents of the PT can be calculated as:

$$I_s = 4 \cdot \frac{C_{\text{load}} \cdot V_{\text{test}}}{T_r} = 4 \cdot \frac{30 \text{ pF} \cdot 7 \text{ kV}_{\text{pk}}}{4 \mu \text{s}} \approx 210 \text{ mA} \quad (10)$$

$$I_p = n \cdot I_s = 50 \cdot 210 \text{ mA} \approx 10.5 \text{ A}$$

(11)

hence,  $d_p = 2$  mm is selected for a 3-A/mm<sup>2</sup> current density. The final measured height of the primary winding is  $h_p = 35$  mm and  $d_{\rm pc} = 3$  mm is now the thickness of the wire silicon insulation. Secondary energization induces a potential onto the core causing LV-core discharges leading to damages on the LV structure, as shown in Fig. 11. This potential was estimated with finite element analysis (FEA) and measured with an electrostatic voltmeter to be 0.3 times the  $V_{\rm test}$  magnitude. The core is thus grounded and  $d_{\rm pc}$  is kept as short as possible to provide flexibility for other tradeoffs.

Improper grounding can cause discharges between core pieces, only diagnosed with auditory feedback. Each core interface was then coated with a 1:1 (catalyst:base) paste mixture of TFC Silicone Rubber Type 3 and conductive carbon

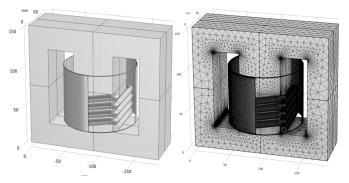

Fig. 12. Three-dimensional FEA model and mesh of prototype PT.

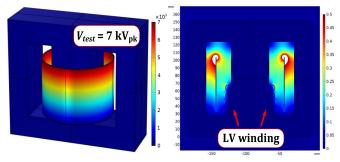

Fig. 13. HV potential distribution (left: 0–7 kV<sub>pk</sub>) and *E*-field magnitudes inside PT window from FEA (right: 0–0.5 kV/mm).

black. Larger paste volumes can decrease inductance and cause pulse droop.

2) Secondary Winding Parameters: An enamled wire of  $d_s = 0.35$  mm is selected to construct a 200-turn secondary HV winding of height  $h_s = 70$  mm. This is made in a single layer so as to reduce  $C_d$  parasitic. The transformer is 3-D modeled for FEA, as shown in Fig. 12. Secondary voltage  $V_{\text{test}}$  is implemented as a gradient along the HV winding length.

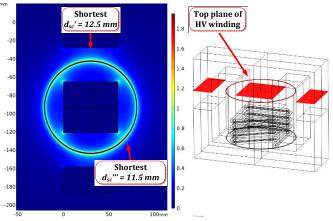

The vertical position of the primary winding  $(d'_{sp})$  influences the HV-LV field stresses and is hence set to 0 mm to limit the average field strength to 500 V/mm, as shown in Fig. 13. The largest possible vertical clearance between the highest potential of the HV winding to the grounded core is  $d_{\rm sc}'' = 20$  mm for this core. It can be seen in Fig. 13 that the highest field stresses occur at the top of the HV winding. This can be studied with an xy 2-D cut plane slicing the transformer model, as shown in Fig. 14. The curvature of the secondary results in two critical points, i.e., at  $d'_{sc}$  inside the transformer and at an external distance  $d_{\rm sc}^{\prime\prime\prime}$  (Fig. 14). Since an increase in either of these clearances reduces the other, an optimal balance is found at  $d'_{sc} = 12.5$  mm and  $d'''_{sc} = 11.5$  mm through FEA. The average field strength in this area also satisfies the 500-V/mm limit. The peak stresses here are improved by applying insulating grease on the winding. It should also be noted that liquids are unsuitable as an alternative medium due to nonunity permittivities ( $\varepsilon_r \neq 1$ ) multiplying with  $C_d$  parasitic. SF<sub>6</sub> can offer desirable properties but is not considered due to negative environmental impact, and highpressure gases will require expensive gas-tight enclosures.

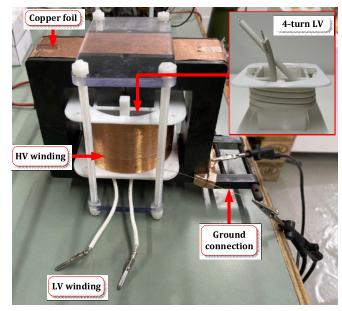

*3) Parasitic Evaluation:* The final prototype is shown in Fig. 15 and summarised in Table V. The silicon-insulated LV is contained inside the HV, both of which were designed in CAD and 3-D printed in polylactic acid (PLA). The core is

Fig. 14. Obtained *E*-field magnitudes (left: 0–1.9 kV/mm) and studied 2-D *xy* cut plane at the top of HV winding (right: red).

Fig. 15. Final PT prototype (note that LV is shown inverted here).

TABLE V

SUMMARY OF FINAL PT GEOMETRY VALUES (REFER FIG. 9)

| Primary LV                      | Secondary HV                  | Core                           |

|---------------------------------|-------------------------------|--------------------------------|

| $n_p$ = 4 turns                 | n <sub>s</sub> = 200 turns    | N <sub>c</sub> = 8 core pieces |

| $d_p$ = 2 mm stranded           | $d_s$ = 0.35 mm solid         | $h_c = 152 \text{ mm}$         |

| $h_p = 35 \text{ mm}$           | $h_s = 70 \text{ mm}$         | $I_c = 186 \text{ mm}$         |

| $d_{pc}$ = 3 mm                 | $d_{sc}$ = 22.5 mm            | <i>I<sub>cm</sub></i> = 20 mm  |

| $d_{sp} = 10 \text{ mm}$        | $d_{\rm sc}$ ' = 12.5 mm      | $h_w = 96 \text{ mm}$          |

| $d_{sp}$ ' = 0 mm               | d <sub>sc</sub> " = 20 mm     | $I_w = 37 \text{ mm}$          |

| <i>d<sub>sp</sub></i> " = 45 mm | d <sub>sc</sub> ''' = 11.5 mm | $A_e = 3360 \text{ mm}^2$      |

uniformly grounded and held together in a plexiglass frame. Measured PT parasitics are  $L_{\sigma}=730~\mu\text{H}$  and  $C_{d}=25~\text{pF}$ .

### C. Variable Test Elements

Test elements include a series  $R_t$  and a parallel  $C_t$ , which can tune output pulse shape and ensure consistency across tests.

$R_t$  is implemented as a bank of three series sets of five parallel high-power resistors, as shown in Fig. 16. Since

Fig. 16. Left: resistance bank  $(R_t)$  Right: HV disk capacitor  $(C_t)$ .

Fig. 17. Pulse shape (green) deformation above  $R_{t \text{ max}} = 20 \text{ k}\Omega$ .

Fig. 18. Pulse shape without (left) and with (right)  $R_t$   $C_t$  elements.

values above  $R_{t_{\rm max}} = 20~{\rm k}\Omega$  overdamp the output pulse as shown in Fig. 17, hence,  $R_t = 17.75~{\rm k}\Omega$  is implemented with combinations of 20 and 50 k $\Omega$ . This reduces the power dissipation per resistor ensuring stable temperatures (and resistance) during long aging tests.

$C_t$  is implemented as a high-voltage capacitor connected in parallel to the test sample, as shown in Fig. 16. The disk diameter is 20 cm and the distance between disks (d) can be altered with a rotational handle. Smaller d increases  $C_t$  and, thereby, the pulse damping, which is important since  $R_t$  alone cannot be used to tune output wave shape ( $R_{t\_max}$  criterion). Typical  $C_t$  magnitudes between tests at 10–50 kHz ranged between 50 and 150 pF.

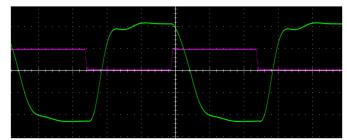

The impact of tuning  $R_t$   $C_t$  on the pulse shape is shown in Fig. 18.

### D. Breakdown Detection

In the event of insulation breakdown, the modulator must automatically disconnect the supply in a few milliseconds. In the absence of this function, a conducting arc will gradually burn the oil-paper sample and cause electrode deformation (Fig. 19). To prevent this, an analog circuit was designed in the ESE Laboratory, TU Delft, to detect dielectric breakdown. Since (dV/dt) of output waveform is high, it cannot be used as a trigger parameter. Instead, the detector is connected in series to and measures overcurrent through the test sample. Furthermore, the current flowing through the capacitive sample increases for higher frequencies, requiring adjustment of overcurrent threshold for breakdown detection.

Fig. 19. Electrode breakdown marks requiring sand polishing.

Fig. 20. Effect of sensitivity frequency on breakdown mark.

If the detector is made oversensitive, it would disconnect before dielectric breakdown, statistically neglecting healthy samples. If undersensitive, breakdown arcs are longer leading to carbonization and electrode deformation. Few reference test samples were checked after breakdown under an Olympus SZH-ILLD microscope. The effect of pulse frequency and detection sensitivity is shown in Fig. 20. The burn mark was observed to be sharper at 50 kHz than at 10 kHz.

# E. Prototype Summary

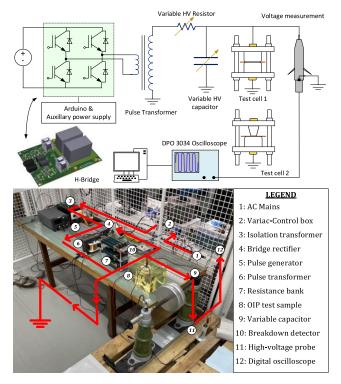

An overview of the built prototype pulse modulator is shown in Fig. 21. The system operates in the following three stages.

- The source 230-V<sub>AC</sub> mains is isolated through a transformer and rectified to a smooth dc with a thyristor bridge.

- 2) The bridge powers an H-bridge pulse generator PCB, which produces  $650\text{-V}_{pk\text{-}pk}$  bipolar pulses controlled by an Arduino.

- 3) The low voltage pulses are stepped up through the designed 1:50 PT and tuned by test elements  $R_t$  and

Fig. 21. Overview of modulator prototype for dielectric testing.

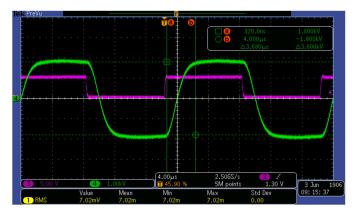

Fig. 22. Measurement of pulse parameters at 50 kHz.

$C_t$  before being applied across the oil-immersed test sample.

The output pulse waveform is analyzed in Fig. 22. The measured rise time  $T_r = 1.84~\mu s$  (Fig. 22) satisfies the  $T_r < 0.2T_p$  criteria in Table III. Measured pulse tops were  $T_p = 6.32~\mu s$  at 50 kHz and  $T_p = 46.32~\mu s$  at 10 kHz. Pulse overshoot was critically damped ( $\Delta V \approx 0$ ) for all tests to study the impact of pulse frequency. The duty cycle was set to 50%. In the next section, these pulses will be applied in tests.

# IV. DIELECTRIC TESTING

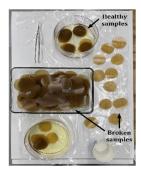

This section applies the modulator prototype to perform dielectric tests. OIP samples with average thickness of 150  $\mu$ m are cut and impregnated inside a vacuum oven as shown in Fig. 23. Samples are kept under oil, transferred to the test setup, and stored later for breakdown pattern analysis [33].

Fig. 23. Preparation workflow of OIP samples for pulsed tests.

Fig. 24. Breakdown distribution for cylindrical/conical electrodes.

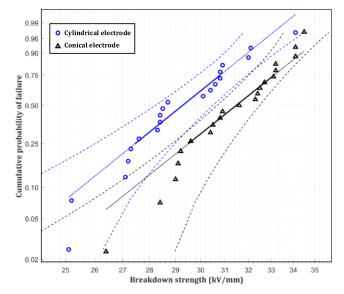

# A. Breakdown Strength

To determine the breakdown strength of insulation samples with cylindrical and conical electrodes, pulsed waveforms at 50-kHz ramping at  $1 \text{ kV}_{pk}$ /s were applied. The cumulative failure probability F(E) is linearized across field magnitudes. This is expressed according to the Weibull probability model

$$F(E) = 1 - e^{-\left(\frac{E_{\text{break}}}{\alpha}\right)^{\beta}}.$$

(12)

Shape parameter  $\beta$  in Table VII is the slope of the resultant line, and scale parameter  $\alpha$  represents  $E_{\text{break}}$  at F(E)=63.2%. Plotting F(E) against breakdown strengths produces Fig. 24. The cylindrical electrode shown in Fig. 19 applies field uniformly across a larger area, thereby lowering breakdown strength (shifted left), and was hence selected for lifetime tests.

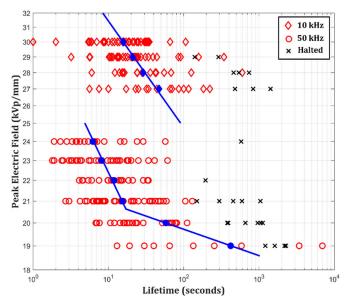

# B. Accelerated Aging

To perform lifetime tests, six E-field values were chosen with the highest value lower than the lowest breakdown strength  $E_{\text{break}} \approx 25 \text{ kV/mm}$  (Fig. 25). A total of 292 tests were performed with 20–41 tests at each field.  $R_t$  temperature was kept <50 °C with a fan and measured at intervals. Electrodes were polished after breakdowns. Failure time is plotted logarithmically in Fig. 25. Median lifetimes (blue points) are connected with a best-fit line to obtain lifelines at

Fig. 25. Obtained lifelines at 10 kHz (red diamonds) and 50 kHz (red circles) by connecting median points (blue points). Halted experiments (black crosses) are included in the median calculation.

TABLE VI

OBTAINED WEIBULL DISTRIBUTION PARAMETERS

| Parameter             | β    | α          |

|-----------------------|------|------------|

| Conical electrode     | 32.3 | 18.1 kV/mm |

| Cylindrical electrode | 31.3 | 17.8 kV/mm |

10 and 50 kHz. The remaining lifetime can then be expressed as an inverse power law model

$$T_{\text{life}} = k \left(\frac{E}{E_0}\right)^{-n}.$$

(13)

Constant k has a unit of time (seconds), while  $E_0$  has a unit of field strength (V/mm). Slope n indicates the sensitivity of lifetime to field variation. The obtained values are summarized in Table VI.

### C. Analysis of Aging Results

Trends from Fig. 25 can be divided into two aspects.

1) Frequency Impact: Dielectric lifetime and breakdown strength at 50 kHz is reduced when compared to 10 kHz. This aligns well with previous observations in the literature between 50 and 1500 Hz [33]. One potential cause is the increased dielectric losses leading to excessive heating in the insulation when stressed with higher frequency components [34]. However, the OIP sample is immersed in oil, an effective thermal conductor with low loss tangent. Hence, it is unlikely that the temperature of the test object would increase. The failure could then be due to the nonhomogenous nature of the oil-paper itself. This would result in an irregular temperature gradient with local hotspots, which eventually cause local (and over time, global) failure of the insulation. Tests at higher frequency produce larger capacitive losses, bring about earlier thermal breakdowns, and hence have shorter failure times.

2) Electric Field Impact: Dielectric lifeline at 50 kHz seems to "slow down" below a certain critical field  $F_c \approx 21$  kV/mm. A similar bend has been observed in literature by:

First, Yin et al. [7] indicated that the dielectric losses in magnet wire dramatically increase above the PDIV. These

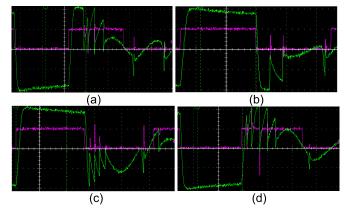

Fig. 26. Observed breakdown instants during. (a) During positive pulse top. (b) During negative pulse top. (c) During pulse fall time. (d) During pulse rise time.

TABLE VII

OBTAINED LIFETIME CURVE PARAMETERS

| Parameter                 | n    | k                              |

|---------------------------|------|--------------------------------|

| 10 kHz (above transition) | 9.5  | $1.7 \times 10^{15} \text{ s}$ |

| 50 kHz (above transition) | 6.9  | $2.1 \times 10^{10} \text{ s}$ |

| 50 kHz (below transition) | 37.5 | $3.6 \times 10^{50} \text{ s}$ |

TABLE VIII

STATISTICS OF BREAKDOWN INSTANTS OF 20 TESTS AT 10 KHZ

| Breakdown instant  | Breakdowns | Percentage |

|--------------------|------------|------------|

| Pulse tops         | 14         | 70 %       |

| Pulse rise or fall | 6          | 30 %       |

discharges produce heat within the dielectric leading to higher leakage currents and losses. This PD inception level has been shown to depend on specific pulse parameters [35].

Second, Crine [36] linked space charge injection in polyethylene above a critical field to an accelerated dielectric aging [37]. His work predicted a transition at  $F_c=18-20~\rm kV/mm$  at which any injected charges that have energies greater than the polymer cohesion energy can break weaker van der Waals bonds and speed up the insulation aging process [38].

Two alternate hypotheses for this bend are also explored.

- 1) Field enhancement in oil-filled voids between individual paper fibers can exceed local PDIV and accelerate aging.

- 2) Field enhancement at electrode edges exceeding local oil PDIV can accelerate aging due to discharges. However the breakdown burn marks from tests were always seen to be at the center, ruling out this explanation.

Although the above correlations sound promising, they must be explored further with extensive statistics specifically with oil-paper insulations. The modulator design presented in this article provides confidence in performing future research to fill this gap. It should also be noted that this phenomenon could not be observed at lower frequencies since the field strengths required for breakdown are far larger than the observed  $F_c$  value. High frequencies allow us to study low-field dielectric dynamics.

Finally, breakdown instants are analyzed in Fig. 26. Statistics from 20 tests given (Table VIII) show that most failures occur at the pulse top. It was seen that failures during pulse rise or fall usually occur at the end of the transition near maximum voltage.

### V. CONCLUSION

This article illustrates the complexities involved in developing pulse modulators for dielectric testing. A new PQR equation is derived to model such systems since existing literature cannot be applied to capacitor loads. The design procedure for a prototype modulator is described: navigating challenges such as tight core saturation criteria, optimization of transformer parasitics, and failure modes. Test elements  $R_t$   $C_t$  allow pulse shaping for consistent testing. Future work is aimed at applying the PQR equation to different modulator prototypes toward building a single comprehensive design optimization model. Breakdown and aging tests are performed on OIP samples at 10 and 50 kHz with pulses of  $T_r = 1.84 \ \mu s$ . A significant reduction is seen in lifetimes at 50 kHz. This is potentially due to the nonhomogenous distribution of dielectric losses leading to local hotspots in the insulation which eventually cause thermal breakdown. Increased losses at higher frequencies hence lead to shorter lifetimes. A critical field level  $F_c = 21$  kV/mm is found below which aging is slowed, possibly the transition into the non-PD regime of oil-filled cavities between paper fibers. Future research is aimed at generating a lifeline at 30 kHz and identifies  $F_c$  to understand if its value is an inherent property of the material itself or instead depends on pulse frequency.

### REFERENCES

- [1] J. W. Kolar and G. Ortiz, "Solid-state-transformers: Key components of future traction and smart grid systems," in *Proc. Int. Power Electron. Conf. (IPEC)*, 2014, pp. 18–21.

- [2] M. Ghassemi, "Accelerated insulation aging due to fast, repetitive voltages: A review identifying challenges and future research needs," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 26, no. 5, pp. 1558–1568, Oct. 2019, doi: 10.1109/TDEI.2019.008176.

- [3] J. A. Oliver and G. C. Stone, "Implications for the application of adjustable speed drive electronics to motor stator winding insulation," *IEEE Elect. Insul. Mag.*, vol. 11, no. 4, pp. 32–36, Jul./Aug. 1995, doi: 10.1109/57.400762.

- [4] J. P. Bellomo, P. Castelan, and T. Lebey, "The effect of pulsed voltages on dielectric material properties," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 6, no. 1, pp. 20–26, Feb. 1999, doi: 10.1109/94.752005.

- [5] M. Kaufhold, G. Borner, M. Eberhardt, and J. Speck, "Failure mechanism of the interturn insulation of low voltage electric machines fed by pulse-controlled inverters," *IEEE Elect. Insul. Mag.*, vol. 12, no. 5, pp. 9–16, Sep./Oct. 1996, doi: 10.1109/57.537190.

- [6] W. Yin, "Failure mechanism of winding insulations in inverter-fed motors," *IEEE Elect. Insul. Mag.*, vol. 13, no. 6, pp. 18–23, Nov./Dec. 1997, doi: 10.1109/57.637150.

- [7] W. Yin, K. Bultemeier, D. Barta, and D. Floryan, "Critical factors for early failure of magnet wires in inverter-fed motor," in *Proc. Conf. Electr. Insul. Dielectric Phenomena*, San Francisco, CA, USA, 1995, pp. 258–261, doi: 10.1109/CEIDP.1995.483712.

- [8] G. C. Montanari, D. Fabiani, and A. Contin, "Ageing investigation of turn insulation under fast repetitive pulse voltage with or without partial discharges," in *Proc. Coll Winding, Insul. Electr. Manuf. Exhib.*, Berlin, Germany, Jun. 1999, pp. 88–96.

- [9] A. Cavallini, D. Fabiani, and G. C. Montanari, "Power electronics and insulation systems—Part 2: Life modelling," *IEEE Elect. Insul. Mag.*, vol. 26, no. 4, pp. 33–39, Jul./Aug. 2010.

- [10] P. Wang, A. Cavallini, and G. C. Montanari, "Characteristics of PD under square wave voltages and their influence on motor insulation endurance," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 22, no. 6, pp. 3079–3086, Dec. 2015, doi: 10.1109/TDEI.2015.005158.

- [11] P. Wang, A. Cavallini, G. C. Montanari, and G. Wu, "Effect of rise time on PD pulse features under repetitive square wave voltages," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 20, no. 1, pp. 245–254, Feb. 2013, doi: 10.1109/TDEI.2013.6451364.

- [12] P. Wang, A. Cavallini, and G. C. Montanari, "The influence of repetitive square wave voltage parameters on enameled wire endurance," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 21, no. 3, pp. 1276–1284, Jun. 2014, doi: 10.1109/TDEI.2014.6832275.

- [13] P. Wang, A. Cavallini, and G. C. Montanari, "The influence of square wave voltage duty cycle on PD behavior," in *Proc. IEEE Conf. Electr. Insul. Dielectric Phenomena (CEIDP)*, Ann Arbor, MI, USA, Oct. 2015, pp. 338–341, doi: 10.1109/CEIDP.2015.7352006.

- [14] T. Koltunowicz, A. Cavallini, D. Djairam, G. C. Montanari, and J. Smit, "The influence of square voltage waveforms on transformer insulation break down voltage," in *Proc. Annu. Rep. Conf. Electr. Insul. Dielectric Phenomena*, Cancun, Mexico, Oct. 2011, pp. 48–51, doi: 10.1109/CEIDP.2011.6232593.

- [15] T. L. Koltunowicz, R. Kochetov, G. Bajracharya, D. Djairam, and J. J. Smit, "Repetitive transient aging, the influence of repetition frequency," in *Proc. Electr. Insul. Conf. (EIC)*, Annapolis, MD, USA, Jun. 2011, pp. 444–448, doi: 10.1109/EIC.2011.5996195.

- [16] D. Bortis, G. Ortiz, J. W. Kolar, and J. Biela, "Design procedure for compact pulse transformers with rectangular pulse shape and fast rise times," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 18, no. 4, pp. 1171–1180, Aug. 2011.

- [17] S. Candolfi, P. Viarouge, D. Aguglia, and J. Cros, "Hybrid design optimization of high voltage pulse transformers for klystron modulators," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 22, no. 6, pp. 3617–3624, Dec. 2015, doi: 10.1109/TDEI.2015.005047.

- [18] D. Aguglia et al., "Klystron modulator technology challenges for the Compact Linear Collider (CLIC)," in *Proc. IEEE Pulsed Power Conf.*, Chicago, IL, USA, Jun. 2011, pp. 1413–1421, doi: 10.1109/PPC.2011.6191626.

- [19] E. H. W. M. Smulders, B. E. J. M. van Heesch, and S. S. V. B. van Paasen, "Pulsed power corona discharges for air pollution control," *IEEE Trans. Plasma Sci.*, vol. 26, no. 5, pp. 1476–1484, Oct. 1998, doi: 10.1109/27.736042.

- [20] H. Akiyama, T. Sakugawa, T. Namihira, K. Takaki, Y. Minamitani, and N. Shimomura, "Industrial applications of pulsed power technology," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 14, no. 5, pp. 1051–1064, Oct. 2007, doi: 10.1109/TDEI.2007.4339465.

- [21] S. J. Beebe, "Applications for pulse power using nanosecond pulsed electric fields (nsPEFs) in cell biology and cancer treatment," *Bioelectr. Publications*, vol. 3, p. e123, Jan. 2013.

- [22] Rotating Electrical Machines—Part 18–41: Partial Discharge Free Electrical Insulation Systems (Type I) Used in Rotating Electrical Machines Fed From Voltage Converters, IEC Standard 60034, 2014.

- [23] R. Färber, "Endurance of polymeric insulation under mixed-frequency medium-voltage stress," Ph.D. dissertation, ETH High Voltage Lab., ETH Zurich, Zurich, Switzerland, 2019.

- [24] K. Whitham, "What is wrong with line-type modulators?" in *Proc. 29th Annu. Conf. IEEE Ind. Electron. Soc. (IECON)*, Roanoke, VA, USA, Nov. 2003, pp. 93–95, doi: 10.1109/IECON.2003.1279961.

- [25] W. J. Carey and J. R. Mayes, "Marx generator design and performance," in *Proc. Conf. Rec. 25th Int. Power Modulator Symp.*, High-Voltage Workshop., Hollywood, CA, USA, Jul. 2002, pp. 625–628, doi: 10.1109/MODSYM.2002.1189556.

- [26] R. Cassel, "The evolution of pulsed modulators from the Marx generator to the solid state Marx modulator and beyond," in *Proc. IEEE Int. Power Modulator High Voltage Conf. (IPMHVC)*, San Diego, CA, USA, Jun. 2012, pp. 9–13, doi: 10.1109/IPMHVC.2012.6518666.

- [27] M. Schueller et al., "Development of a pulsed high frequency source for testing cellulosic insulation material for high voltage solid state transformer applications," in *Proc. IEEE Int. Conf. High Voltage Eng. Appl. (ICHVE)*, Athens, Greece, Sep. 2018, pp. 1–4, doi: 10.1109/ICHVE.2018.8641793.

- [28] K. Niayesh and E. Gockenbach, "On the aging mechanism of solid insulating materials exposed to repetitive high voltage pulses," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 21, no. 1, pp. 304–310, Feb. 2014, doi: 10.1109/TDEI.2013.004055.

- [29] IEEE Standard for Pulse Transformers, IEEE Standard 390, 1987.

- [30] G. N. Glasoe and W. H. Bostick, "Pulse generators," MIT Radiation Laboratory Series, vol. 5. New York, NY, USA: McGraw-Hill, 1948, ch. 14.

- [31] S. Stathis and J. Biela, "Optimal design of a transformer-based solid-state pulse modulator with a damping network for ultra-fast rise times," in *Proc. 23rd Eur. Conf. Power Electron. Appl. (EPE-ECCE Europe)*, Ghent, Belgium, Sep. 2021, pp. p.1–p.11, doi: 10.23919/EPE21ECCEEurope50061.2021.9570450.

- [32] M. Jaritz and J. Biela, "Isolation design of a 14.4kV, 100kHz transformer with a high isolation voltage (115kV)," in *Proc. IEEE Int. Power Modulator High Voltage Conf. (IPMHVC)*, San Francisco, CA, USA, Jul. 2016, pp. 73–78, doi: 10.1109/IPMHVC.2016.8012831.

- [33] M. G. Niasar and W. Zhao, "Aging of oil-impregnated paper at different frequencies," in *Proc. IEEE Int. Conf. Properties Appl. Dielectric Mater. (ICPADM)*, Jul. 2021, pp. 430–433, doi: 10.1109/ICPADM49635.2021.9493911.

- [34] B. Sonerud, T. Bengtsson, J. Blennow, and S. M. Gubanski, "Dielectric heating in insulating materials subjected to voltage waveforms with high harmonic content," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 16, no. 4, pp. 926–933, Aug. 2009, doi: 10.1109/TDEI.2009.5211835.

- [35] A. Cavallini, E. Lindell, G. C. Montanari, and M. Tozzi, "Inception of partial discharges under repetitive square voltages: Effect of voltage waveform and repetition rate on PDIV and RPDIV," in *Proc. Annu. Rep. Conf. Electr. Insul. Dielectic Phenomena*, West Lafayette, IN, USA, Oct. 2010, pp. 1–4, doi: 10.1109/CEIDP.2010.5724033.

- [36] J.-P. Crine, "A molecular model to evaluate the impact of aging on space charges in polymer dielectrics," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 4, no. 5, pp. 487–495, Oct. 1997, doi: 10.1109/94.625641.

- [37] H. R. Zeller, "Breakdown and prebreakdown phenomena in solid dielectrics," *IEEE Trans. Electr. Insul.*, vol. EI-22, no. 2, pp. 115–122, Apr. 1987, doi: 10.1109/TEI.1987.298867.

- [38] J.-P. Crine, "On the interpretation of some electrical aging and relaxation phenomena in solid dielectrics," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 12, no. 6, pp. 1089–1107, Dec. 2005, doi: 10.1109/TDEI.2005.1561789.

- [39] P. Mathew and M. G. Niasar, "Lifetime of oil-impregnated paper under pulse stress at different frequencies," in *Proc. 27th Nordic Insul. Symp.* (*NordIS*), vol. 27, no. 1, 2022, pp. 1–4.

- [40] P. Mathew, "Pulsed ageing of oil-paper: Test modulators and ageing trends," M.S. thesis, Dept. Elect. Eng., Math. Comput. Sci., TU Delft, Delft, The Netherlands, 2021.

Philip Mathew (Graduate Student Member, IEEE) was born in Mumbai, India, in 1997. He received the B.Tech. degree in electrical engineering from NIT-K, Surathkal, India, in 2019, and the M.Sc. degree in power engineering from TU Delft, Delft, The Netherlands, in 2021; with a specialty in combining high-voltage physics and power electronics. His master's thesis studied the dielectric aging phenomenon under high-frequency pulsed stresses specifically seen in oil-paper insulations.

At IIT Delhi, he researched PV-based microgrids for spreading electricity access in rural areas. During his studies, he also interned and later worked part-time at the Research and Development for Prysmian Group, Milan, Italy. He is currently employed as a Research and Development Engineer with Hitachi Energy, Ludvika, Sweden; working with BiMOS semiconductors in gigawatt HVDC converter systems. He will next join CERN in Geneva, Switzerland, to design high-power electronics for their particle accelerators.

Mohamad Ghaffarian Niasar was born in Tehran, Iran, in 1984. He received the M.S. degree from the Sharif University of Technology, Tehran, Iran, in 2008, and the Ph.D. degree from the Royal Institute of Technology, Stockholm, Sweden, in 2015.

He is currently an Assistant Professor with the High Voltage Technologies Group, Delft University of Technology, Delft, The Netherlands. His main research interests include the aging of electrical insulation, HVDC insulation, partial

discharges, high-frequency power transformers, power cables, and FEM modeling.

Peter Vaessen (Member, IEEE) was born in Maasbree, The Netherlands, in 1960. He received the M.Sc. degree (cum laude) in electrical power engineering from Eindhoven Technical University, Eindhoven, The Netherlands.

In 1985, he joined KEMA (now a CESI brand). In his 35-year career, he held research positions in the field of large power transformers and high-voltage measurement and testing. He has 25 years of experience in (U)HVDC Technology

and T&D Grids with high shares of renewables. He is a Manager of Innovations with KEMA Laboratories Arnhem, The Netherlands, and the Chairperson of the European Distributed Energy Resources Laboratories Association (DERlab), Kassel, Germany. Since 2017, he has been a part-time Professor of hybrid transmission systems with the Delft University of Technology, Delft, The Netherlands, where he teaches courses on both high-voltage technologies and HVDC.