**Delft University of Technology**

# High-Performance Multilevel Class-D Audio Amplifiers

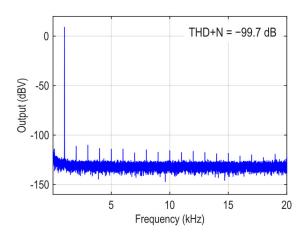

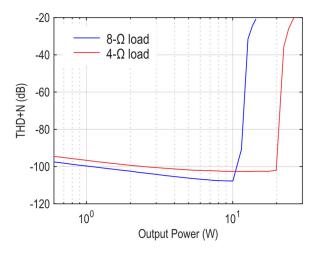

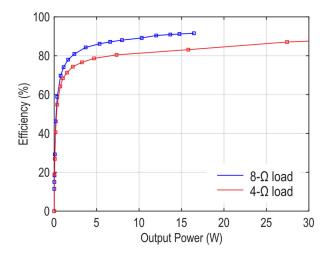

Zhang, H.

DOI 10.4233/uuid:d9cae0f9-23ca-45ab-83a1-0965014db6b7

Publication date 2024

**Document Version** Final published version

Citation (APA) Zhang, H. (2024). High-Performance Multilevel Class-D Audio Amplifiers. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:d9cae0f9-23ca-45ab-83a1-0965014db6b7

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

#### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# High-Performance Multilevel Class-D Audio Amplifiers

Dissertation

for the purpose of obtaining the degree of doctor

at Delft University of Technology

by the authority of the Rector Magnificus prof.dr.ir. T.H.J.J. van der Hagen

chair of the Board for Doctorates

to be defended publicly on

Monday 15 April 2024 at 15:00 o'clock

by

Huajun ZHANG

Master of Science in Electrical Engineering, University of Michigan, USA

born in Beijing, China

This dissertation has been approved by the promotors.

Composition of the doctoral committee: Rector Magnificus, chairperson Prof.dr. K.A.A. Makinwa, Delft University of Technology, promotor Dr. Q. Fan, Delft University of Technology, copromotor

Independent members:

Prof.dr. G.Q. Zhang, Delft University of TechnologyProf.dr. J. Xu, Fudan University, ChinaDr.ir. P.J.A. Harpe, Eindhoven University of TechnologyDr.ir. R.A.R. van der Zee, University of TwenteProf.dr.ir. W. van Driel, Delft University of Technology, reserve member

Other member:

Dr. M. Berkhout, Goodix Technology

This research was funded partially by Goodix Technology and partially by NXP Semiconductors.

Copyright © by Huajun Zhang

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any other means, or stored in a database or retrieval system, without the prior written permission of the author.

# **Table of Contents**

| CHAP   | FER 1 | 1 INTRODUCTION                        | 1  |

|--------|-------|---------------------------------------|----|

| 1.1    | M     | OTIVATION                             | 1  |

| 1.2    | BA    | ACKGROUND                             | 2  |

| Ĺ      | 1.2.1 | Principle of Operation                | 2  |

| Ĺ      | 1.2.2 | Power Loss and Efficiency             | 4  |

| Ì      | 1.2.3 | Modulation Schemes                    | 6  |

| 1.3    | CH    | HALLENGES AND PRIOR ART               | 10 |

| Ì      | 1.3.1 | ЕМІ                                   | 10 |

| Ì      | 1.3.2 | Nonlinearity                          | 14 |

| Ì      | 1.3.3 | Noise                                 | 21 |

| 1      | 1.3.4 | Power Supply Rejection Ratio (PSRR)   | 23 |

| 1.4    | TH    | IESIS GOAL AND ORGANIZATION           | 24 |

| Ref    | EREN  | CES                                   | 25 |

|        | грр / |                                       | съ |

| CHAPT  |       |                                       |    |

| AUDIC  | AN    | PLIFIER.                              | 34 |

| 2.1    |       | TRODUCTION                            |    |

| 2.2    | Pr    | OPOSED OUTPUT STAGE                   | 35 |

|        | 2.2.1 | Topology                              | 35 |

|        | 2.2.2 | Modulation Scheme                     | 37 |

| 2.3    | CI    | RCUIT IMPLEMENTATION                  | 39 |

|        | 2.3.1 | Overview                              | 40 |

|        | 2.3.2 | Gate Charge Reuse                     | 42 |

|        | 2.3.3 | Floating Regulator                    | 42 |

| 4      | 2.3.4 | Level Shifter                         | 44 |

| 4      | 2.3.5 | Gate Driver                           | 44 |

| 4      | 2.3.6 | Output Transistor Sizing              | 45 |

| 4      | 2.3.7 | PVCM Regulator                        | 46 |

| 2.4    | Pr    | OTOTYPE CLOSED-LOOP CLASS-D AMPLIFIER | 47 |

| 4      | 2.4.1 | Loop Filter                           | 47 |

| ,<br>2 | 2.4.2 | Pulse Width Modulator                 | 49 |

| 2.5    | M     | EASUREMENT RESULTS                    | 51 |

| 2.6     | CONCLUSION                                    |    |

|---------|-----------------------------------------------|----|

| Refei   | RENCES                                        |    |

|         | ED 2 A 121 5 DD THD CLASS DAUDIO AMD          |    |

| CHAPTI  |                                               |    |

| DB LC F | FILTER NONLINEARITY SUPPRESSION               |    |

| 3.1     | INTRODUCTION                                  | 61 |

| 3.2     | PROPOSED ARCHITECTURE                         |    |

| 3       | 2.1 Inner Loop                                |    |

| 3       | 2.2 Outer Loop                                |    |

| 3       | 2.3 Nonlinearity Suppression                  |    |

| 3       | 2.4 $f_{LC}$ Tolerance                        |    |

| 3.3     | CIRCUIT IMPLEMENTATION                        | 71 |

| 3       | 3.1 Loop Filter                               |    |

| 3       | 3.2 Overload Detection and Recovery           |    |

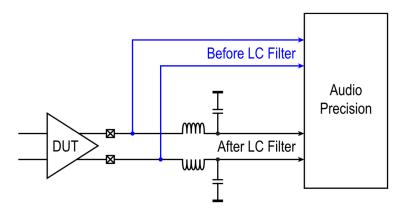

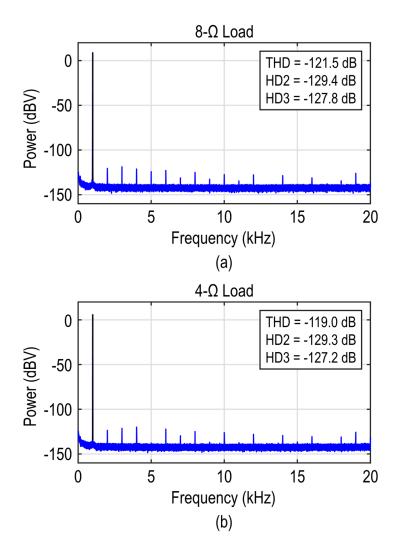

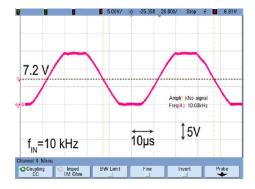

| 3.4     | MEASUREMENT RESULTS                           |    |

| 3.      | 4.1 Audio Performance                         |    |

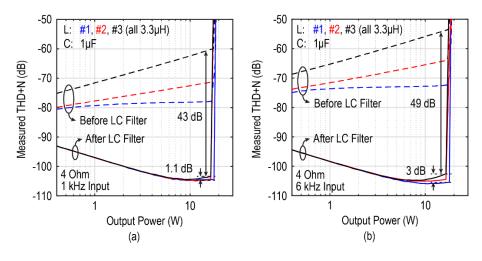

| 3.4     | 4.2 Suppression of LC Filter Nonlinearity     |    |

| 3.4     | 4.3 Variations in Loading and f <sub>LC</sub> |    |

| 3.4     | 4.4 Efficiency and Idle Power                 |    |

| 3.4     | 4.5 Comparison with the State-of-the-Art      |    |

| 3.5     | Conclusion                                    |    |

| Refei   | RENCES                                        |    |

|         |                                               |    |

| CHAPTI  |                                               |    |

| CLASS-I | D AUDIO AMPLIFIER /                           |    |

| 4.1     | INTRODUCTION                                  |    |

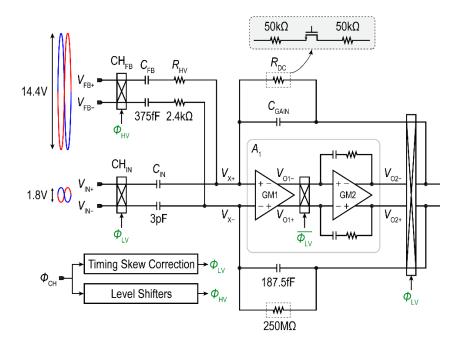

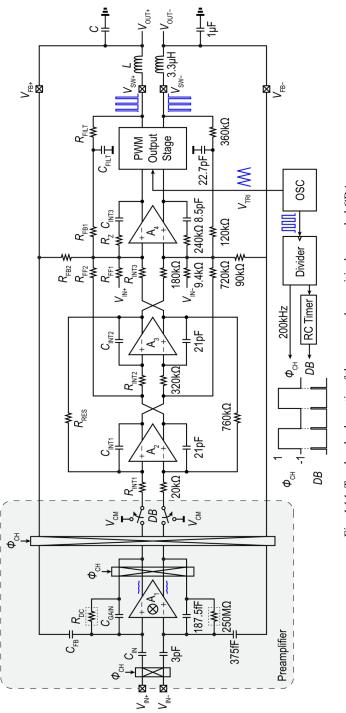

| 4.2     | CAPACITIVELY COUPLED CHOPPER CDA              |    |

| 4       | 2.1 Overview                                  |    |

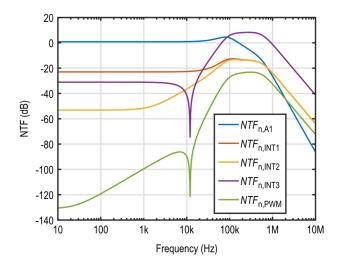

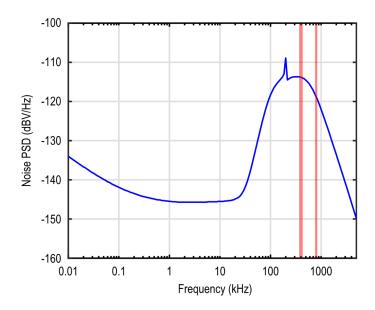

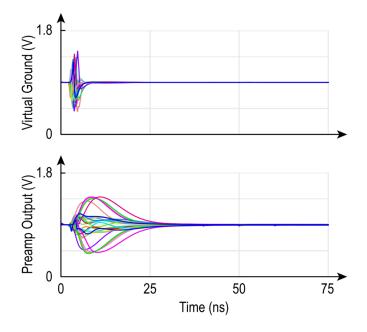

| 4       | 2.2 Noise Analysis                            |    |

| 4.3     | CIRCUIT IMPLEMENTATION                        |    |

| 4       | 3.1 Capacitively Coupled Chopper Preamplifier |    |

| 4       | 3.2 <i>HV</i> Chopper                         |    |

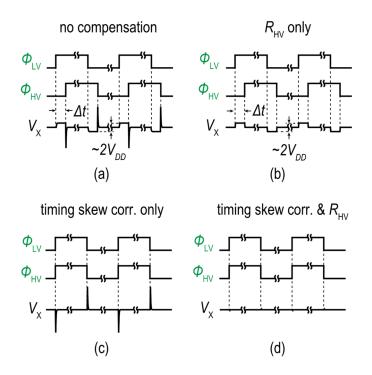

| 4       | 3.3 Timing Skew Correction                    |    |

| 4       | 3.4 Impedance Compensation                    |    |

| 4       | 3.5 CDA                                       |    |

| 4.4   | M     | EASURE  | MENT RESUL   |           |                   |                | 107         |

|-------|-------|---------|--------------|-----------|-------------------|----------------|-------------|

| 4.5   | Co    | NCLUSI  | ON           |           |                   |                | 114         |

| Refe  | ERENG | CES     |              |           |                   |                | 114         |

| СНАРТ | ER :  | 5 A     | 120.9DB      | DR        | DIGITAL-INF       | PUT CAPA       | CITIVELY    |

| COUPL | ED (  | СНОРЕ   | PER CLASS    | S-D AU    | DIO AMPLIFIE      | ER             | 118         |

| 5.1   | In    | FRODUC  | TION         |           |                   |                | 118         |

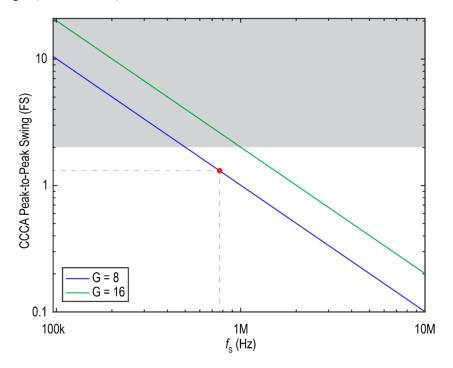

| 5.2   | Di    | gital-I | NPUT CAPAC   | CITIVEL   | Y COUPLED CHOP    | PER CDA        | 119         |

| 5.    | .2.1  | Overvi  | ew           |           |                   |                | 119         |

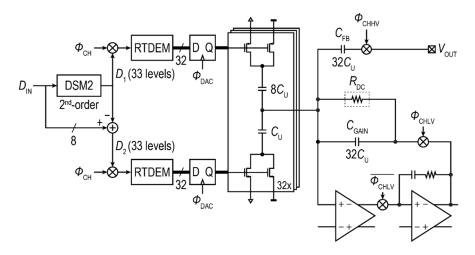

| 5.    | .2.2  | DAC S   | ampling Fre  | equency   | ,                 |                | 120         |

| 5.    | .2.3  | DACK    | Resolution   |           |                   |                | 122         |

| 5.    | .2.4  | Interm  | odulation    |           |                   |                | 124         |

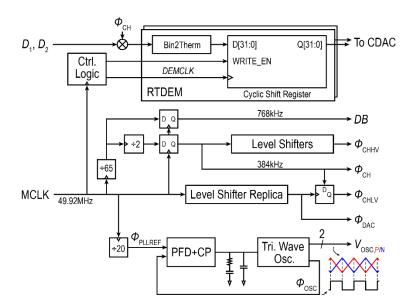

| 5.3   | DA    | AC IMPL | .EMENTATIO   | N         |                   |                | 124         |

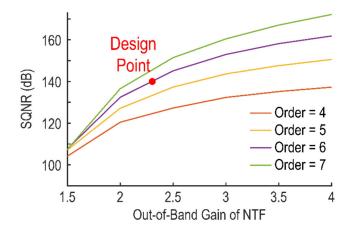

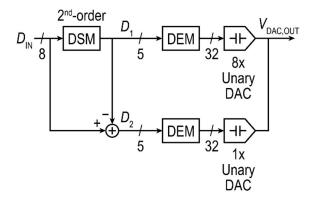

| 5.    | .3.1  | Delta-  | Sigma Modu   | lator D   | esign             |                | 124         |

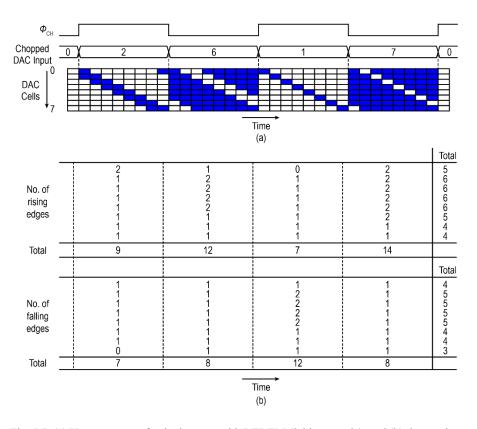

| 5.    | .3.2  | Dynan   | ic Element   | Matchir   | ıg (DEM)          |                | 125         |

| 5.    | .3.3  | Clock.  | Jitter       |           |                   |                | 132         |

| 5.4   | CL    | osed-L  | OOP CDA      |           |                   |                |             |

| 5.    | .4.1  | Top-Le  | evel         |           |                   |                | 135         |

| 5.    | .4.2  | Timing  | and RTDE     | M Logi    | 2                 |                | 137         |

| 5.    | .4.3  | DAC     |              |           |                   |                | 138         |

| 5.5   | M     | EASURE  | MENT RESUL   |           |                   |                | 139         |

| 5.6   | Сс    | NCLUSI  | ON           |           |                   |                | 146         |

| Refe  | ERENG | CES     |              |           |                   |                | 146         |

| СНАРТ | ER (  | s co    | NCLUSIO      | NS AN     | D OUTLOOK         |                | 152         |

| 6.1   | M     | AIN CON | TRIBUTIONS   | 5         |                   |                | 152         |

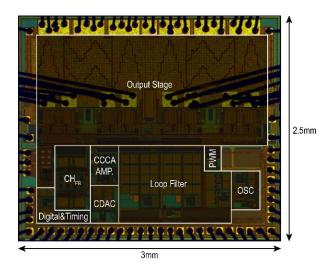

| 6     | .1.1  | 4.2 MF  | Hz Fully-Dif | ferentia  | l Multilevel PWN  | l Output Stage | (Chapter 2) |

|       |       |         |              |           |                   |                |             |

| 6     | .1.2  | Dual-I  | Loop Feedba  | ck-afte   | r-LC Architecture | e (Chapter 3)  |             |

| 6     | .1.3  |         |              |           | DA Using Capacit  |                |             |

|       |       | -       |              | -         |                   |                |             |

| 6     | .1.4  | Digital | l-Input Capa | icitively | , Coupled CDA (   | Chapter 5)     |             |

| 6.2   | M     |         |              |           |                   |                |             |

| 6.3   | Сс    | MPARIS  | ON WITH TH   | E STAT    | E-OF-THE-ART      |                |             |

| 6.4   | Fu    | TURE R  | ESEARCH DI   | RECTIO    | NS                |                |             |

| 6.4.                                  | 1 Other Feedback-after-LC Architectures             | 156                       |

|---------------------------------------|-----------------------------------------------------|---------------------------|

| 6.4.                                  | 2 Capacitively Coupled CDA with Open-Loop Front-End | 157                       |

| 6.4.                                  | 3 Ultra-Low-Power CDA for TWS Headphones            | 158                       |

| 6.4.                                  | 4 GaN-Based CDA                                     | 159                       |

| 6.4.                                  | 5 Advanced Packaging Solutions                      | 159                       |

| 6.5                                   | CONCLUDING REMARKS                                  |                           |

| Refere                                | NCES                                                |                           |

| SUMMAR                                | Υ                                                   | 162                       |

|                                       |                                                     |                           |

| SAMENV                                | ATTING                                              | 165                       |

|                                       | ATTING                                              |                           |

| LIST OF I                             |                                                     | 169                       |

| LIST OF I<br>Journa                   | PUBLICATIONS                                        | <b>169</b><br>169         |

| LIST OF I<br>Journ <i>a</i><br>Confei | PUBLICATIONS                                        | <b> 169</b><br>169<br>169 |

# Chapter 1 Introduction

# 1.1 Motivation

Loudspeakers are ubiquitous in modern life. In the audio band, they typically have an impedance in the order of a few ohms and, depending on the application, dissipate to several watts to kilowatts, which means they must be driven by a power amplifier. The steady development of consumer electronics and automotive infotainment systems has increased the demand for high-performance and high-efficiency audio amplifiers.

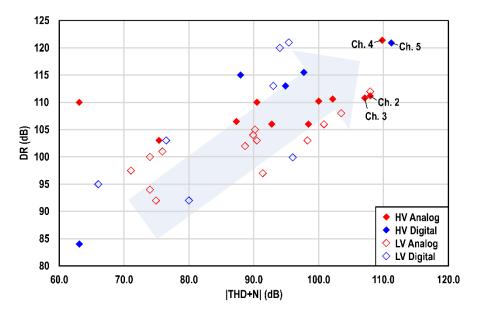

Traditionally, Class-AB amplifiers are used to drive loudspeakers. However, for a sinusoidal input, their power efficiency is limited to a theoretical maximum of 78% [1], since their output stages typically consist of common source (emitter) amplifiers or source (emitter) followers, which must simultaneously handle large voltages and currents. This results in significant heat dissipation, leading to bulky and complicated cooling solutions and reduced battery life in portable applications. Nevertheless, Class-AB amplifiers are still prevalent in low-power (e.g., headphone) applications due to their excellent audio performance. For example, a Class-AB amplifier [2] driven by a standalone DAC [3] achieves a total harmonic distortion plus noise (THD+N) well below –100 dB, together with a dynamic range (DR) above 120 dB. Recent monolithic solutions also achieve similar or even better performance [4], [5].

In high-power applications, however, Class-D amplifiers (CDAs) are taking over from Class-AB amplifiers because their power efficiency is typically greater than 90%, which significantly simplifies their cooling requirements, thereby reducing system cost and size [6]. The advent of bipolar-CMOS-DMOS (BCD) process technology has made monolithic high-

voltage (HV, >10 V) CDAs feasible, thus enabling further miniaturization [7]. However, compared to Class-AB amplifiers, CDAs suffer from several disadvantages, including greater electromagnetic interference (EMI), lower dynamic range, and inferior linearity. In the coming sections, the basic operation of CDAs and the reasons for these disadvantages will be discussed in more detail.

# 1.2 Background

# **1.2.1** Principle of Operation

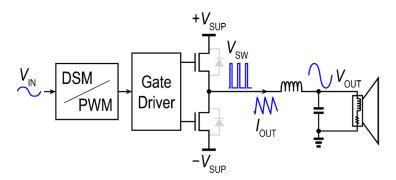

The term "Class-D" refers to a mode of operation in which an amplifier's output transistors function as switches, which, ideally, do not dissipate power. The required output voltage is then approximated by rapidly switching the output between a small number of supply voltages and low-pass filtering the result. Fig. 1.1 illustrates the operation of a typical single-ended (SE) Class-D output stage. This circuit, also known as the half-bridge, is widely used in various power electronics applications. The negative supply is required to ensure that no DC current flows through the speaker.

Fig. 1.1. Basic single-ended Class-D output stage.

In Fig. 1.1, the output is switched between discrete voltages, i.e.,  $\pm V_{SUP}$ , which are produced at the switching node ( $V_{SW}$ ) by the output stage. As a

result,  $V_{SW}$ , besides the audio-band content of the input signal  $V_{IN}$ , also consists of high-frequency components. The audio signal can be recovered by an LC low-pass filter or, in low-cost applications, by the speaker itself, since this typically behaves like an LR low-pass filter.

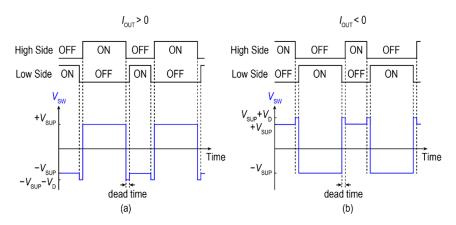

To avoid shorting the supply and ground (aka. cross conduction or shootthrough), a dead time is usually implemented to guarantee break-before-make switching of the high-side and low-side output transistors [7], [8]. The inductive load will still force a continuous current through the output stage nevertheless. This current will flow through the body diodes of the transistors (shown in grey in Fig. 1.1), adding a diode drop  $V_D$  to the output. The resulting output waveform is shown in Fig. 1.2.

Fig. 1.2. Impact of dead time on the Vsw waveform.

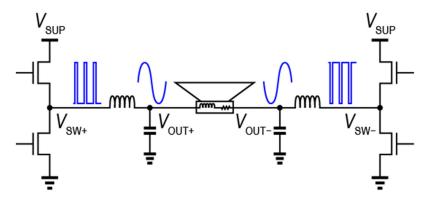

To obviate the need for a negative supply, the speaker can be connected between two half-bridges, which is known as the bridge-tied-load (BTL) configuration, and the resulting output stage is called a full bridge or an Hbridge [9] (Fig. 1.3).

Fig. 1.3. Class-D output stage with bridge-tied-load (BTL) configuration.

# 1.2.2 Power Loss and Efficiency

The non-zero power dissipation of a practical Class-D output stage can be divided into conduction loss, transition loss, reverse conduction loss, and gate charge loss [10].

Conduction loss occurs in all the resistances that carry the load current, including the output transistors, metallization, bondwire, package, PCB routing, and the external inductor. Wider output transistors thus reduce the conduction loss on the chip at the expense of a larger silicon area.

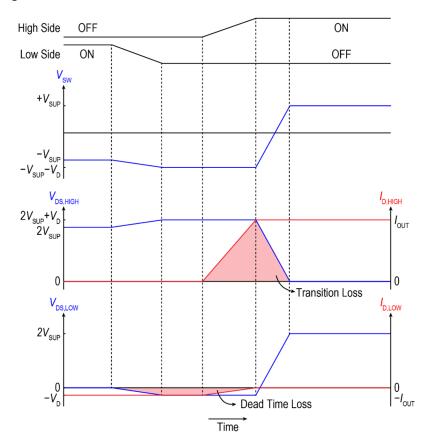

As illustrated in Fig. 1.4, another source of power loss is due to the output transistor's finite switching speed, which is known as the transition loss. Due to the low-side body diode, when  $I_{OUT} > 0$ ,  $V_{SW}$  will not rise until the output current is completely sourced from the high side. Therefore, during the transition, the high-side transistor's drain-source voltage ( $V_{DS,HIGH}$ ) and drain current ( $I_{D,HIGH}$ ) are both nonzero, which implies power dissipation. Transition loss can be reduced by increasing the switching speed. However, this leads to a high di/dt in the output stage, inducing ringings due to parasitic inductances in the system, which could overstress the output transistors and lead to EMI issues. During the dead time, reverse conduction

through the body diode also causes power loss, as shown in the bottom plot of Fig. 1.4.

Fig. 1.4. Zoomed-in view of a rising transition in Fig. 1.2(a). For simplicity, the effect of parasitic capacitance is ignored.

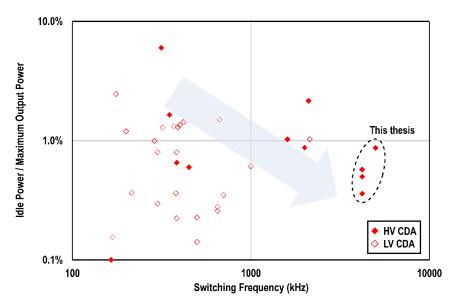

Periodic charging of the input and output capacitances of the output transistors also adds to the power loss. The former is called gate charge loss, while the latter adds to the transition loss. They are proportional to the switching frequency and are present even when a zero input is applied to the CDA, and thus  $I_{OUT} \approx 0$ . The CDA's power consumption, in this case, is defined as the *idle power*. It can be reduced by employing segmented power transistors [11], by choosing a low switching frequency [12], [13], [14], and

by adopting a switching scheme that lowers the switching frequency at low input levels [15], [16].

To quantify the power loss with respect to the power delivered to the speaker, a CDA's efficiency ( $\eta$ ) is defined by the ratio between the power delivered to the load ( $P_{\text{LOAD}}$ ) and the power drawn from the supply ( $P_{\text{SUPPLY}}$ ):

$$\eta = \frac{P_{\text{LOAD}}}{P_{\text{SUPPLY}}} \times 100\%.$$

(1.1)

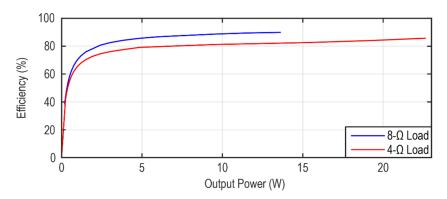

It is typically around, or above, 90% for a CDA.

# 1.2.3 Modulation Schemes

As mentioned above, the modulation scheme of a CDA maps the input audio signal into discrete voltage levels. To maintain high audio quality, it should introduce minimal noise and distortion in the audio band. To achieve this, pulse width modulation (PWM) and delta-sigma modulation (DSM) are commonly used.

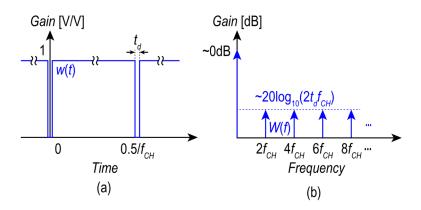

#### 1.2.3.1 PWM

PWM produces square-wave pulses whose duty cycle, and thus, whose low-frequency component, tracks the audio input. This can be implemented by comparing the input signal with a triangle wave (aka. a carrier) with a frequency of  $f_{sw}$ . This operation is known as natural sampling PWM [9] and is illustrated in Fig. 1.5(a). Fig. 1.5(b) shows the spectrum of  $V_{sw}$ , which consists of the input, PWM tones, and sidebands. As shown, natural sampling ideally does not introduce in-band distortion.

Fig. 1.5. (a) Timing diagram of natural sampling PWM, and (b) spectrum of  $V_{SW}$ .

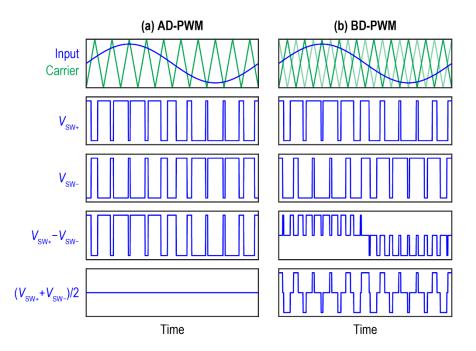

In a BTL output stage, the two half-bridges can be configured to switch in a fully-differential fashion. This is known as the AD mode [Fig. 1.6(a)]. The output thus has no CM content at the switching frequency, which is beneficial for EMI (Section 1.3.1). Alternatively, the two half-bridges can be modulated separately using two triangle waves with opposite phases, which is known as the BD mode [Fig. 1.6(b)]. In this case, no current flows through the load for a zero input, reducing the idle power consumption. For the differential output, it also produces three output levels and doubles the effective PWM frequency. However, the output CM exhibits a rail-to-rail swing, which causes strong tones in the CM spectrum around the switching frequency and its harmonics.

Fig. 1.6. Waveform of (a) AD and (b) BD PWM.

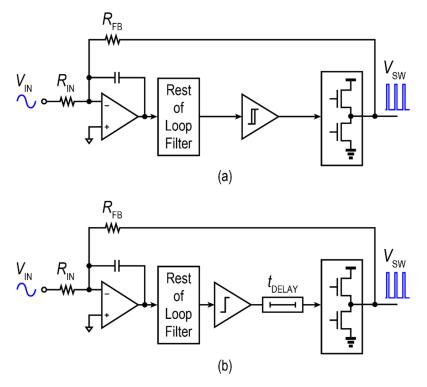

Apart from comparing an input signal with a triangle wave, PWM can also be implemented by a self-oscillating feedback loop based on internal hysteresis or delay [9], as shown in Fig. 1.7. However, the resulting switching frequency varies with the input signal, since the slew rate of the loop filter output is input-dependent, leading to an unpredictable EMI spectrum and potential crosstalk between channels [9], [17].

Chapter 1

Fig. 1.7. Self-oscillating CDA based on (a) hysteresis and (b) delay.

# 1.2.3.2 Delta-Sigma Modulation (DSM)

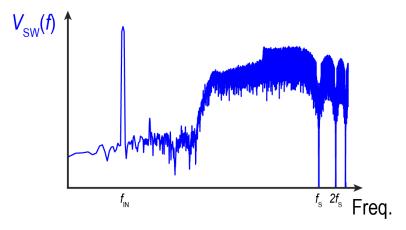

DSM employs oversampling and noise shaping to realize discrete output levels while maintaining a high in-band SNR. Quantization noise is pushed out of the signal band, resulting in a wideband noise spectrum, as shown in Fig. 1.8, which spreads the EMI power and facilitates a filterless configuration [15], [16], [18]. Single-bit DSM is also known as pulse density modulation (PDM). For a BTL output stage, the two switching nodes can be controlled independently as in BD-PWM, resulting in the generation of three differential output levels with a single supply [18], which improves the SQNR.

Fig. 1.8. Output spectrum of CDA based on DSM with an input tone at  $f_{IN}$  sampled at  $f_{S}$ .

Unfortunately, CDAs based on high-order PDM suffer from instability at large signal amplitudes, so they cannot produce the full output swing offered by the power supply. Dynamically reducing the loop filter order can keep the loop stable up to the full scale (FS) at the expense of lower SNR [15].

# **1.3** Challenges and Prior Art

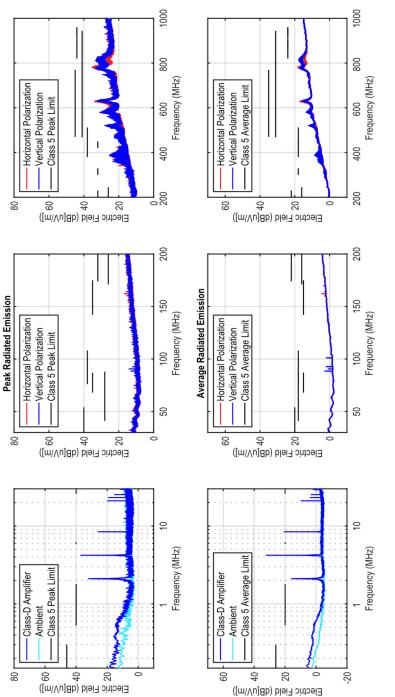

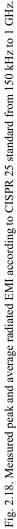

# 1.3.1 EMI

High-frequency switching activities in the output stage are coupled into, and radiated by, the cable harness connecting the power supply, audio amplifiers, and speakers, which is known as radiated EMI. It is particularly problematic in automotive applications, which must comply with strict EMI standards (e.g., CISPR 25 Class 5 [19]). Fully differential switching is preferred to meet this requirement since EMI produced by the 2 output nodes will then partially cancel each other out [17], [20]. The residual EMI must then be suppressed by an LC filter at the output of the Class-D amplifier and/or shielding. Unfortunately, these solutions significantly increase system cost and bulk. In applications with low output power, short speaker cable, and relaxed EMI specifications (e.g., CISPR 32 Class B [21]), the LC filter can

be omitted, which is often referred to as the filterless configuration [18], [22], [23], [24], [25], [26].

Aside from radiated EMI, high-frequency components in the supply current due to the output transitions will cause power-supply ripple, which may interfere with other electronics sharing the same supply. This is known as conducted EMI, which can be mitigated by decoupling and filtering the supply along with careful PCB layout [27]. Another cause of high-frequency current, is the reverse recovery of the body diode. When it conducts, its pnjunction is filled with charge carriers, which are depleted when the diode is suddenly switched to reverse bias. This leads to current spikes in the supply and thus conducted EMI, which can be addressed by using an adaptive gate driver that avoids reverse recovery [28].

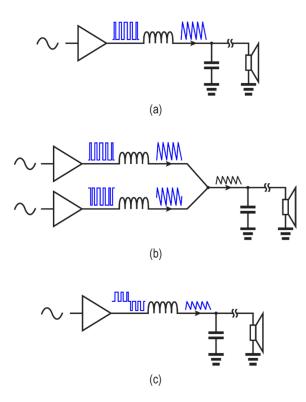

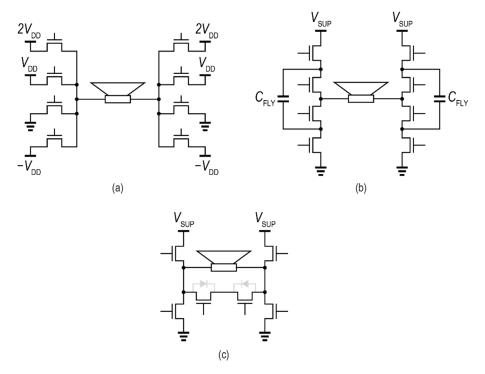

To mitigate EMI, multiphase [17] and multilevel output stages [16], [26], [29], [30], [31], [32], [33], [34], [35], [36], [37] have been proposed, as shown in Fig. 1.9.

Fig. 1.9. Switching activity in (a) conventional, (b) multiphase, and (c) multilevel CDAs.

In multiphase output stages [17], several output stages drive separate inductors while switching at different moments [Fig. 1.9(b)]. Therefore, the total high-frequency ripple current delivered to the load is reduced, which reduces EMI. However, this increases the number of inductors required, as well as the idle power dissipation caused by the ripple currents circulating in the various output stages. As the number of audio channels increases, the total system cost and idle power dissipation increase proportionally.

Multilevel output stages [Fig. 1.9(c)] reduce EMI by reducing the switching step size. In [29], [30], [31], [32], [33], [34], this is achieved by using multiple supply voltages, which often increases system cost [Fig. 1.10(a)]. Alternatively, this can be done by using (relatively low-cost) external flying capacitors to generate an intermediate output level equal to a

fraction (usually  $\frac{1}{2}$ ) of the supply [35], [36], as shown in Fig. 1.10(b). However, extra control circuitry is then required to regulate the voltage across these capacitors to half of the supply, thus increasing design complexity. In [16], [26], an extra output level is created by simply shorting the load [Fig. 1.10(c)], but it requires zero or even negative dead time for proper operation, resulting in a complicated gate-driving configuration. In [37], independent control of the back-to-back transistors shorting the load is proposed, which obviates zero dead time. However, in both cases, extra circuitry and, thus, idle power is required to robustly define the output CM.

Fig. 1.10. Prior-art multi-level CDA output stages using (a) multiple supplies, (b) flying capacitor, and (c) switches shorting the load.

Another way to meet the EMI challenge is by tailoring it to the requirements of the CISPR 25 EMI mask. Class-D amplifiers employing fixed-frequency pulse-width modulation (PWM) [38] or a hybrid of PWM

and DSM [39] can do this by switching at frequencies above 1.8 MHz where the EMI requirements are relaxed. This also allows the size of the LC filter to be reduced. However, this results in increased switching loss and, hence, higher idle power. On the other hand, Class-D amplifiers employing DSM [15], [18], [34], [37] can reduce EMI peaks by spreading the switching energy, which is useful in consumer applications. However, even with sampling frequencies of several MHz, their out-of-band quantization noise may still fall within the AM band, especially near the lower end of 150 kHz. Hence, an LC filter with a cutoff frequency much lower than 150 kHz may be required, e.g., 41 kHz is used in [15].

#### **1.3.2** Nonlinearity

Nonlinearity in a CDA distorts the signal of interest and should be minimized for optimal audio quality. There are several sources of nonlinearity in a CDA, which will be discussed in this section.

#### 1.3.2.1 Output Stage

Signal-dependent timing errors in the switching of the output stage can introduce distortion. As shown in Fig. 1.2, depending on the direction of the load current,  $V_{sw}$  can either make its transition before the dead time (known as soft switching) or after the dead time (known as hard switching) [9], thus causing a signal-dependent delay. This can be mitigated using a "zero" dead time, provided that cross-conduction can be robustly avoided through appropriate sizing [40]. Errors in the pulse shape, due to, e.g., nonlinear on-resistance and the forward voltage drop during body diode conduction, also add extra distortion.

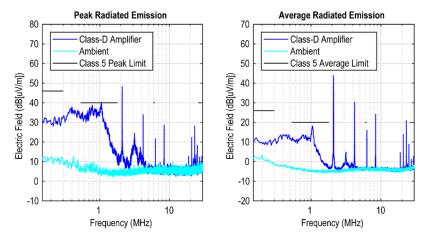

#### 1.3.2.2 Loop Filter

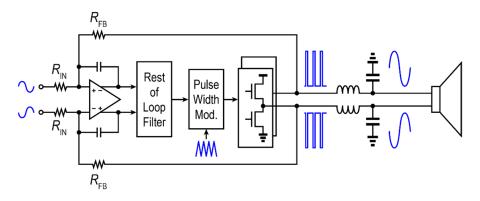

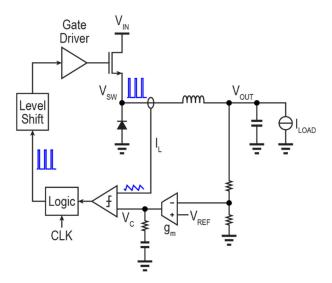

To improve linearity, feedback can be applied around the output stage. Fig. 1.11 illustrates such a closed-loop CDA. Its output is sensed by the feedback resistors  $R_{\text{FB}}$ , whose distortion is then suppressed by using one or more integrators to realize high loop gain in the audio band. Higher loop gain can be achieved by increasing the unity gain frequency ( $f_{\text{U}}$ ) of the feedback loop or the loop filter order. However, in constant-frequency PWM-based CDAs,  $f_{\text{U}}$  must stay below  $f_{\text{PWM}} / \pi$  to maintain correct PWM operation [7], [9] since the slew rate of the PWM modulator's input must be less than that of the triangle wave. Furthermore, residual ripple at the loop filter output, which contains PWM sidebands, can be demodulated back to the audio band by the PWM operation, thus limiting the linearity of closed-loop CDAs [41]. In [12], [13], [14], the PWM ripple is actively canceled to circumvent this limitation.

Fig. 1.11. Closed-loop constant-frequency PWM-based CDA.

The loop filter itself can also introduce distortion. The 1<sup>st</sup> integrator, which is the most critical for noise and distortion, must process the large current pulses coming through the feedback resistors, including PWM tones and sidebands, whose intermodulation products can fall into the audio band and lead to distortion. When using BD-PWM, the large CM swing [Fig. 1.6(b)]

modulates the CM level at the virtual ground of the 1<sup>st</sup> integrator, posing additional challenges for realizing a low-distortion loop filter.

#### 1.3.2.3 LC Filter

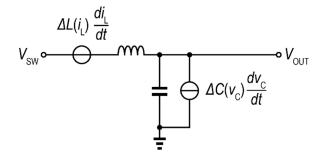

As mentioned in Section 1.3.1, LC filters are often required to suppress EMI. However, practical inductors and capacitors exhibit bias (current and voltage) dependencies, respectively, that cause distortion. This bias dependence can be modeled as follows:

$$L(i_L) = L_0 + \Delta L(i_L) \quad \text{and} \quad C(v_C) = C_0 + \Delta C(v_C). \quad (1.2)$$

In (1.2),  $i_L$  and  $v_C$  are the inductor current and capacitor voltage, respectively;  $L_0$  and  $C_0$  are the nominal inductance and capacitance, respectively. Therefore, their I-V relations can be expressed as:

$$v_{L}(i_{L}) = L_{0} \frac{di_{L}}{dt} + \underbrace{\Delta L(i_{L}) \frac{di_{L}}{dt}}_{v_{L,nonlinear}} \quad \text{and} \quad i_{C}(v_{C}) = C_{0} \frac{dv_{C}}{dt} + \underbrace{\Delta C(v_{C}) \frac{dv_{C}}{dt}}_{i_{C,nonlinear}}.$$

(1.3)

Equation (1.3) shows that the inductor's current dependence can be modeled as a nonlinear voltage in series, which appears low-pass filtered at the LC filter output (Fig. 1.12). Similarly, the capacitor's voltage dependence can be modeled by a nonlinear current in parallel, which is band-pass filtered when  $V_{SW}$  is driven by a low-impedance source in the case of a CDA.

Fig. 1.12. Circuit model for LC filter nonlinearity.

Hence, in audio applications, the LC filter nonlinearity is dominated by the inductor's current dependence and, according to [10], can be estimated by:

$$\text{THD}_{L} \approx \frac{f_{\text{IN}}}{f_{\text{LC}}Q} \cdot \frac{P_{\text{OUT}}}{6R_{L}I_{\text{SAT}}^{2}},$$

(1.4)

where  $f_{\rm LC} = (2\pi\sqrt{LC})^{-1}$  is the LC filter's cutoff frequency and  $I_{\rm SAT}$  is the inductor's saturation current.

From Equation (1.4), an  $I_{SAT} > 12$  A would be required for a THD < -100 dB, while the maximum load current for a CDA with 14.4 V supply and 4- $\Omega$  load is only 3.6 A. To verify this, the linearity of LC filters realized with three different inductors (Bourns PQ2614BHA-100K, Würth 7443340330, Murata FDSD0420-H-3R3M=P3) has been measured and listed in Table 1.1. As shown, the use of inductors with a large footprint and high cost is still necessary to guarantee high linearity.

|                  |              |           | ٠         |

|------------------|--------------|-----------|-----------|

| Dimension (mm)   | 28 x 20 x 16 | 8 x 8 x 7 | 4 x 4 x 2 |

| I <sub>SAT</sub> | 100 A        | 19 A      | 3.7 A     |

| THD*             | -102 dB      | -102 dB   | -60 dB    |

| Cost             | \$\$\$       | \$\$      | \$        |

Table 1.1. Selected inductors for CDA application.

Source: Bourns, Würth, Murata

\*Measured right before clipping across a 4- $\Omega$  load.

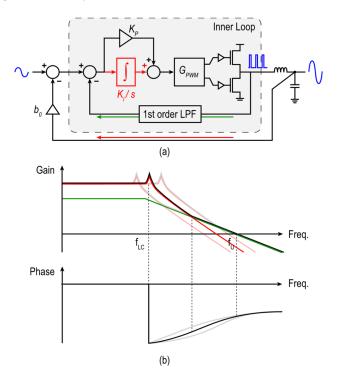

Feedback-after-LC architectures have been proposed to reduce the impact of LC filter nonlinearity [17], [42], [43], [44], [45], [46]. In such architectures, LC filter nonlinearity is suppressed by the amplifier's overall loop gain. However, implementing this is challenging because the LC filter introduces two additional complex poles into the amplifier's feedback path. Furthermore, practical inductors and capacitors have manufacturing tolerances, as well as bias (current and voltage) dependencies, leading to variations in  $f_{\rm LC}$ . In [43], [44], [46], self-oscillating architectures that take advantage of the LC filter's poles have been employed. However, their PWM frequency is signal- and  $f_{\rm LC}$  -dependent, leading to an unpredictable EMI spectrum, which restricts their use in EMI-sensitive applications.

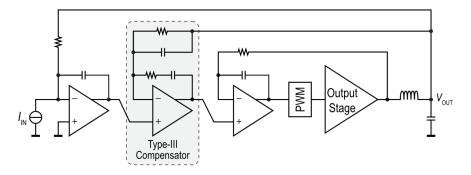

In fixed-frequency PWM designs, zeros can be added to the loop filter to compensate for the LC filter's phase shift. However, with a single feedback path, the loop bandwidth ( $f_{\rm U}$ ) will be a function of  $f_{\rm LC}$ . This limits the allowable  $f_{\rm LC}$  tolerance because  $f_{\rm U}$  should not exceed  $f_{\rm PWM} / \pi$  in Class-D amplifiers with fixed-frequency PWM [7], [42]. In [42], the effect of capacitance variation is eliminated by using a current-mode inner loop but  $f_{\rm U}$  still depends on the inductance, and the maximum modulation index is limited to 0.85. To mitigate this, a triple-feedback architecture (Fig. 1.13) is

proposed in [45], where a first feedback path around the output stage and before the LC filter desensitizes the loop bandwidth from  $f_{\rm LC}$  variations. A second feedback path after the LC filter is then stabilized with the help of a Type-III compensator. Finally, an outer 1<sup>st</sup> order feedback path increases the suppression of LC filter nonlinearity. However, due to its limited loop filter order and a low  $f_{\rm PWM}$  of 100 kHz, this design only achieves a modest (10 dB) suppression of LC filter nonlinearity at 20 kHz.

Fig. 1.13. The triple loop architecture of [45].

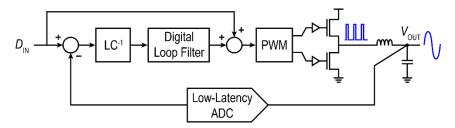

In [17], a digital feedback architecture is proposed in which a 5<sup>th</sup>-order digital loop filter provides 50 dB of loop gain around the LC filter at 20 kHz (Fig. 1.14). To maintain stability, the LC filter's poles are nominally canceled by an  $LC^{-1}$  filter implemented in the digital domain. This architecture requires a high-performance and low-latency ADC in the feedback path, significantly increasing its complexity. Furthermore, the mismatch between the external LC filter and the digital  $LC^{-1}$  filter compromises stability, which is exacerbated by its low loop bandwidth (100 kHz). As a result, the coefficients of the digital  $LC^{-1}$  filter have to be adjusted for a given LC filter, resulting in significantly increased application cost.

Fig. 1.14. Digital-input CDA with low-latency ADC feedback [17].

## 1.3.2.4 Digital-Input CDAs

Most audio sources nowadays are digital, so there is a growing trend towards CDAs with digital-inputs. Compared to a monolithic digital-input CDA solution, feeding the input of an analog-input CDA through a standalone DAC increases system size. It also makes the CDA more sensitive to RF interference [47]. Therefore, monolithic digital-input CDAs are preferred.

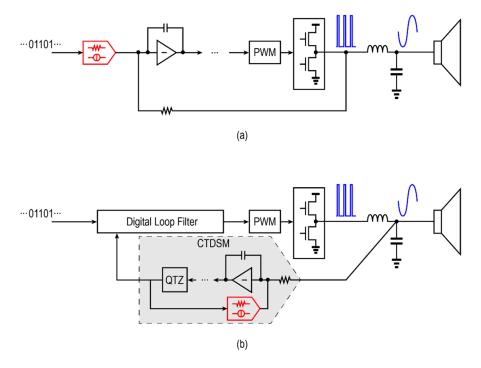

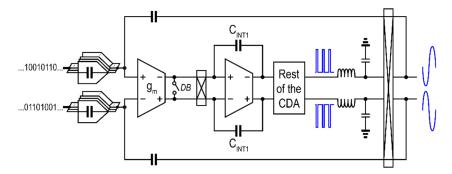

For a digital-input closed-loop CDA, an analog/digital interface is required so that the analog output can be fed back and compared against the digital input. If the comparison is performed in the analog domain, an upfront DAC will be required, whose noise and distortion will add to that of the CDA itself [16], [48], [49], as illustrated in Fig. 1.15(a).

Alternatively, an ADC can be employed to sense the CDA output, whose linearity will be limited by the internal feedback DAC of the ADC [17], [50], as shown in Fig. 1.15(b). In either case, therefore, the DAC's linearity is crucial to that of the CDA. Major distortion sources here are the unit-element mismatch and intersymbol interference (ISI) [51], [52], [53].

Single-bit PWM DACs [11], [47], [50], [54] do not suffer from unitelement mismatch because quantization is realized in the time domain. Since PWM is implemented in the digital domain, it also obviates the need for a triangle wave generator in the analog domain, further simplifying the design

[11]. However, since the signal is encoded into the pulse width, this type of DAC is more sensitive to clock jitter than a multi-bit DAC [55].

Fig. 1.15. Digital-input CDA architectures using: (a) upfront DAC [48] and (b) feedback ADC [17]. The main sources of distortion are highlighted in red.

# 1.3.3 Noise

The human ear has a high sensitivity, with a DR of above 120 dB [56], [57]. As mentioned in Section 1.1, audio drivers based on Class-AB amplifiers can achieve a DR higher than 120 dB. As will be discussed in the following, achieving a similar DR with a CDA is quite challenging.

# 1.3.3.1 Open-Loop CDAs

In an open-loop CDA, the main noise sources are the power supply and clock jitter. At small signal amplitudes, power supply noise appears mostly

as CM across the load and is thus suppressed [58]. On the other hand, clock jitter modulates the timing of output transitions and causes output noise as long as the CDA output keeps switching. The output noise due to the jitter is proportional to the transition step size and RMS value of the jitter (normalized to the switching frequency in the case of PWM [58] and quantizer sampling frequency in the case of DSM [59]).

In [58], an open-loop CDA with 120 dB of DR is reported, in which a digital input is first delta-sigma modulated and then directly used to control the duty cycle of an output stage. As such, its noise performance is limited by supply noise and clock jitter. To achieve the reported 120 dB dynamic range, an integrated clock jitter of less than 2 ps (rms) is required [58], which increases system cost. The open-loop architecture also leads to significant distortion at high power levels and poor power supply rejection.

In [54], the supply voltage is adaptively reduced at low power levels to reduce jitter sensitivity, while feedback is employed at high power levels to reduce distortion and improve supply rejection. However, the additional DC-DC converter required for supply scaling reduces power efficiency, whereas the amplitude-dependent use of resistive feedback causes significant noise floor modulation.

#### 1.3.3.2 Closed-Loop CDAs

For closed-loop CDAs (Fig. 1.11), supply noise and clock jitter in the output stage are suppressed by the loop gain, while the feedback network and loop filter introduce additional noise. Here, the noise floor is typically limited by the thermal noise generated by the resistors that set the CDA's closed-loop gain (or by the resistive or current DAC in a digital-input architecture) and by the amplifier in the 1<sup>st</sup> stage of the loop filter. The contribution of the latter is usually low since a well-designed active-RC integrator typically satisfies

$g_{\rm M}R_{\rm IN} >> 1$ , where  $R_{\rm IN}$  is the integrator's input resistance and  $g_{\rm M}$  is the amplifier's transconductance [51]. Furthermore, in addition to the resistor's thermal noise, the amplifier's flicker noise is also often significant.

To lower the thermal noise floor,  $R_{IN}$  must be reduced, and therefore, a larger integration capacitor will be required in the 1<sup>st</sup> integrator, since the unity-gain frequency of the loop ( $f_{U}$ ) is limited by the switching frequency, as mentioned in Section 1.3.2.2. In contrast, Class-AB amplifiers do not suffer from this limitation, allowing the use of  $f_{U}$ 's above 10 MHz [60].

Due to the abovementioned limitations, the dynamic range of conventional monolithic Class-D audio amplifiers is lower than that of their Class-AB counterparts, around 110 dB for analog-input designs [15], [35], [39], [61], [62] and up to about 115 dB for digital-input designs [16], [17], [48], [49].

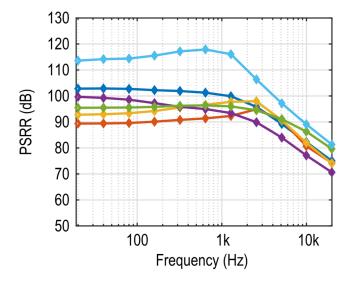

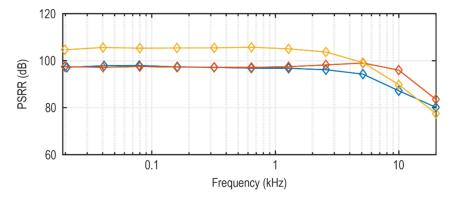

# 1.3.4 Power Supply Rejection Ratio (PSRR)

Since the CDA's output transistors operate as switches, supply noise directly couples to the output. For an open-loop CDA, the supply is essentially multiplied by the ideal output waveform. Hence, the rejection of power supply noise depends on the input level, the modulation scheme (e.g., AD vs. BD), and whether an SE or BTL output stage is used. As mentioned in Section 1.3.3, supply noise appears as CM in a BTL configuration when there is no input. However, the PSRR significantly decreases for large input signals and approaches only 3 dB for a full-scale input [58].

For closed-loop CDAs, on the other hand, supply noise at the output is suppressed by the loop gain. Nevertheless, mismatches in the feedback network can cause CM-to-differential leakage and limit the PSRR. Therefore, the PSRR can be improved by regulating the output CM with a CMFB loop

[17], [63]. Digital-input CDAs employing a current DAC also exhibit high PSRR if there is no CM voltage drop across the feedback resistors [16].

# 1.4 Thesis Goal and Organization

As introduced in Section 1.1, CDAs suffer from greater EMI, inferior linearity, and lower DR than Class-AB amplifiers. Since most audio sources are digital, Table 1.2 summarizes and compares the performance of state-of-the-art digital-input audio drivers at the start of the research described in this thesis. As shown, the THD+N of CDAs is significantly higher than those of Class-AB amplifiers, and few CDAs satisfy the stringent automotive EMI standard of CISPR 25 Class 5 EMI. Although EMI can be improved by advanced PCB layout with extra supply decoupling, filtering, and shielding [64], these mitigation techniques inevitably increase the application cost. Given the necessity for high power efficiency in high-power applications, CDAs with small LC filters are desired to achieve an overall form factor close to that of Class-AB solutions [65].

|            | TI<br>PCM1794A<br>+ TPA6120A2 | SH. Wen [4]<br>ISSCC'19 | E. Cope [49]<br>ISSCC'18           | D. Schinkel [17]<br>JSSC'17        |

|------------|-------------------------------|-------------------------|------------------------------------|------------------------------------|

| Monolithic | No                            | Yes                     | Yes                                | Yes                                |

| Amp. Class | Class-AB                      | Class-AB                | Class-D                            | Class-D                            |

| THD+N      | -107 dB                       | -105 dB                 | -97 dB                             | -89 dB                             |

| DR         | >120 dB                       | 120 dB                  | 115.5 dB                           | 115 dB                             |

| PSRR       | 75 dB                         |                         | $80 \text{ dB} \sim 50 \text{ dB}$ | $88 \text{ dB} \sim 60 \text{ dB}$ |

| (Freq./Hz) | (N.A.)                        | -                       | $(20 \sim 20k)$                    | $(100 \sim 20k)$                   |

| Pout,max   | 0.7 W                         | 62 mW                   | 20 W                               | 80 W                               |

| Efficiency | -                             | -                       | 90%                                | >90%                               |

| Iq         | 70 mA                         | 3.8 mA                  | 20.5 mA                            | -                                  |

| EMI        | No                            | No                      | Yes                                | Yes                                |

| flc        | No                            | No                      | Not reported                       | ~40 kHz                            |

| Table 1.2. Comparison | between state-of-the-art | Class-AB and | Class-D amplifiers. |

|-----------------------|--------------------------|--------------|---------------------|

|                       |                          |              |                     |

In view of the abovementioned limitation of CDAs, this thesis describes the design and implementation of CDAs that aim to approach the performance

of Class-AB amplifiers in terms of their application cost (mainly for suppressing EMI), dynamic range, and linearity while retaining the characteristic high power efficiency of the CDA.

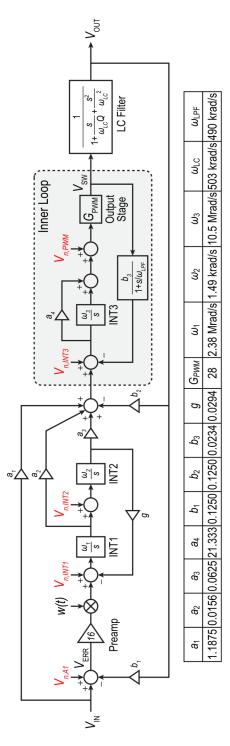

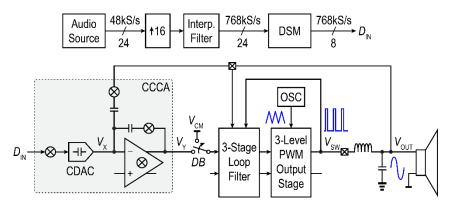

Chapter 2 presents a CDA with a 4.2 MHz constant-CM multi-level output stage that reduces the radiated EMI, a major issue in automotive applications, thus relaxing the requirements on its LC filter and reducing its size and cost. However, the filter must still be highly linear, which limits further cost and size reductions. To address this issue, **Chapter 3** describes a dual-loop architecture featuring feedback after the LC filter, thus suppressing its nonlinearity and ensuring that it no longer limits the linearity of the CDA. In this architecture, switching components in the feedback signal are also attenuated, enabling the implementation of the capacitively-coupled chopper CDA described in **Chapter 4**, which breaks the dynamic range limitation of conventional CDAs by obviating the need for noisy input resistors. **Chapter 5** extends this architecture to a digital-input CDA and presents design considerations to mitigate distortion due to DAC nonidealities and intermodulation. **Chapter 6** concludes this thesis and discusses potential directions for future works.

# References

- J. H. Huijsing, Operational Amplifiers: Theory and Design, 3 ed., Cham: Springer, 2017.

- [2] Texas Instruments, "TPA6120A2 High Fidelity Headphone Amplifier,"

[Online]. Available: <u>https://www.ti.com/product/TPA6120A2</u>

- [3] Texas Instruments, "PCM1794A 24-Bit, 192-kHz Sampling, Advanced Segment, Audio Stereo Digital-to-Analog Converter," [Online]. Available: <u>https://www.ti.com/product/PCM1794A</u>

- [4] S.-H. Wen, K.-D. Chen, C.-H. Hsiao, and Y.-C. Chen, "A -105dBc THD+N (-114dBc HD2) at 2.8V<sub>PP</sub> Swing and 120dB DR Audio Decoder with Sample-and-Hold Noise Filtering and Poly Resistor Linearization Schemes," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 294-295.

- [5] S.-H. Wen et al., "A -117dBc THD (-132dBc HD3) and 126dB DR Audio Decoder with Code-Change-Insensitive RT-DEM Algorithm and Circuit Technique for Relaxing Velocity Saturation Effect of Poly Resistors," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech.* Papers, Feb. 2022, pp. 482-484.

- [6] X. Jiang, "Fundamentals of Audio Class D Amplifier Design: A Review of Schemes and Architectures," *IEEE Solid-State Circuits Magazine*, vol. 9, no. 3, pp. 14-25, Aug. 2017.

- [7] M. Berkhout, "An Integrated 200-W Class-D Audio Amplifier," *IEEE J. Solid-State Circuits*, vol. 38, no. 7, pp. 1198-1206, July 2003.

- [8] I. Mosely, P. H. Mellor, and C. Bingham, "Effect of dead time on harmonic distortion in class-D audio power amplifiers," *Electronics Letters*, vol. 35, no. 12, pp. 950-952, July 1999.

- [9] M. Berkhout, L. Breems, and E. van Tuijl, "Audio at low and high power," in *Proc. ESSCIRC*, Sept. 2008, pp. 40-49.

- [10] M. Berkhout, "Balancing Efficiency, EMI, and Application Cost in Class-D Audio Amplifiers," *Low-Power Analog Techniques, Sensors* for Mobile Devices, and Energy Efficient Amplifiers: Advances in Analog Circuit Design 2018, K. A. A. Makinwa, A. Baschirotto and P. Harpe, eds., pp. 315-337, Cham: Springer, 2019.

- [11] L. Dooper, and M. Berkhout, "A 3.4 W Digital-In Class-D Audio Amplifier in 0.14 μm CMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1524-1534, July 2012.

- [12] T. Kuo, S. Chien, J. Huang, Y. Chen, and Y. Lee, "A 2.4 mA Quiescent Current, 1 W Output Power Class-D Audio Amplifier With Feed-Forward PWM-Intermodulated-Distortion Reduction," *IEEE J. Solid-State Circuits*, vol. 51, no. 6, pp. 1436-1445, June 2016.

- [13] S. Chien, Y. Chen, and T. Kuo, "A Low Quiescent Current, Low THD+N Class-D Audio Amplifier With Area-Efficient PWM-Residual-Aliasing Reduction," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3377-3385, Dec. 2018.

- Y. Z. Qiu, S. H. Chien, and T. H. Kuo, "A 0.4-mA-Quiescent-Current, 0.00091%-THD+N Class-D Audio Amplifier With Low-Complexity Frequency Equalization for PWM-Residual-Aliasing Reduction," *IEEE J. Solid-State Circuits*, vol. 57, no. 2, pp. 423-433, Feb. 2021.

- [15] E. Gaalaas, B. Y. Liu, N. Nishimura, R. Adams, and K. Sweetland, "Integrated stereo  $\Delta\Sigma$  class D amplifier," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2388-2397, Dec. 2005.

- [16] A. Matamura *et al.*, "An 82-mW ΔΣ-Based Filter-Less Class-D Headphone Amplifier With -93-dB THD+N, 113-dB SNR, and 93% Efficiency," *IEEE J. Solid-State Circuits*, vol. 56, no. 12, pp. 3573-3582, Dec. 2021.

- [17] D. Schinkel *et al.*, "A Multiphase Class-D Automotive Audio Amplifier With Integrated Low-Latency ADCs for Digitized Feedback After the Output Filter," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3181-3193, Dec. 2017.

- [18] A. Matamura, N. Nishimura, and B. Y. Liu, "Filterless multi-level deltasigma class-D amplifier for portable applications," in *Proc. ISCAS*, May 2009, pp. 1177-1180.

- [19] Vehicles, boats and internal combustion engines Radio disturbance characteristics – Limits and methods of measurement for the protection of on-board receivers, CISPR, Geneva, Switzerland, Oct. 2016.

- [20] T. Karaca, and B. Deutschmann, "Electromagnetic evaluation of Class-D switching schemes," in 2015 11th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), 29 June-2 July 2015, pp. 113-116.

- [21] Electromagnetic compatibility of multimedia equipment Emission requirements, CISPR, Geneva, Switzerland, Mar. 2015.

- [22] Maxim Integrated, "25W/50W, Filterless, Spread-Spectrum, Stereo/Mono, Class D Amplifier," [Online]. Available: <u>https://www.maximintegrated.com/en/products/analog/audio/MAX970</u> <u>9.html</u>

- [23] M. A. Teplechuk, A. Gribben, and C. Amadi, "True Filterless Class-D Audio Amplifier," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 2784-2793, Dec. 2011.

- [24] L. Guo, T. Ge, and J. S. Chang, "A 101 dB PSRR, 0.0027% THD + N and 94% Power-Efficiency Filterless Class D Amplifier," *IEEE J. Solid-State Circuits*, vol. 49, no. 11, pp. 2608-2617, Nov. 2014.

- [25] T. Ge, H. He, L. Guo, and J. S. Chang, "A Direct Battery Hookup Filterless Pulsewidth Modulation Class D Amplifier With >100 dB PSRR for 100 Hz to 1 kHz, 0.005% THD+N and 16 μV Noise," *IEEE Trans. Power Electronics*, vol. 35, no. 1, pp. 789-799, Jan. 2020.

- [26] P. P. Siniscalchi, and R. K. Hester, "A 20 W/Channel Class-D Amplifier With Near-Zero Common-Mode Radiated Emissions," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3264-3271, Dec. 2009.

- [27] Texas Instruments, "Application Report SNAA050A Managing EMI in Class D Audio Applications," [Online]. Available: <u>https://www.ti.com/lit/pdf/snaa050</u>

- [28] M. Berkhout, "A 460W Class-D output stage with adaptive gate drive," *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, pp. 452-453, Feb. 2009.

- [29] J. Lee *et al.*, "An 8Ω 10W 91%-power-efficiency 0.0023%-THD+N multi-level Class-D audio amplifier with folded PWM," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 88-89.

- [30] S. Yu, and M. Tseng, "Optimal Control of a Nine-Level Class-D Audio Amplifier Using Sliding-Mode Quantization," *IEEE Trans. Industrial Electronics*, vol. 58, no. 7, pp. 3069-3076, July 2011.

- [31] S.-H. Yang *et al.*, "A low-THD class-D audio amplifier with dual-level dual-phase carrier pulsewidth modulation," *IEEE Trans. Industrial Electronics*, vol. 62, no. 11, pp. 7181-7190, Nov. 2015.

- [32] V. M. Antunes, V. F. Pires, and J. F. A. Silva, "Narrow pulse elimination PWM for multilevel digital audio power amplifiers using two cascaded H-bridges as a nine-level converter," *IEEE Trans. Power Electronics*, vol. 22, no. 2, pp. 425-434, Mar. 2007.

- [33] C. Cerutti, Multilevel class-D amplifier, US 8,330,541, 2013.

- [34] Analog Devices, "Digital 2.5 W, 5.1 V, Boost Class-D Audio Amplifier with Output Sensing," [Online]. Available: <u>https://www.analog.com/media/en/technical-documentation/data-sheets/SSM4567.pdf</u>

- [35] M. Høyerby, "A 2×70 W Monolithic Five-Level Class-D Audio Power Amplifier in 180 nm BCD," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 2819-2829, Dec. 2016.

- [36] D. Nielsen, A. Knott, and M. A. Andersen, "Multilevel inverter based class D audio amplifier for capacitive transducers," in *Proc. 16th European Conference on Power Electronics and Applications*, Aug. 2014, pp. 1-7.

- [37] S. Chien *et al.*, "An open-loop class-D audio amplifier with increased low-distortion output power and PVT-insensitive EMI reduction," in *Proc. IEEE CICC*, Sept. 2014, pp. 1-4.

- [38] Texas Instruments, "TAS6424-Q1 75-W, 2-MHz Digital Input 4-Channel Automotive Class-D Audio Amplifier With Load-Dump Protection and I2C Diagnostics," [Online]. Available: <u>https://www.ti.com/lit/gpn/tas6424-q1</u>

- [39] S. Karmakar *et al.*, "A 28-W, -102.2-dB THD+N Class-D Amplifier Using a Hybrid ΔΣM-PWM Scheme," *IEEE J. Solid-State Circuits*, vol. 55, no. 12, pp. 3146-3156, Dec. 2020.

- [40] M. Berkhout, "A class D output stage with zero dead time," in *IEEE Int.* Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2003, pp. 134-135.

- [41] L. Risbo, and C. Neesgaard, "PWM amplifier control loops with minimum aliasing distortion," in *Proc. 120th AES Conv.*, May 2006, pp. 1-15.

- [42] N. Anderskouv, K. Nielsen, and M. A. Andersen, "High-fidelity pulsewidth modulation amplifiers based on novel double-loop feedback techniques," in *Proc. 100th AES Conv.*, May 1996, pp. 1-17.

- [43] B. Putzeys, "Simple self-oscillating class D amplifier with full output filter control," in *Proc. 118th AES Conv.*, May 2005, pp. 1-8.

- [44] W. Yu, W. Shu, and J. S. Chang, "A low THD analog Class D Amplifier based on self-oscillating modulation with complete feedback network," in *Proc. ISCAS*, May 2009, pp. 2729-2732.

- [45] P. Adduci, E. Botti, E. Dallago, and G. Venchi, "Switching power audio amplifiers with high immunity to the demodulation filter effects," J. AES, vol. 60, no. 12, pp. 1015-1023, Dec. 2012.

- [46] M. Sobaszek, "Self-Tuned Class-D Audio Amplifier With Post-Filter Digital Feedback Implemented on Digital Signal Controller," *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 67, no. 3, pp. 797-805, Mar. 2020.

- [47] M. Berkhout, and L. Dooper, "Class-D Audio Amplifiers in Mobile Applications," *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 57, no. 5, pp. 992-1002, 2010.

- [48] T. Ido, S. Ishizuka, L. Risbo, F. Aoyagi, and T. Hamasaki, "A Digital Input Controller for Audio Class-D Amplifiers with 100W 0.004% THD+N and 113dB DR," in *IEEE Int. Solid-State Circuits Conf.* (ISSCC) Dig. Tech. Papers, Feb. 2006, pp. 1366-1375.

- [49] E. Cope et al., "A 2×20W 0.0013% THD+N Class-D audio amplifier with consistent performance up to maximum power level," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 56-58.

- [50] M. Auer, and T. Karaca, "A Class-D Amplifier with Digital PWM and Digital Loop-Filter using a Mixed-Signal Feedback Loop," *Proc. ESSCIRC*, pp. 153-156, Sept. 2019.

- [51] S. Pavan, R. Schreier, and G. C. Temes, "Circuit Design for Continuous - Time Delta - Sigma Modulators," Understanding Delta-Sigma Data Converters, p. 304, Piscataway, NJ, USA: IEEE Press, 2017.

- [52] L. Risbo, R. Hezar, B. Kelleci, H. Kiper, and M. Fares, "Digital Approaches to ISI-Mitigation in High-Resolution Oversampled Multi-

Level D/A Converters," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 2892-2903, Dec. 2011.

- [53] P. Payandehnia, T. He, Y. Wang, and G. C. Temes, "Digital Correction of DAC Nonlinearity in Multi-Bit Feedback A/D Converters: Invited tutorial," in *Proc. IEEE CICC*, Mar. 2020, pp. 1-8.

- [54] W. H. Sun, S. H. Chien, and T. H. Kuo, "A 121dB DR, 0.0017% THD+N, 8× Jitter-Effect Reduction Digital-Input Class-D Audio Amplifier with Supply-Voltage-Scaling Volume Control and Series-Connected DSM," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2022, pp. 486-488.

- [55] D. M. Lombardo, "High-Dynamic-Range, Low-Power Digital-Input Direct-PWM Class-D Amplifier," MSc. Thesis, Delft University of Technology, 2022.

- [56] F.-G. Zeng, Q.-J. Fu, and R. Morse, "Human hearing enhanced by noise," *Brain Research*, vol. 869, no. 1, pp. 251-255, June 2000.

- [57] C. J. Plack, and N. F. Viemeister, "Suppression and the dynamic range of hearing," *The Journal of the Acoustical Society of America*, vol. 93, no. 2, pp. 976-982, 1993.

- [58] M. Wang, X. Jiang, J. Song, and T. L. Brooks, "A 120 dB Dynamic Range 400 mW Class-D Speaker Driver With Fourth-Order PWM Modulator," *IEEE J. Solid-State Circuits*, vol. 45, no. 8, pp. 1427-1435, Aug. 2010.

- [59] S. Pavan, R. Schreier, and G. C. Temes, "Nonidealities in Continuous-Time Delta-Sigma Modulators," Understanding Delta-Sigma Data Converters, pp. 259-299, Piscataway, NJ, USA: IEEE Press, 2017.

- [60] N. Mehta, J. H. Huijsing, and V. Stojanović, "A 1-mW Class-AB Amplifier With -101 dB THD+N for High-Fidelity 16 Ω Headphones

in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 54, no. 4, pp. 948-958, Apr. 2019.

- [61] Texas Instruments, "TPA3255-Q1 315-W Stereo, 600-W Mono PurePath<sup>TM</sup> Ultra-HD Analog-Input," [Online]. Available: <u>https://www.ti.com/lit/gpn/tpa3255-q1</u>

- [62] W. Wang, and Y. Lin, "A 0.0004% (-108dB) THD+N, 112dB-SNR,

3.15W fully differential Class-D audio amplifier with Gmnoise cancellation and negative output-common-mode injection techniques," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 58-60.

- [63] W. Wang, and Y. Lin, "A 118 dB PSRR, 0.00067% (-103.5 dB) THD+N and 3.1 W Fully Differential Class-D Audio Amplifier With PWM Common Mode Control," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 2808-2818, Dec. 2016.

- [64] D. Reusch, and J. Strydom, "Understanding the Effect of PCB Layout on Circuit Performance in a High-Frequency Gallium-Nitride-Based Point of Load Converter," *IEEE Trans. Power Electronics*, vol. 29, no. 4, pp. 2008-2015, 2014.

- [65] Texas Instruments, "Automotive 4-Channel Class D Amplifier Reference Design for Head Unit," [Online]. Available: <u>https://www.ti.com/tool/TIDA-00573</u>

# Chapter 2 A –107.8 dB THD+N Low-EMI Multi-Level Class-D Audio Amplifier<sup>1</sup>

# 2.1 Introduction

As mentioned in Chapter 1, the EMI of CDAs typically has to be suppressed by a bulky LC filter to avoid interfering with AM radios, especially in automotive applications, which have stringent EMI requirements. Setting the PWM frequency above the AM band (150 kHz  $\sim$ 300 kHz and  $530 \text{ kHz} \sim 1.8 \text{ MHz}$ ) allows for a smaller LC filter at the expense of higher idle power [1], [2]. This chapter presents a CDA with a multi-level Class-D output stage. The modulation scheme establishes a fixed output CM voltage, which helps to reduce EMI since the emissions from the pair of output wires partially cancel each other out [3]. In [3], however, a negative dead time was required to ensure correct operation, increasing the gate driver's complexity, and its output CM was defined by a power-hungry resistive divider even with duty-cycling. Moreover, the second and third harmonics of its 500 kHz switching frequency fall within the AM band. As mentioned in Section 1.3.1, several other topologies realizing a multilevel output have been reported [4], [5], [6], [7], [8], [9], [10], [11], which requires external flying capacitors or supply voltages at the expense of a higher application cost.

In this work, an alternative topology is proposed, which does not require a complicated gate driver, power-hungry CM regulation circuitry, or flying capacitors. With a switching frequency of 4.2 MHz, the required LC filter

<sup>&</sup>lt;sup>1</sup> This chapter is based on the journal paper: H. Zhang *et al.*, "A High-Linearity and Low-EMI Multilevel Class-D Amplifier," *IEEE J. Solid-State Circuits*, vol. 56, no. 4, pp. 1176-1185, Apr. 2021.

cutoff frequency is significantly increased. Meanwhile, the increased idle power due to the high switching frequency is mitigated by a modulation scheme that has minimal switching activity during idling and a gate-charge reuse technique.

This chapter is organized as follows. Section 2.2 explains the proposed output stage architecture and modulation scheme. Section 2.3 describes the output stage's circuit implementation. Section 2.4 details the design of the prototype's signal-processing circuitry, including the loop filter and the pulse width modulator. Section 2.4 presents the measurement results, and Section 4.5 summarizes and concludes the chapter.

# 2.2 **Proposed Output Stage**

# 2.2.1 Topology

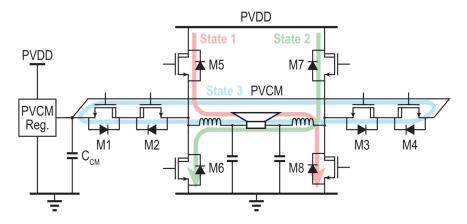

Fig. 2.1 shows the proposed fully differential multilevel output stage for a bridge-tied-load (BTL) [12]. Four CM output transistors (M1-M4) are added to the conventional H-bridge (M5-M8). A low-power linear regulator generates a voltage PVCM equal to half of PVDD. The output stage then produces three differential output levels ( $V_{OUTP} - V_{OUTN}$ ): +PVDD, -PVDD, and 0 in States 1, 2, and 3, respectively.

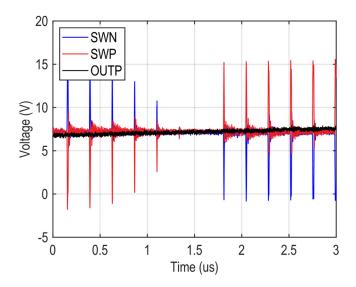

In State 1, M5, M8, M2, and M4 are turned on; in State 2, M6, M7, M1, and M3 conducts; and in State 3, M1-M4 are switched on. The output CM in all states is maintained at 1/2 PVDD, effectively reducing CM EMI, which is worse than DM EMI since the two output cables' emissions add in phase. The output stage switches between either State 1 and State 3, or State 2 and State 3. During the brief transition between State 1 and State 3, only M2 and M4 are on, and the body diodes of M1 and M3 provide a path for the inductor current to continue flowing. Similarly, the body diodes of M2 and M4 provide a path

for the inductor current during the transition between State 2 and State 3. Compared to [3], the proposed multilevel output stage does not require complex circuitry to avoid both dead time and cross-conduction. In contrast to [10], no complicated capacitor charge balancing circuitry is needed since, in State 3, the signal current only circulates within M1-M4. Thus, no signal current is drawn from PVCM, which can be maintained by a low-power linear regulator. Note that while idling, the output stage is mostly in State 3, which significantly reduces idle power.

Fig. 2.1. Circuit topology of the proposed multilevel output stage.

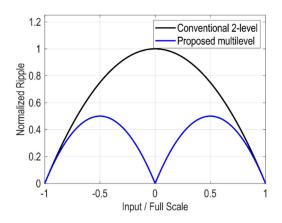

Introducing the extra output level reduces the output step size by half compared to traditional two-level PWM modulation, leading to significant EMI reduction. Although it is rather difficult to predict EMI by simulations, the ripple current injected into the load provides a relevant indication. With the same inductor, Fig. 2.2 compares the peak-to-peak output ripple current of a conventional two-level AD mode output stage and that of the proposed multilevel output stage. The conventional output stage generates the most ripple when there is no audio signal, while the proposed output stage produces the least in this situation, with a 2x lower peak amplitude, which is reached at half full-scale. As a result, the proposed output stage should have significantly better EMI performance since most audio signals have a high crest factor.

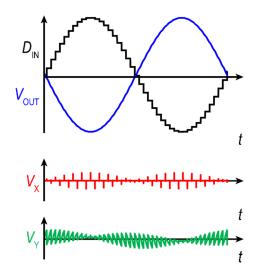

#### 2.2.2 Modulation Scheme

As mentioned in Section 1.2.3.1, fixed-frequency PWM creates tones at well-defined frequencies in the EMI spectrum, which can be placed above the AM band (150 kHz to 1.8 MHz). Although the CISPR 25 standard does not specify the maximum EMI between 1.8 MHz and 5.9 MHz, a certain limit might still be imposed by the application. Hence, this work employs fixed-frequency PWM switching at 4.2 MHz. For the same amount of attenuation, this allows the LC filter cutoff frequency to be 2x higher than that used in [1], [2], where  $f_{PWM}$  was set to 2 MHz. While a  $f_{PWM}$  of 4.2 MHz is possible for a CDA employing conventional AD modulation as in [1], [2] in the chosen 180 nm BCD process, analysis shows that the high switching frequency will increase the idle power significantly.

Multilevel operation facilitates low idle power by reducing switching losses. In this work, the voltage step size on the parasitic capacitance  $C_{\text{PAR}}$  at the output nodes is reduced by half, while  $C_{\text{PAR}}$  itself is increased by less than 50% since, as will be discussed in Section 2.3.6, M1-M4 are sized smaller than M5-M7. Therefore, the switching loss due to output capacitance, which is proportional to  $C_{\text{PAR}}V^2f_{\text{PWM}}$ , is reduced even when  $f_{\text{PWM}}$  is doubled. Gate charge loss for a small input is also reduced because the on-time of M5-M8 is too short for their  $V_{\text{GS}}$  to be fully charged; on the other hand, although the  $V_{\text{GS}}$ 's of M1-M4 are fully charged and discharged at  $f_{\text{PWM}}$ , they are sized smaller.

Fig. 2.2. Normalized peak-to-peak output ripple as a function of average output voltage for the proposed multilevel and conventional two-level output stages.

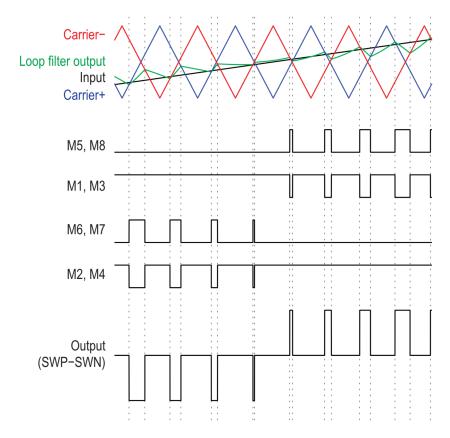

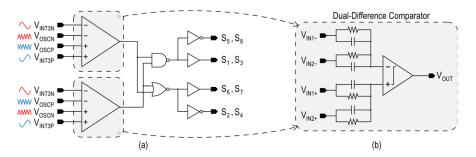

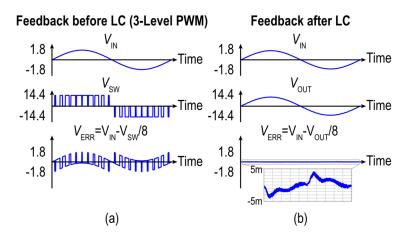

The proposed output stage generates three differential output voltages while the output CM stays at PVDD/2 to minimize CM EMI [3], [13]. To derive them, two triangular-wave carriers are employed, which are equal in amplitude but opposite in phase (Fig. 2.3), as in BD modulation (Section 1.2.3.1), since, differentially, both modulation schemes have three output levels. The loop filter output is then compared to the two triangular waves. When the input signal is above both carriers, the output stage switches to State 1, bringing the differential output to +PVDD; when the signal is between the two carriers, the output stage switches to State 3, creating a zero differential output; and when the signal is below both carriers, the output stage switches to State 2 to provide –PVDD. Since PWM pulses are now generated twice in each carrier cycle, a 2.1 MHz carrier frequency is used to operate the output stage at 4.2 MHz.

Fig. 2.3. Proposed modulation scheme, the resulting ON/OFF states of the output transistors, and differential output voltage.

# 2.3 Circuit Implementation

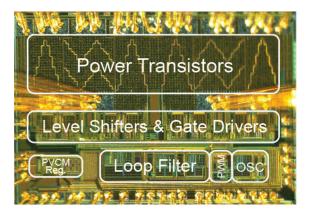

The proposed Class-D amplifier is implemented in a high-voltage BCD process, and its output stage is powered by a 14.4 V supply. To account for the extra voltage stress due to the supply ringing caused by off-chip parasitic inductances, the power transistors are all implemented as n-channel LDMOS transistors with 5 V gate oxide and a 20 V  $V_{DS}$  rating. This section describes the circuitry driving the output transistors and then discusses the design details of the gate-charge reuse technique, the power transistor driving

circuits, the sizing of the power transistors, and the implementation of the PVCM regulator.

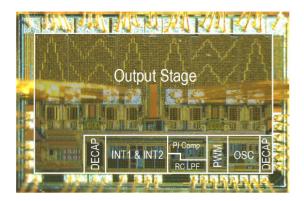

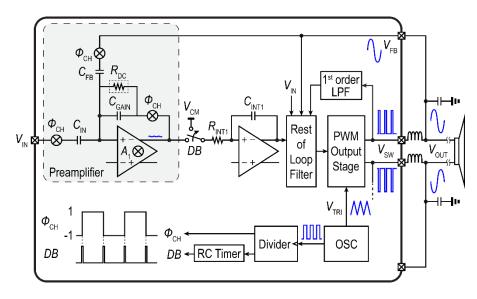

## 2.3.1 Overview

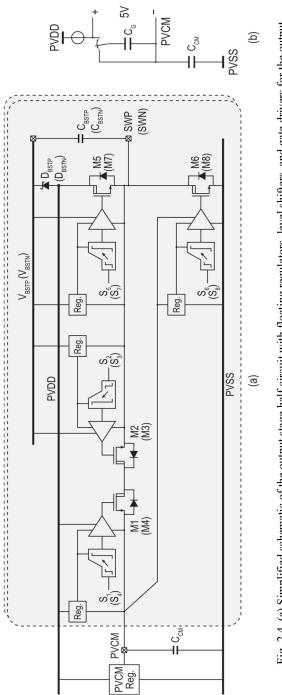

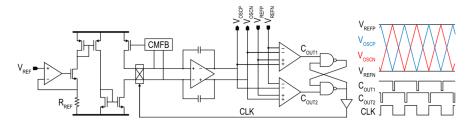

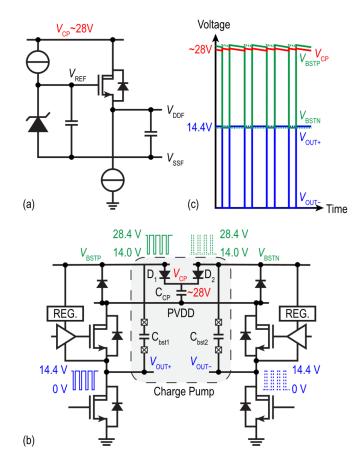

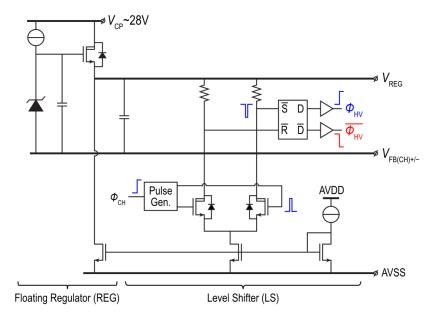

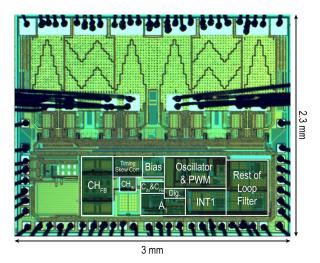

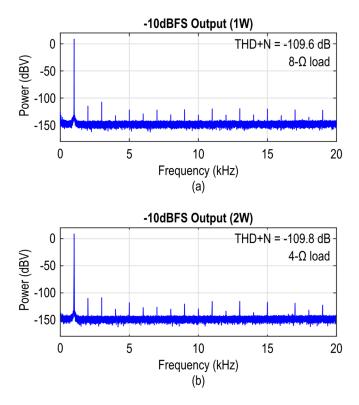

As shown in Fig. 2.4(a), the output stage consists of 8 power transistors (M1-M8) and their respective driving circuits, an external capacitor  $C_{CM}$  to hold the mid-rail level, and a PVCM regulator to maintain the voltage on C<sub>CM</sub>. Each output transistor is driven by a PWM signal generated by a 1.8 V PWM modulator (Section 2.4.2). This signal is then used to drive the transistor via a level shifter and a gate driver. The level shifter and the gate driver of each output transistor are powered by a floating regulator that provides a 5V local supply with respect to the source of each output transistor. M2, M3, M5, and M7 require local supplies above PVDD, which are obtained using external bootstrap capacitors C<sub>BSTP</sub> and C<sub>BSTN</sub> charged respectively through internal Schottky diodes D<sub>BSTP</sub> and D<sub>BSTN</sub>, as in [2], [14], [15], [16]. M2 and M5 (also M3 and M7) employ separate regulators to avoid crosstalk-induced timing errors due to voltage droop at the regulator outputs during gate charging. The gate drive for M1 and M4 is regulated from PVDD, while that for M6 and M8 is derived from PVCM. This configuration allows M6 and M8 to recycle the gate charge from M1 and M4 along with the bias current of their respective floating regulators, as will be explained further in Section 2.3.2. The PVCM regulator is a linear regulator which pre-charges C<sub>CM</sub> during startup and maintains it at mid-rail during normal operation.

### 2.3.2 Gate Charge Reuse

When M1 and M4 are switched on, C<sub>CM</sub> collects the current charging their gate-source capacitance. Effectively, the periodic charging and discharging of the gate-source capacitance of M1 and M4 create switched-capacitor resistors between PVDD and PVCM, charging C<sub>CM</sub>. Fig. 2.4(b) shows the equivalent circuit. This charge is then reused for the gates of M6 and M8. The proposed gate-charge reuse scheme not only reduces the gate charging loss but also alleviates the loading on the PVCM regulator, which now only needs to supply the difference between the gate-charge currents of M6, M8, and M1, M4. According to simulations, the idle power would increase by 14 mW if the low-side gate driver's power was simply derived from PVDD.

# 2.3.3 Floating Regulator

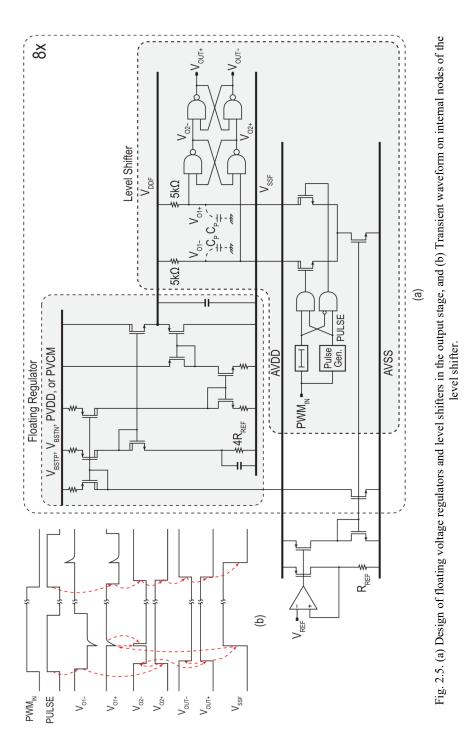

Fig. 2.5(a) shows the schematic of the floating regulator, similar to that in [2]. A current reference  $I_{REF}$  is derived by imposing a reference voltage (1.25 V) across a resistor  $R_{REF}$ , whose copies are routed to each floating regulator.  $I_{REF}$  flows through a 4x larger resistor of the same type in each regulator to create a scaled reference voltage of 5 V with respect to  $V_{SSF}$  in the floating domain, which is then buffered by a class-AB source follower that supplies the level shifter and gate driver. The matching of resistors and current source devices guarantees sufficient accuracy of the output voltage [2].

43

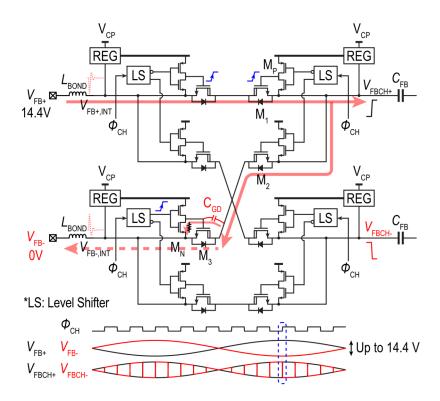

### 2.3.4 Level Shifter

Fig. 2.5(a) also shows the level shifter translating the PWM signal from the 1.8 V domain to the floating voltage domains. It consists of a resistor-loaded differential amplifier and a CM-immune two-stage NAND latch. During an output transition, one of the differential pair inputs is pulled high, creating a 5V voltage drop at the respective input of the floating-domain NAND latch, updating its output. The differential pair is only enabled momentarily by a pulse generator to reduce idle power. To avoid pulse width errors due to the pulse generator, a delay line before the AND gates at the input ensures that *PULSE* goes high before the input transition arrives at the differential pair. In the level shifters for M2, M3, M5, and M7,  $V_{\rm SSF}$  switches to the new output level with a slew rate of several V/ns after a transition propagates to the output transistor. As shown in Fig. 2.5(b), displacement current through the parasitic capacitance at nodes  $V_{01+}$  and  $V_{01-}$  can pull them down and lead to glitches on  $V_{02+}$  or  $V_{02-}$ . They are blocked by a second NAND latch, and thus, the level shifter output remains constant and correct during the slewing of  $V_{\rm SSF}$  . The input pulse is designed to extend beyond the  $V_{\rm SSF}$  transition so that the first latch's output is restored after the transition. The pulse generators in all 8 level shifters trigger during each output transition to guarantee the outputs of the 4 level shifters not switching (Fig. 2.3) are not accidentally flipped due to switching noise and bondwire ringing on nodes SWP and SWN.

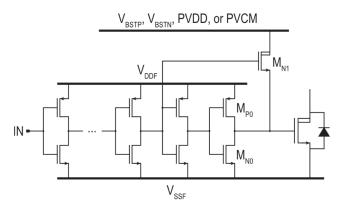

# 2.3.5 Gate Driver

Fig. 2.6 shows the gate driver design, which buffers the level shifter output and drives the output transistors. To reduce loading on the floating regulator, most of the gate charge is drawn from the floating regulator's input directly using a source follower  $M_{N1}$  [2], [16]. In the last stage, the pull-down strength

is chosen to be larger than the pull-up strength to avoid cross-conduction and to allow minimal dead time, which reduces the output stage distortion [15].

Fig. 2.6. Implementation of the gate driver.

# 2.3.6 Output Transistor Sizing

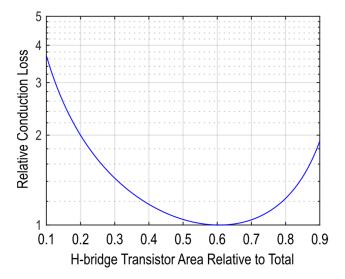

Multilevel output stages require additional output transistors that can drastically increase the overall area [3], [4], [6], [10]. At first sight, the on-resistance of M1-M4 should be 2x lower than that of M5-M8, such that the resistance between the output and any of the supply rails (PVDD, PVCM, and PVSS) would be the same. With the same type of transistor used, M1-M4 will occupy a 2x larger area compared to M5-M8. This is mitigated in the proposed output stage architecture. The ON duty cycle of the CM switches (M1-M4) is given by  $(1-|V_{IN}|/V_{IN,FS})$ , where  $V_{IN,FS}$  is the input full scale and  $V_{IN}$  is the differential input voltage between  $\pm V_{IN,FS}$ . Therefore, at high output power, as  $|V_{IN}|$  approaches  $V_{IN,FS}$ , the on-time of M1-M4 approaches zero. Fig. 2.7 shows the conduction loss as a function of relative sizing of M1-M4 and M5-M8 when the amplifier delivers a 10% THD clipped sine wave, representing the worst-case for conduction loss is minimized when M5-M8 occupy

60% of the total output transistor area. In this paper, the  $R_{\text{DS(ON)}}$  of M1-M4 is 210 m $\Omega$ , and that of M5-M8 is 140 m $\Omega$ .

Fig. 2.7. Conduction loss as a function of the area allocated for H-bridge transistors M5-M8 in the output stage when the amplifier delivers a 10%-THD clipped sine wave.

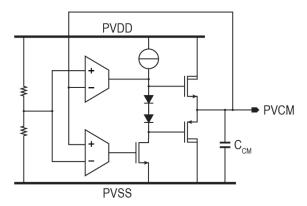

### 2.3.7 PVCM Regulator

As mentioned in Section 2.2, the PVCM regulator does not supply the load current. However, since M1 and M4 are sized differently from M6 and M8, the regulator must compensate for the difference between their gate charge, which is also signal-dependent. When the duty cycle of M1 and M4 is almost 100%, and the on-time of M6 and M8 is smaller than their gate voltages' rise time, a net current flows into PVCM. On the other hand, when the signal is large and since M1 and M4 have a smaller gate area, their gate charge is not enough to fully charge the gates of M6 and M8, and a net current flowing out of PVCM is required. To stabilize PVCM, the regulator uses a class-AB follower output stage to both source and sink current. Fig. 2.8 shows its implementation, where a resistor divider creates a mid-rail reference voltage,

which drives PVCM through a unity-gain buffer. It only draws 0.5 mA of quiescent current from PVDD.

Fig. 2.8. Implementation of the PVCM regulator.

# 2.4 Prototype Closed-Loop Class-D Amplifier

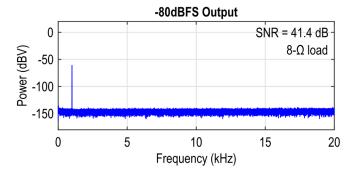

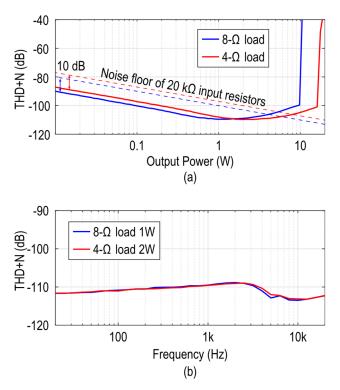

In closed-loop Class-D amplifiers, distortion in the output stage is suppressed by the loop gain, while noise and distortion introduced in the loop filter directly impact the overall performance. Therefore, the performance of the loop filter and the pulse width modulator is of critical importance. This section presents the design considerations and implementation details of the loop filter and the multilevel pulse width modulator.

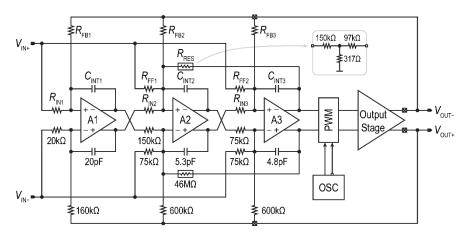

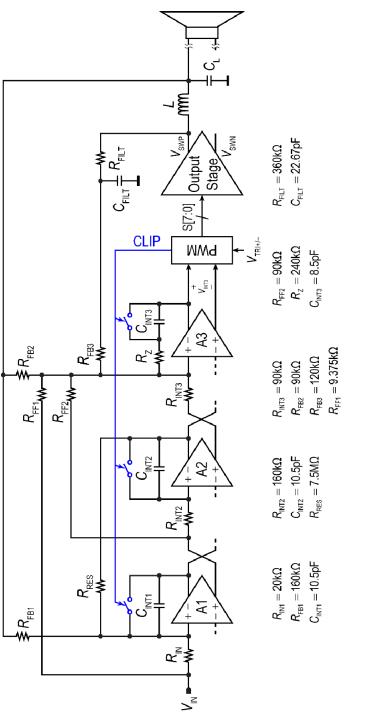

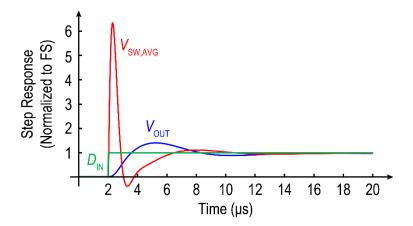

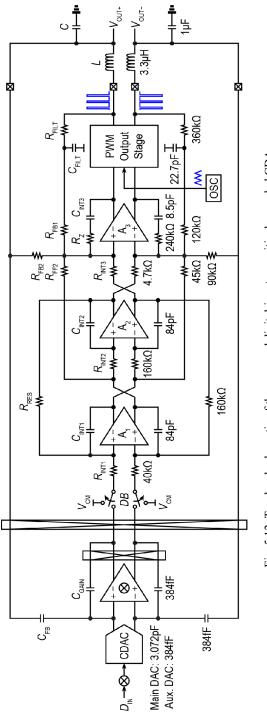

# 2.4.1 Loop Filter

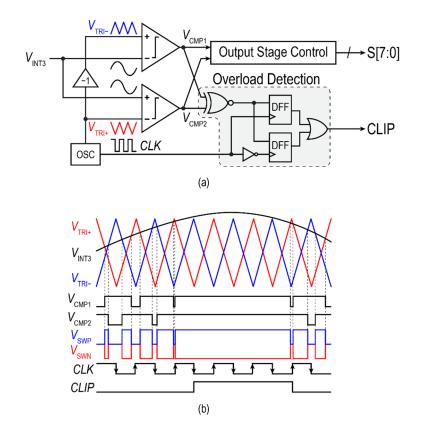

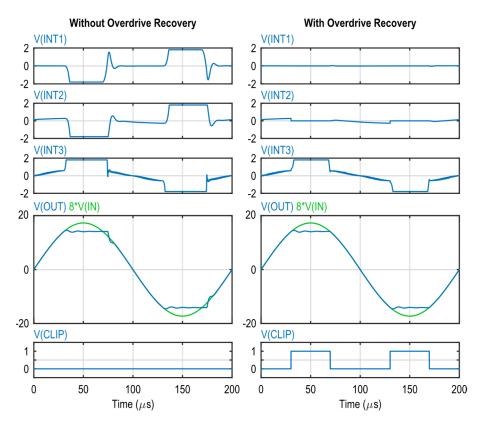

For Class-D amplifiers using fixed-frequency PWM, the maximum allowable bandwidth for stable operation is given by  $f_{SW}/\pi$ , which ensures that the slope of the modulator's input signal is always less than that of the modulating triangular waveform [17]. A loop bandwidth of 800 kHz is chosen to allow for sufficient stability margin, while a 3<sup>rd</sup>-order loop filter guarantees sufficient loop gain in the audio band. Fig. 2.9 shows a simplified schematic of the loop filter, where active-RC integrators employing polysilicon resistors

and metal-insulator-metal (MIM) capacitors are used for their superior linearity. The integration capacitors are built with switchable banks to compensate for the process variation of the RC time constant. A resonance at around 15 kHz is realized by local feedback through  $R_{RES}$  around the 2<sup>nd</sup> and 3<sup>rd</sup> integrators to boost the loop gain in the audio band to above 82 dB [18]. Extra input feed-ins into the 2<sup>nd</sup> and 3<sup>rd</sup> integrators via  $R_{FF1}$  and  $R_{FF2}$  guarantee low swing at the output of the first two integrators and improve their linearity. In particular, the 1<sup>st</sup> integrator processes the difference between the input and feedback signals. The feedback signal contains significant high-frequency components, including the PWM tones, sidebands, and their harmonics. Nonlinearity in the amplifier A1 results in intermodulation among these components, which is directly added to the input and leads to in-band distortion.

Fig. 2.9. Block diagram of the closed-loop Class-D amplifier.

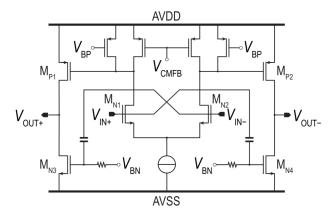

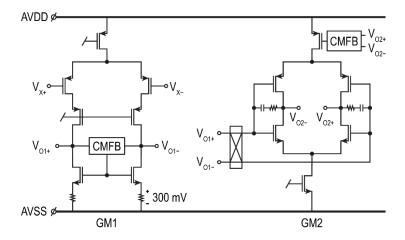

To mitigate this effect, a two-stage feedforward-compensated OTA instead of a conventional two-stage Miller-compensated OTA is employed, as shown in Fig. 2.10. Feedforward compensation is implemented by ac-coupling the inputs to  $M_{N3}$  and  $M_{N4}$  in the second stage [2]. This allows for 14 dB of extra gain at the switching frequency to suppress the intermodulation distortion

compared to a conventional Miller-compensated OTA without increasing the power consumption.

Fig. 2.10. The two-stage feedforward compensated OTA used in the loop filter.

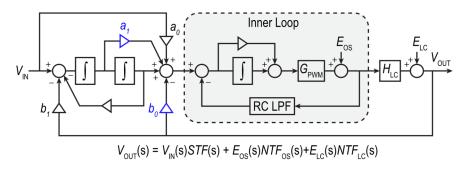

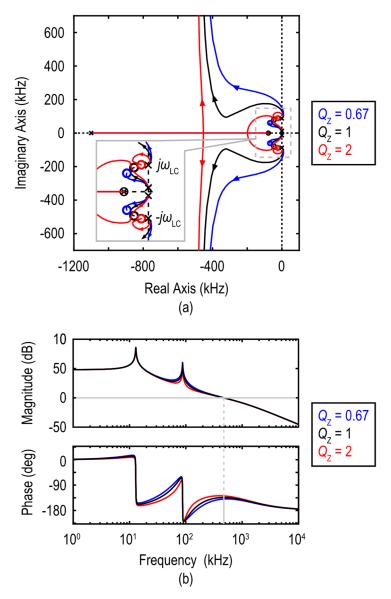

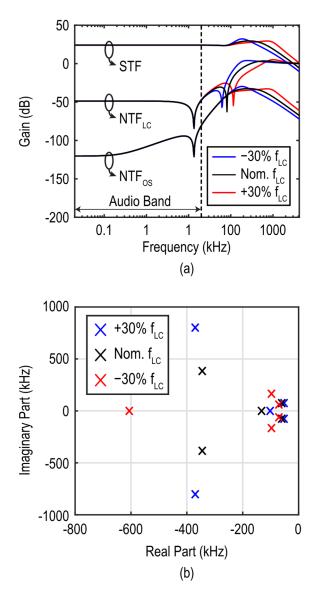

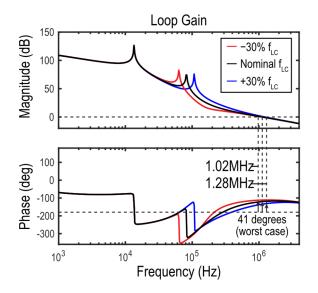

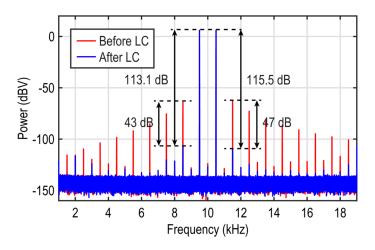

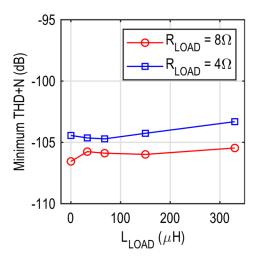

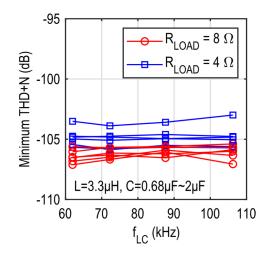

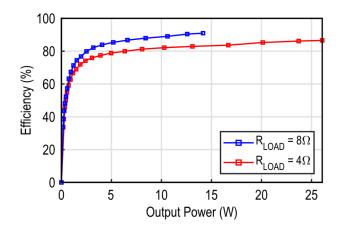

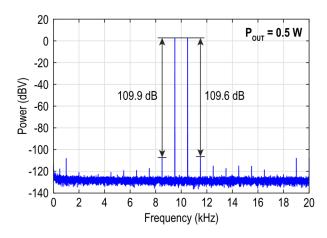

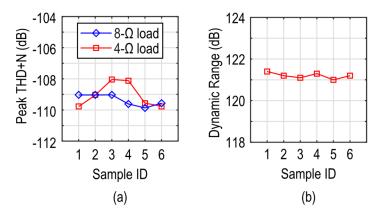

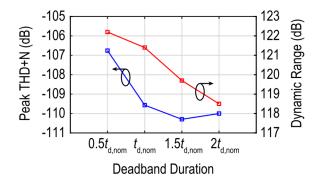

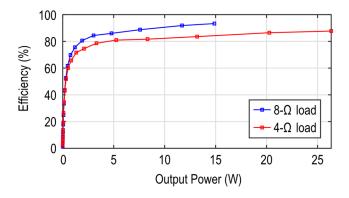

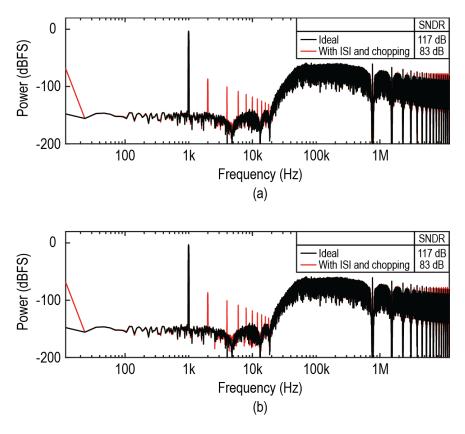

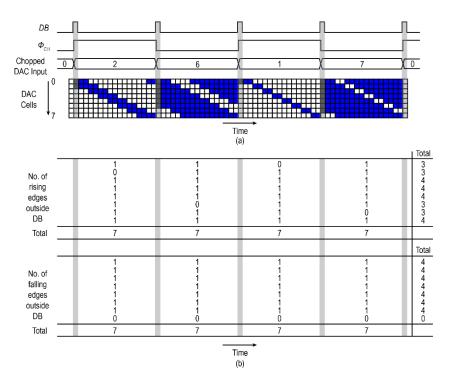

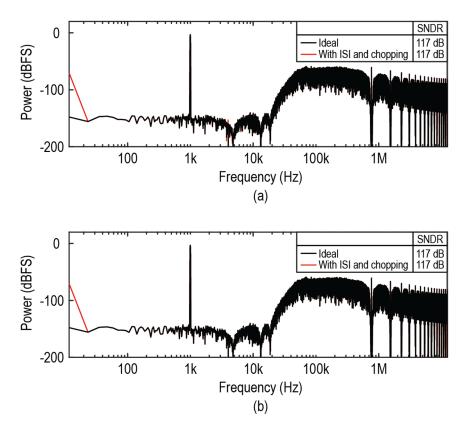

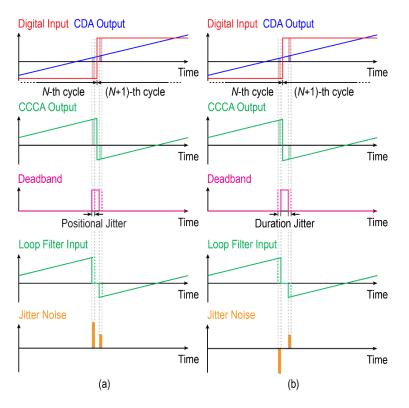

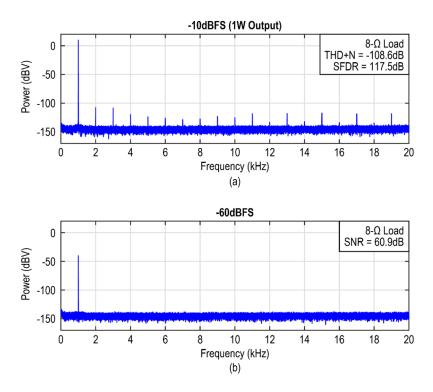

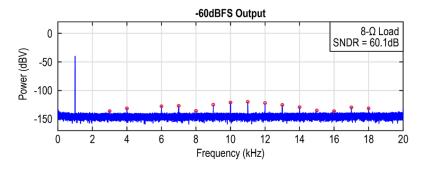

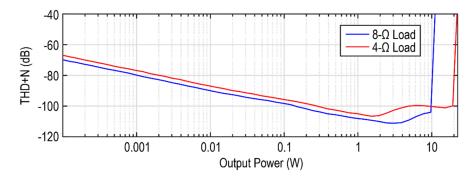

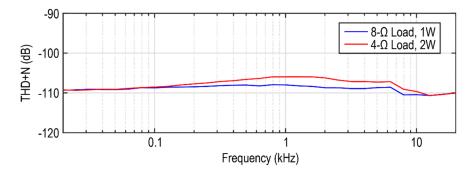

## 2.4.2 Pulse Width Modulator