# HW/SW Co-Design for Security Systems and the Investigation of Deep Learning-based Side-channel Analysis

Li, H.

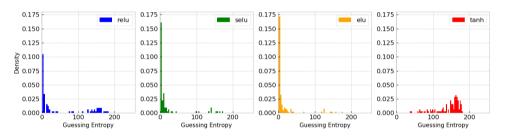

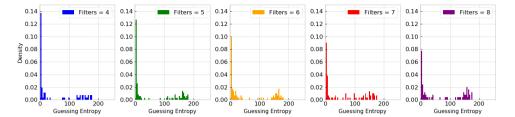

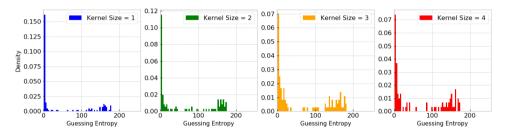

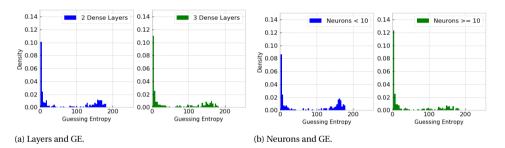

DOI

10.4233/uuid:8bdc75a9-2d88-42c6-92ac-88491ad41b61

**Publication date**

**Document Version**

Final published version

Citation (APA)

Li, H. (2024). HW/SW Co-Design for Security Systems and the Investigation of Deep Learning-based Side-channel Analysis. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:8bdc75a9-2d88-42c6-92ac-88491ad41b61

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

**Takedown policy**Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# HW/SW Co-Design for Security Systems and the Investigation of Deep Learning-Based Side-Channel Analysis

# HW/SW Co-Design for Security Systems and the Investigation of Deep Learning-Based Side-Channel Analysis

# Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus Prof.dr.ir. T.H.J.J.van der Hagen, chair of the Board for Doctorates to be defended publicly on Date 17 April 2024 at 12:30 o'clock

by

# Huimin LI

Master of Engineering in Micro-electromechanical Systems, Northwestern Polytechnical University, China, born in Guangyuan, China. This dissertation has been approved by the promoters.

## Composition of the doctoral committee:

Rector Magnificus, chairperson

Prof. dr. ir. R.L. Lagendijk, Delft University of Technology, promotor Dr. S. Picek, Delft University of Technology, copromotor

Radboud University, The Netherlands

*Independent members:*

Dr. S. Bhasin Nanyang Technological University, Singapore

Prof. dr. G. Smaragdakis Delft University of Technology

Prof. dr. L. Batina Radboud University, The Netherlands

Prof. dr. M. Conti Delft University of Technology & University of Padua, Italy

Prof. dr. P. Grosso University of Amsterdam, The Netherlands

Keywords: Electronic Systems, Security, HW/SW Co-design, Cryptographic Algo-

rithms, Trusted Execution Environments, Side-channel Analysis

*Printed by:* Ipskamp Printing

Front & Back: Wenjun Wang

Copyright © 2024 by Huimin Li

ISBN 978-94-6473-466-9

An electronic version of this dissertation is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

To my beloved family. Huimin Li

# **CONTENTS**

| St | ımm     | ary                                                                      | Хİ   |

|----|---------|--------------------------------------------------------------------------|------|

| Sa | ımen    | vatting                                                                  | xiii |

| Pa | ırt I I | ntroduction and Preliminary                                              | 1    |

| 1  | Intr    | roduction                                                                | 3    |

|    | 1.1     | Motivation                                                               | . 3  |

|    | 1.2     | Thesis Outline                                                           | . 4  |

|    |         | 1.2.1 Part I: Introduction and Preliminary                               | . 4  |

|    |         | 1.2.2 Part II: HW/SW Co-design for Security Systems                      | . 4  |

|    |         | 1.2.3 Part III: The Study of Deep Learning-based Side-channel Analysis . |      |

|    |         | 1.2.4 Part IV: Discussion                                                | . 11 |

|    | 1.3     | About the Thesis                                                         | . 11 |

|    | 1.4     | List Of Excluded Publications                                            | . 12 |

| 2  | Pre     | liminary                                                                 | 13   |

|    | 2.1     | Cryptography                                                             | . 13 |

|    |         | 2.1.1 Symmetric Cryptography                                             | . 14 |

|    |         | 2.1.2 Asymmetric Cryptography                                            | . 15 |

|    |         | 2.1.3 Hash Functions                                                     | . 15 |

|    |         | 2.1.4 Post-quantum Cryptography                                          | . 16 |

|    | 2.2     | Side-channel Analysis                                                    | . 16 |

|    |         | 2.2.1 Leakage Model                                                      | . 17 |

|    |         | 2.2.2 Non-profiled SCA and Profiled SCA                                  | . 18 |

|    |         | 2.2.3 Countermeasures                                                    | . 24 |

|    | 2.3     | Trusted Execution Environments                                           | . 25 |

|    | 2.4     | RISC-V Instruction Set Architecture                                      | . 25 |

|    | 2.5     | Vector Processing                                                        |      |

|    | 2.6     | Federated Learning                                                       |      |

|    |         | 2.6.1 Poisoning Attacks                                                  |      |

|    |         | 2.6.2 Privacy Attacks                                                    | . 31 |

|    | 2.7     | Summary                                                                  | . 32 |

| Pa | art II  | HW/SW Co-design for Security Systems                                     | 33   |

| 3  | A Sc    | calable SIMD RISC-V based Processor with Customized Vector Extensions    |      |

|    | for     | CRYSTALS-Kyber                                                           | 35   |

|    | 3.1     | Introduction                                                             | . 36 |

|    | 3.2     | Notation                                                                 | . 37 |

viii Contents

|   | 3.3  | Background                                                            | 38 |

|---|------|-----------------------------------------------------------------------|----|

|   |      | 3.3.1 Module Learning with Errors Problem                             | 38 |

|   |      | 3.3.2 CRYSTALS-Kyber                                                  | 38 |

|   |      | 3.3.3 Number Theoretic Transform                                      | 38 |

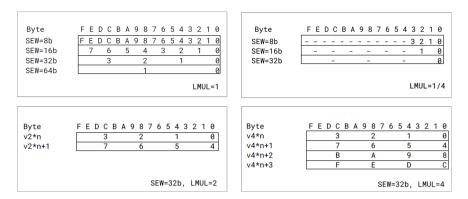

|   |      | 3.3.4 RISC-V Vector Extensions                                        | 39 |

|   |      | 3.3.5 Customize RISC-V Instructions                                   | 42 |

|   | 3.4  | The Design of An SIMD RISC-V Processor                                | 43 |

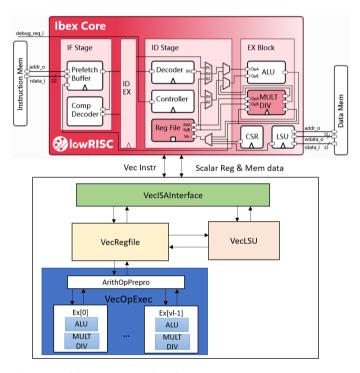

|   |      | 3.4.1 Scalar Core                                                     | 43 |

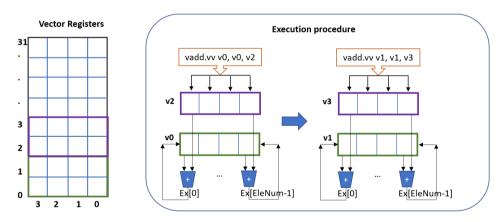

|   |      | 3.4.2 Vector Processing Unit                                          | 44 |

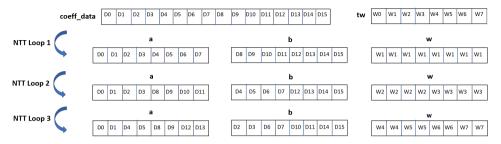

|   | 3.5  | The Design for Polynomial Multiplications in Crystal-Kyber            | 47 |

|   |      | 3.5.1 Register Pooling                                                | 47 |

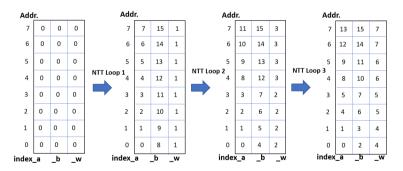

|   |      | 3.5.2 Automatic Index Generation                                      | 49 |

|   |      | 3.5.3 Customized Vector Instructions for NTT                          | 50 |

|   |      | 3.5.4 Optimization for Finite Field Arithmetic Operations             | 50 |

|   |      | Experimental Results                                                  | 51 |

|   | 3.7  | Summary                                                               | 52 |

| 4 | Max  | imizing the Potential of Custom RISC-V Vector Extensions for Speeding |    |

|   |      | SHA-3 Hash Functions                                                  | 55 |

|   |      | Introduction                                                          | 56 |

|   |      | Background                                                            | 57 |

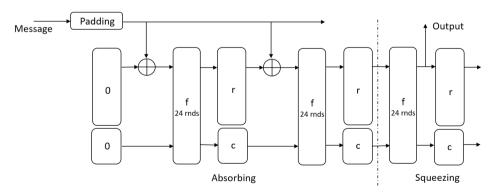

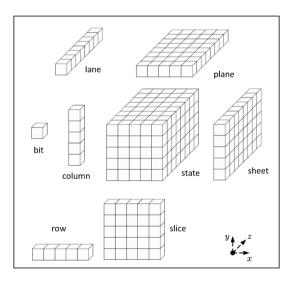

|   |      | 4.2.1 Keccak-f[1600] Permutation                                      | 57 |

|   |      | 4.2.2 Related Works                                                   | 58 |

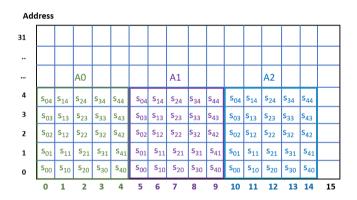

|   | 4.3  | System Design                                                         | 60 |

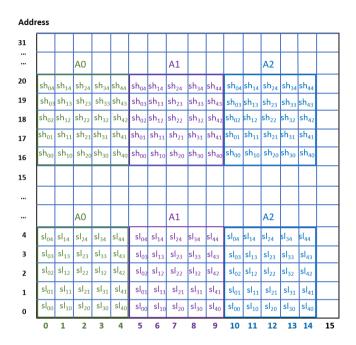

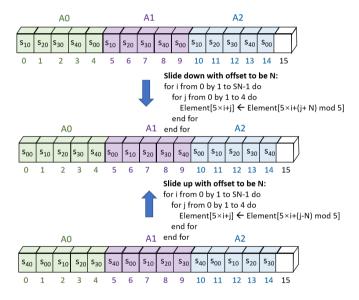

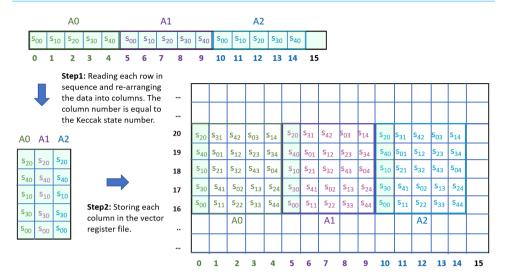

|   |      | 4.3.1 64-bit Architecture                                             | 61 |

|   |      | 4.3.2 32-bit Architecture                                             | 62 |

|   |      | 4.3.3 Custom Vector Extensions                                        | 63 |

|   | 4.4  | Implementations and Results                                           | 67 |

|   | 4.5  | Summary                                                               | 70 |

| 5 | ET A | IRS:FPGA-Accelerated Inference-Resistant & Secure Federated Learning  | 71 |

| J | 5.1  | Introduction                                                          | 73 |

|   | 5.2  | Background                                                            | 75 |

|   | 3.2  | 5.2.1 Federated Learning                                              | 75 |

|   |      | 5.2.2 Remote Attestation                                              | 76 |

|   |      | 5.2.3 TEEs on FPGAs                                                   | 76 |

|   |      | 5.2.4 Related Works                                                   | 77 |

|   | 5.3  | Problem Setting                                                       | 77 |

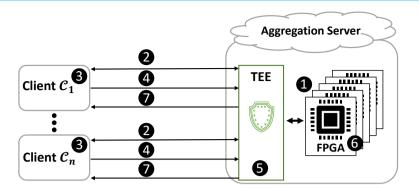

|   | 0.0  | 5.3.1 System Model                                                    | 77 |

|   |      | 5.3.2 Adversary Model                                                 | 77 |

|   |      | 5.3.3 Design of FLAIRS                                                | 78 |

|   | 5.4  | Design & Implementation.                                              | 80 |

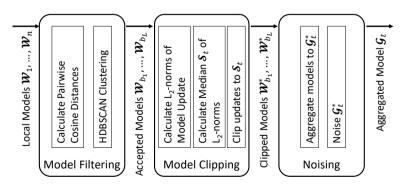

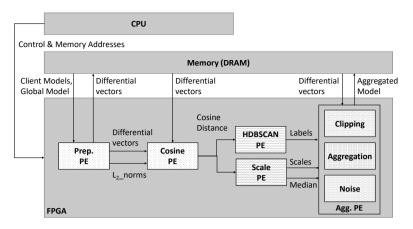

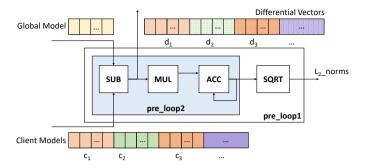

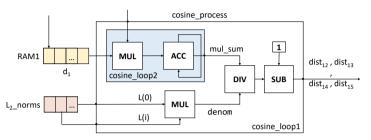

|   | 0.1  | 5.4.1 Analysis of FLAME Algorithm                                     | 80 |

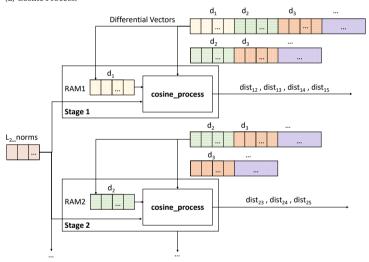

|   |      | 5.4.2 Implementation                                                  | 81 |

|   |      | 5.4.3 Evaluation                                                      | 85 |

|   | 5.5  | Summary                                                               | 86 |

|   |      |                                                                       | 55 |

CONTENTS ix

| Pa | rt III | The Investigation of Deep Learning-based Side-channel Analysis          | 87    |

|----|--------|-------------------------------------------------------------------------|-------|

| 6  | Ove    | erview of Recent Applications of Deep Learning to Profiled Side-channel |       |

|    | Ana    | ılysis                                                                  | 89    |

|    | 6.1    | Introduction                                                            | . 90  |

|    | 6.2    | Deep Learning-based SCA                                                 | . 91  |

|    |        | 6.2.1 Notation                                                          | . 91  |

|    |        | 6.2.2 Profiled SCA and Deep Learning                                    | . 92  |

|    | 6.3    | Recent Results in Deep Learning-based SCA                               | . 94  |

|    |        | 6.3.1 From Machine Learning to Deep Learning in SCA                     | . 94  |

|    |        | 6.3.2 Deep Learning Techniques in SCA                                   | . 95  |

|    | 6.4    | Advantages of Deep Learning for Profiled SCA                            | . 96  |

|    |        | 6.4.1 SCA without Preprocessing                                         | . 96  |

|    |        | 6.4.2 Bypassing Desynchronization                                       | . 97  |

|    |        | 6.4.3 Deep Neural Networks can Learn Second-order Leakages              | . 98  |

|    |        | 6.4.4 Take Advantage of the Domain Knowledge                            | . 99  |

|    |        | 6.4.5 Visualization Techniques to Identify Input Leakage                | . 100 |

|    | 6.5    | Metrics for Deep Learning-based Profiled SCA                            | . 101 |

|    | 6.6    | Tuning Neural Network Hyperparameters for SCA                           | . 102 |

|    | 6.7    | Different Applications of Deep Learning to SCA                          | . 105 |

|    | 6.8    | Summary and Perspectives                                                | . 106 |

| 7  | A C.   | omparison of Weight Initializers in Deep Learning-based Side-channel    |       |

| •  |        | omparison of weight initializers in Deep Learning-based side-channer    | 109   |

|    |        | Introduction                                                            |       |

|    | 7.2    | Background                                                              |       |

|    |        | 7.2.1 Weight Initializers                                               |       |

|    | 7.3    | Experimental Setup                                                      |       |

|    | 7.4    | Experimental Results                                                    |       |

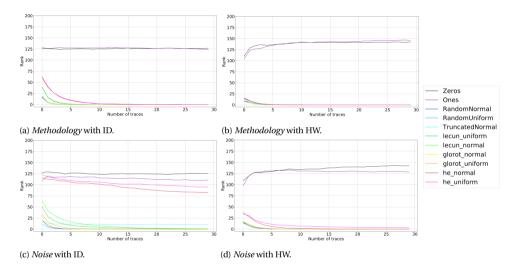

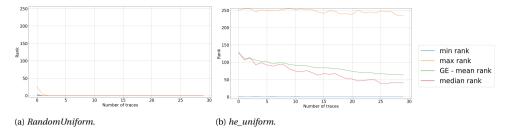

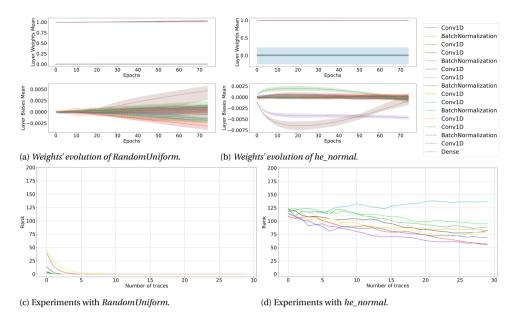

|    |        | 7.4.1 Results for the DPAv4.2 Dataset                                   |       |

|    |        | 7.4.2 Results for the AES_RD Dataset                                    |       |

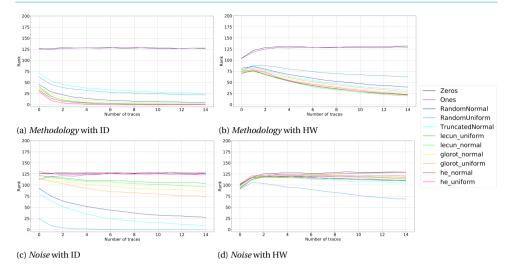

|    |        | 7.4.3 Results for the ASCAD Dataset                                     |       |

|    | 7.5    | Weight Initializer Influence on Other Hyperparameters                   |       |

|    | 7.6    | Summary                                                                 |       |

|    | 4.0    |                                                                         |       |

| 8  | A Sy   | ystematic Study of Data Augmentation for Protected AES Implementa-      | 125   |

|    |        | Introduction                                                            |       |

|    | 8.2    | Background                                                              |       |

|    | 0.2    |                                                                         |       |

|    |        | 8.2.1 Data Augmentation                                                 |       |

|    | 8.3    | Related Works.                                                          |       |

|    |        |                                                                         |       |

|    | 8.4    | Analysis Methodology                                                    |       |

|    |        |                                                                         |       |

|    |        | 8.4.2 Data Augmentation Hyperparameters                                 | . 133 |

X CONTENTS

|    | 8.5    | Experimental Results                                                    | 134 |

|----|--------|-------------------------------------------------------------------------|-----|

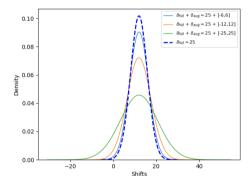

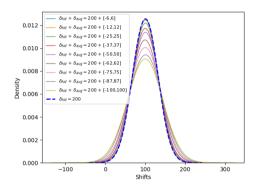

|    |        | 8.5.1 Desynchronization Countermeasure                                  | 134 |

|    |        | 8.5.2 Gaussian Noise Countermeasure                                     | 140 |

|    |        | 8.5.3 Discussion                                                        | 143 |

|    | 8.6    | Summary                                                                 | 147 |

| Pa | rt IV  | Discussion                                                              | 149 |

| 9  | Disc   | eussion                                                                 | 151 |

|    | 9.1    | Summary of Contributions                                                | 151 |

|    |        | 9.1.1 Implementation-related                                            | 151 |

|    |        | 9.1.2 SCA-related                                                       | 154 |

|    | 9.2    | Limitations                                                             | 156 |

|    |        | Future Works                                                            |     |

|    |        | 9.3.1 HW/SW Co-design for Other Cryptographic Algorithms with RISC-     |     |

|    |        | V Vector Extensions                                                     | 157 |

|    |        | 9.3.2 Extending Utilization of FPGA-based TEEs for More Trusted Com-    |     |

|    |        | puting Scenarios                                                        | 157 |

|    |        | 9.3.3 Investigation of the Potential Vulnerabilities of the SIMD RISC-V |     |

|    |        | Platform                                                                | 158 |

|    |        | 9.3.4 RISC-V Platform with Extensions to Mitigate SCAs                  | 158 |

| Ac | knov   | vledgements                                                             | 183 |

| Cu | ırricı | ılum Vitæ                                                               | 187 |

# **SUMMARY**

Electronic devices have permeated into all aspects of our lives, from basic smart cards to sophisticated hybrid automobile systems. These devices comprise a range of products like sensors, wearable gadgets, mobile phones, personal computers, and others, playing vital roles in many applications and enabling the Internet of Things (IoT). However, with this interconnectedness comes the associated security risks since attackers can exploit vulnerabilities in the system.

Securing electronic devices requires the use of cryptographic algorithms and trusted execution environments (TEEs). Cryptographic algorithms ensure data confidentiality and integrity through encryption/decryption, hashing, and digital signatures. TEEs provide secure enclaves within the system for critical operations that prevent unauthorized modifications and access by imposing stringent access restrictions. These two measures have become robust mechanisms for enhancing the security of critical operations and data access control.

Despite the above security measures, electronic systems are susceptible to various attacks, including side-channel analysis (SCA), in which attackers exploit information leakage from physical devices while executing instructions or cryptographic algorithms. Power consumption and electromagnetic radiation (EM) are common indicators of this leakage. Countermeasures such as masking and hiding techniques are commonly employed to enhance resistance against SCA. However, the advent of deep learning in SCA has brought forth new challenges, rendering previously efficient countermeasures ineffective. Moreover, deep learning-based SCA has the potential to eliminate preprocessing and alignment requirements inherent in earlier methods.

Therefore, this thesis focuses on two main objectives. The first objective is the implementation of cryptographic algorithms and the incorporation of TEEs for secure-sensitive applications. HW/SW co-design approach will be utilized to attain optimal performance while preserving flexibility. The second objective of this thesis is the investigation of deep learning-based SCA to explore its effectiveness in detecting side-channel vulnerabilities.

# SAMENVATTING

Elektronische apparaten hebben zich verspreid naar alle aspecten van ons leven, van eenvoudige smartcards tot geavanceerde hybride autosystemen. Deze apparaten omvatten een scala aan producten zoals sensoren, draagbare gadgets, mobiele telefoons, persoonlijke computers en andere, die een cruciale rol spelen in vele toepassingen en het Internet of Things (IoT) mogelijk maken. Echter, met deze onderlinge verbondenheid komen ook de bijbehorende beveiligingsrisico's, aangezien aanvallers kwetsbaarheden in het systeem kunnen misbruiken.

Het beveiligen van elektronische apparaten vereist het gebruik van cryptografische algoritmes en vertrouwde uitvoeringsomgevingen (Trusted Execution Environments, TEEs). Cryptografische algoritmes waarborgen de vertrouwelijkheid en integriteit van gegevens via encryptie/decryptie, hashing en digitale handtekeningen. TEEs bieden veilige enclaves binnen het systeem voor kritieke operaties die ongeautoriseerde wijzigingen en toegang voorkomen door strenge toegangsbeperkingen op te leggen. Deze twee maatregelen zijn robuuste mechanismen geworden voor het verbeteren van de beveiliging van kritieke operaties en data-toegangscontrole.

Ondanks bovengenoemde beveiligingsmaatregelen zijn elektronische systemen vatbaar voor diverse aanvallen, waaronder zijdelingse kanaalanalyse (Side-Channel Analysis, SCA), waarbij aanvallers informatie lekken uit fysieke apparaten tijdens het uitvoeren van instructies of cryptografische algoritmes. Energieverbruik en elektromagnetische straling (EM) zijn veelvoorkomende indicatoren van deze lekken. Robuuste tegenmaatregelen zoals maskering en verbergtechnieken worden vaak gebruikt om de weerstand tegen SCA te vergroten. Echter, de opkomst van deep learning in SCA heeft nieuwe uitdagingen met zich meegebracht, waardoor eerder efficiënte tegenmaatregelen ineffectief zijn geworden. Bovendien heeft op deep learning gebaseerde SCA het potentieel om voorbewerking en uitlijningsvereisten, die inherent zijn aan eerdere methoden, te elimineren.

Daarom richt deze scriptie zich op twee hoofddoelstellingen. De eerste doelstelling is de implementatie van cryptografische algoritmes en de integratie van TEEs voor veilige gevoelige toepassingen. De hardware/software co-design benadering zal worden gebruikt om optimale prestaties te behalen terwijl flexibiliteit behouden blijft. De tweede doelstelling van deze scriptie is het onderzoek naar deep learning-gebaseerde SCA om de effectiviteit ervan bij het detecteren van zijdelingse kanaal kwetsbaarheden te verkennen.

# PART I INTRODUCTION AND PRELIMINARY

1

# INTRODUCTION

# 1.1. MOTIVATION

In recent decades, electronic devices have become essential and integrated components that are indispensable in our daily lives. The devices encompass a spectrum that spans, from basic smart cards with a solitary microcontroller to advanced hybrid automobile systems, which integrate many units, peripherals, and networks. The aforementioned items include sensors, wearable gadgets, cell phones, personal computers, cloud computing platforms, household appliances, intelligent vehicles, medical equipment, etc. The importance of these devices has greatly increased due to their widespread integration into a wide range of applications, hence offering essential functionality and facilitating the implementation of automation capabilities. The emergence of the Internet of Things (IoT) has been facilitated by the ongoing development of these electronic systems, enabling the establishment of connections and communication.

Microcontroller Units (MCUs), Central Processing Units (CPUs), Application-Specific Integrated Circuits (ASICs), and Field Programmable Gate Arrays (FPGAs) facilitate the ability to customize and enhance a wide range of applications. Nevertheless, the incorporation of essential functionality also poses security concerns for designers. Adversaries can exploit potential vulnerabilities inside the system, resulting in data loss and system malfunctions. Attacks frequently focus on the manipulation and compromise of data transmission, data storage, execution processes, and system configurations, necessitating the implementation of robust security measures by designers.

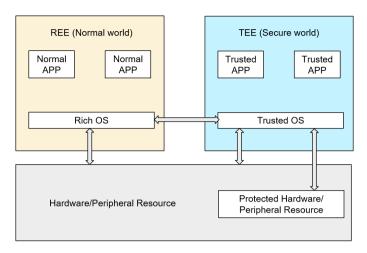

To enhance the security of various systems, it is crucial to employ cryptographic algorithms and trusted execution environments (TEEs). Cryptographic algorithms use mathematical processes that transform information into an incomprehensible format, thereby playing a pivotal role in upholding data confidentiality and integrity [1]. TEEs, also known as enclaves, provide a secure and isolated area within the system wherein critical operations can be executed with a high level of assurance [2]. By enabling strict access restrictions and safeguarding against unauthorized modifications, TEEs are capable of securing applications effectively [3]. This concept has emerged as a robust

mechanism for protecting critical operations, allowing data access exclusively to authorized programs possessing specific permissions. *Thus, the first goal of this thesis is implementation-related: implementing cryptographic algorithms and utilizing TEEs for security-sensitive applications.* Here, hardware/software (HW/SW) co-design is implemented in order to attain optimal performance while emphasizing timely design and adaptability.

Even though electronic systems may be protected by the aforementioned measures, they remain vulnerable to various types of attacks, among which is side-channel analysis (SCA) [4]. SCA is categorized as an implementation attack, wherein adversaries shift their focus from directly targeting algorithms to exploiting vulnerabilities, which are inherent in the physical devices responsible for algorithm execution. These attacks take advantage of unintentional information leakage from various sources. This study concentrates on utilizing power consumption and electromagnetic radiation (EM) as indicators of information leakage, during the execution of security-related instructions or cryptographic algorithms [4]-[6]. To enhance resistance against SCA, it is common practice to employ countermeasures, such as masking and hiding techniques. However, the emergence of deep learning in SCA has brought about new challenges. Certain countermeasures that were previously considered efficient are no longer effective [7], [8]. Additionally, deep learning-based SCA has the potential to eliminate the preprocessing and alignment requirements inherent in earlier SCA methods [9]. Consequently, the second goal of this thesis is SCA-related: the investigation of deep learning-based SCA to explore its effectiveness in detecting side-channel vulnerabilities.

# 1.2. THESIS OUTLINE

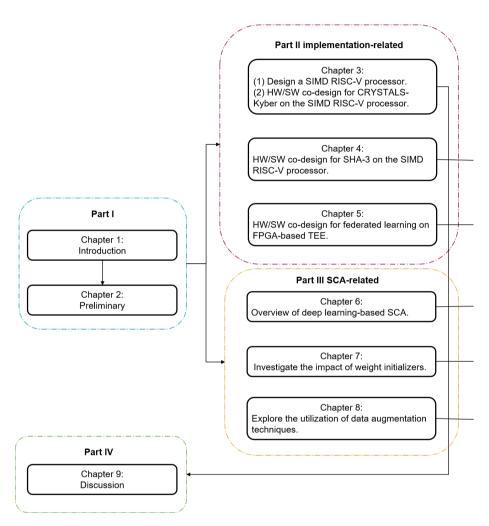

As mentioned in Section 1.1, the primary focus of this thesis revolves around two main objectives: the utilization of HW/SW co-design for the development of security systems (*implementation-related*) and the investigation of deep learning-based SCA (*SCA-related*). The entire thesis comprises four parts as illustrated in Figure 1.1.

### 1.2.1. PART I: INTRODUCTION AND PRELIMINARY

Part I consists of two chapters that establish the foundation for the research works. Chapter 1, titled "Introduction," illuminates the significance of the undertaken research, provides insights into the motivation behind the works, and outlines the structure of the thesis. Chapter 2, "Preliminary," presents an overview of the relevant background information necessary for understanding the proposed research works.

## 1.2.2. PART II: HW/SW CO-DESIGN FOR SECURITY SYSTEMS

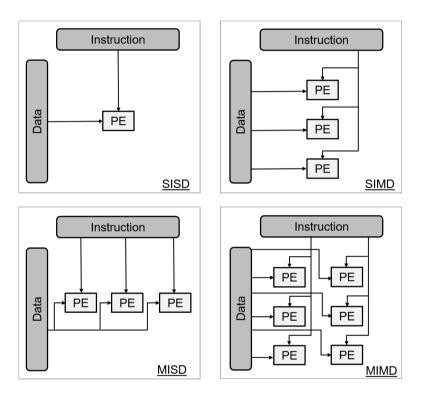

In the realm of system design, three distinct techniques have emerged, namely software (SW) design, hardware (HW) design, and hardware/software (HW/SW) co-design [10], [11]. Each method has unique characteristics and serves specific purposes within the specified field.

The SW design strategy involves the full implementation of a system using software executed on processors or computer platforms (i.e., CPUs or MCUs). SW design offers considerable flexibility, making it a highly appropriate choice for ap-

Figure 1.1: Thesis Outline.

plications that stress adaptability and expedited development cycles. The usage of processors inside a particular system allows for the implementation of software design, which empowers developers to leverage the functionalities of programming languages, libraries, and frameworks to create complex software solutions [12]. The intrinsic flexibility of software programs enables straightforward adaption to certain processors. However, a notable challenge in the implementation of software is the substantial latency that occurs when doing computations at the level of individual words. Furthermore, it is crucial to acknowledge that all processes rely on a pre-established set of instructions. In numerous instances, the execution of software design may not exhibit optimality in effectively managing intricate system activities.

- HW design is designed solely using dedicated hardware components. The present methodology capitalizes on the inherent advantages of hardware, such as its ability to perform speedy processing and efficient parallel operations. The incorporation of hardware components such as FPGAs or ASICs in the HW design showcases exceptional performance and computing capabilities, hence significantly enhancing the overall efficiency of the system to unparalleled extents. On one hand, hardware design entails a significant level of complexity in terms of its design intricacies, accompanied by substantially higher costs and longer time-to-market periods [13]. However, it is important to note that these increased costs come with improved performance, which may be desirable in some applications. Currently, there is a prevalent utilization of hardware designs in high-end cloud server applications. For instance, machine learning accelerators are implemented as cloud services on servers [14].

- HW/SW co-design integrates the beneficial aspects of hardware and software design methodologies. The process of HW/SW co-design involves the partitioning of the complete system into two distinct entities: a hardware component and a software component. The hardware part, which usually uses FPGAs or ASICs, takes advantage of the built-in computing power and high efficiency of specialized hardware. Concurrently, the software component is located within one or many processors. There are two types of processors: hard-core and soft-core. Hard-core processors are integrated within System-on-Chip (SoC) FPGAs or connected to ASIC chips, while soft-core processors often utilize FPGA resources, such as Xilinx MicroBlaze, Intel Nios II, and open-source RISC-V core, for the purpose of building processors [15]–[17]. The use of HW/SW co-design methodology provides the necessary flexibility and adaptability required for effectively managing intricate systems and executing algorithms. This approach achieves the optimal balance of hardware efficiency and parallelism, combined with software modifiability.

Given the numerous benefits associated with HW/SW co-design, we have chosen to utilize this methodology for the development of security systems. The study is to leverage the advantages offered by parallelism, efficient processing, and flexibility, achieved through the integration of hardware and software components, to yield favorable outcomes.

Part II is dedicated to addressing the *implementation-related* objective and consists of three chapters. These chapters will explore the HW/SW co-design approach for security systems, leveraging both the RISC-V based platform and the SoC FPGA platform. Specifically, our focus will be on implementing cryptographic algorithms on the RISC-V based platform, as well as utilizing TEE for security-sensitive applications on the SoC FPGA platform to establish secure frameworks.

## HW/SW CO-DESIGN FOR CRYPTOGRAPHIC ALGORITHMS ON RISC-V PLATFORM

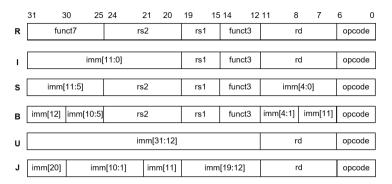

RISC-V is a freely accessible open-source Instruction Set Architecture (ISA) based on RISC principles. It offers a small base instruction set (base ISA) that is suitable for simplified general-purpose computers, as well as rich optional instruction extensions for more comprehensive applications [18]. These extensions are designed to work seamlessly with base ISA without conflicts. Additionally, RISC-V allows users to customize their instructions to accelerate specific applications, making it a versatile and adaptable architecture [18]. Among the many available extensions, RISC-V vector extensions are designed explicitly for vector operations. They enable multiple data to be processed simultaneously in a highly parallel manner under a single instruction. In Chapter 3 and Chapter 4, we will explore the potential of RISC-V vector extensions in cryptographic algorithms.

In Chapter 3, we first design a novel RISC-V based platform incorporating a scalable SIMD (Single Instruction Multiple Data) processor implemented in SystemVerilog to support RISC-V vector extensions. The designed processor not only supports RV32IMC but also integrates RISC-V vector extensions into its functionality. Additionally, it allows users to customize instructions to meet their specific application requirements. Next, we analyze the structure of the three polynomial multiplication algorithms in CRYSTALS-Kyber, namely NTT, INTT, and CWM. To optimize the HW/SW interface, we propose two techniques, called register pooling and automatic index generation. These techniques enhance the efficiency of data transfer between hardware and software components. Afterward, we proceed to customize vector extensions for CRYSTALS-Kyber multiplication and finite field operations. By tailoring the vector extensions to the specific needs of CRYSTALS-Kyber, we aim to maximize the performance of these cryptographic operations. Subsequently, we design the program for the three polynomial multiplication algorithms using the existing RISC-V instructions and the customized extensions. We then compare their performance with both the baseline implementations and the state-of-the-art HW/SW co-design using RV32IMC. The comparative analysis provides insights into the effectiveness of vector extensions in improving the overall performance of CRYSTALS-Kyber algorithms. Related publication:

• Li, Huimin, Nele Mentens, and Stjepan Picek. "A scalable SIMD RISC-V based processor with customized vector extensions for CRYSTALS-kyber." Proceedings of the 59th ACM/IEEE Design Automation Conference. 2022.

In Chapter 4, we utilize the SIMD RISC-V based processor designed in Chapter 3 to explore the utilization of vector extensions for implementing the Keccak-f[1 600] permutation in SHA-3 hash functions. Our investigation begins with a comprehensive analysis of the five-step mappings within the Keccak permutation. Based on this analysis,

8

1

we propose customized vector extensions specifically tailored for both 64-bit and 32-bit architectures. These custom instructions are realized in the SIMD processor using SystemVerilog, ensuring seamless integration and efficient execution. To further optimize the performance of the Keccak permutation, we develop programs that are specifically designed for both the 64-bit and 32-bit architectures. These programs leverage the custom vector instructions in conjunction with the existing RISC-V vector extensions. Subsequently, we conduct a comparative analysis of the performance achieved by our 32-bit architecture and the 64-bit architecture. Additionally, we compare the performance of our designs with existing parallelized implementations. These evaluations allow us to assess the effectiveness of vector extensions and their impact on overall performance for SHA-3 hash functions. Related publication:

• Li, Huimin, Nele Mentens, and Stjepan Picek. "Maximizing the Potential of Custom RISC-V Vector Extensions for Speeding up SHA-3 Hash Functions." 2023 Design, Automation & Test in Europe Conference & Exhibition (DATE). IEEE, 2023.

# HW/SW CO-DESIGN FOR PRIVACY-PRESERVING BACKDOOR-AWARE AGGREGATION FOR FEDERATED LEARNING ON FPGA-BASED TEE

The ongoing progress in FPGA technology has resulted in the emergence of SoC FPGAs, which offer a comprehensive framework for HW/SW co-design. These platforms facilitate the creation of highly customized systems that can effectively address various application needs. The reconfigurable characteristics of SoC FPGAs enable the development of specialized hardware accelerators that operate in conjunction with software executed on processors, leading to improved system performance and system flexibility. Moreover, SoC FPGAs provide the establishment of TEEs in order to guarantee the security of essential workloads. This includes the safeguarding of the FPGA configuration, which may include valuable Intellectual Property (IP) designs, as well as the protection of processed data while maintaining optimal performance.

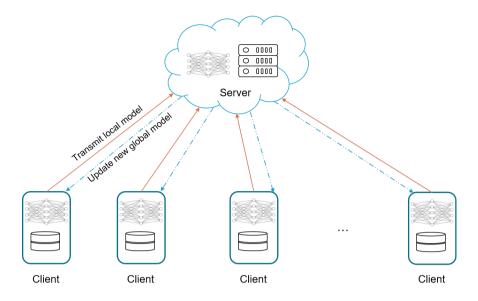

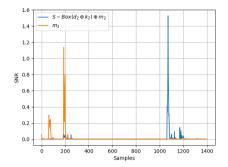

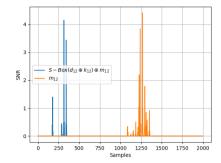

A prominent utilization scenario for FPGA-based TEEs involves the implementation of federated learning (FL). FL is a collaborative learning methodology that enables individual clients to independently train their own local deep neural network models and thereafter transmit solely the training parameters to a central aggregation server. Nevertheless, previous research has demonstrated that FL is susceptible to both backdoor attacks and inference attacks. In the first scenario, adversaries introduce modified updates into the process of aggregating data. In the second scenario, they exploit the local models from clients to infer their confidential information. Current methods aimed at mitigating the security challenges associated with FL exhibit either significant performance overheads, which render them inappropriate for practical implementation, or are tailored to tackle specific risks, such as defending against backdoor attacks or safeguarding privacy during aggregation.

In Chapter 5, given the limitations associated with existing solutions, we introduce a novel framework named FLAIRS, which leverages FPGA-based TEEs for the aggregation process of FL. Our framework is designed to address the performance bottlenecks commonly encountered in software-only solutions, while simultaneously providing defenses against backdoor and inference attacks. To demonstrate the efficacy of our approach, we implement a prototype that incorporates the defense mechanism known as FLAME, as

proposed in the recent publication by Nguyen et al. [19]. Our implementation involves a detailed analysis of the FLAME algorithm, and we realize the backdoor defense mechanism in FPGA to enhance operational efficiency. Additionally, we integrate FPGA-based TEEs as the privacy defenses against inference attacks. Subsequently, we conduct experiments to compare the performance of FLAIRS with FLAME in the original software context. These experiments are evaluated using the IoT-Traffic dataset and CIFAR-10 dataset. Finally, we compare the performance of our experiments with the original performance, offering an assessment of the advancements achieved through our proposed framework. Related publication:

- Li, Huimin, Phillip Rieger, Shaza Zeitouni, Stjepan Picek, Ahmad-Reza Sadeghi.

"FLAIRS: FPGA-Accelerated Inference-Resistant & Secure Federated Learning." 2023

33rd International Conference on Field-Programmable Logic and Applications (FPL).

IEEE, 2023.

- Shaza Zeitouni, Li, Huimin. FPGA-based Trusted Execution Environments and Their Use Cases. Crosscon: Cross-platform Open Security Stack for Connected Devices. December 14, 2023. https://crosscon.eu/blog/fpga-based-trusted-executionenvironments-and-their-use-cases.

# **1.2.3.** Part III: The Study of Deep Learning-based Side-channel Analysis

Cryptographic algorithms play an important role in safeguarding sensitive information, emphasizing the need to protect the private keys utilized in their software or hardware implementations. However, electronic devices are susceptible to a range of attacks, including side-channel analysis (SCA) [4]–[6]. Through SCA, adversaries can exploit vulnerabilities that arise during the execution of cryptographic algorithms, potentially compromising secret keys and exposing sensitive data. To address the consequences of SCA and establish comprehensive safeguards against breaches of confidentiality, it is crucial to prioritize the implementation of effective countermeasures. These countermeasures include various masking and hiding techniques aimed at mitigating the risk of sidechannel leakages and impeding adversaries from exploiting vulnerabilities.

Profiled SCA is considered the most powerful form of SCA and can be divided into two distinct phases [20]. In the profiling phase, adversaries obtain a clone device, collect side-channel traces, and analyze the physical leakages exhibited by these traces to characterize them. This process involves creating a template or statistical model that describes the patterns and characteristics present in the leaked data. Subsequently, in the attack phase, the adversary uses the collected side-channel traces from the targeted device along with the model created earlier to deduce the most likely correct key values.

However, ongoing research in the field of SCA consistently uncovers novel functionalities through the application of sophisticated methodologies. Deep learning has recently emerged as a prominent method in the realm of SCA, offering novel opportunities to exploit leakages in diverse systems. Deep learning-based SCA has the ability to overcome specific countermeasures that were previously considered impervious to conventional techniques [7], [8]. Furthermore, unlike traditional approaches in SCA that heavily rely on the selection of significant features and alignment processes, deep learning-

based SCA eliminates the need for such preprocessing steps [9]. To further explore the realm of deep learning-based SCA, Part III of this thesis, dedicated to the *SCA-related* objective, comprises three chapters focused on this subject.

In Chapter 6, we aim to provide a comprehensive overview of the current state-ofthe-art in deep learning-based SCA. Our chapter begins by establishing a foundational understanding of deep neural networks and profiled SCA. Subsequently, we conduct a survey of the latest advancements in utilizing deep neural networks for profiled SCA, highlighting their numerous advantages over traditional methods. Our primary objective is to underscore the potency of deep neural networks as viable alternatives to classical profiled attacks, such as Template Attacks (TAs) and traditional machine learning, which have long been recognized as highly effective in SCA. We emphasize the potential of deep learning techniques and their ability to outperform traditional approaches. Furthermore, our chapter delves into the appropriate interpretation of metrics when evaluating deep learning-based profiled SCA. Another aspect explored within our chapter is the fine-tuning of hyperparameters during the training of deep neural networks. We examine this problem in the specific context of profiled SCA, providing insights into optimizing network performance. Additionally, we describe various applications of deep learning in SCA, showcasing the adaptability of this approach across different scenarios. This highlights the wide range of possibilities for leveraging deep learning techniques in the SCA field. Lastly, our chapter concludes by providing a concise summary of directions for future research in the field of deep learning-based profiled SCA. Related publication:

Marina Krček, Li, Huimin, Servio Paguada, Unai Rioja, Wu, Lichao, Guilherme Perin, and Łukasz Chmielewski. "Deep learning on side-channel analysis." Security and Artificial Intelligence: A Crossdisciplinary Approach. Cham: Springer International Publishing, 2022. 48-71.

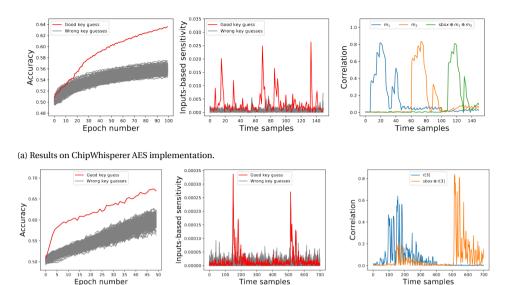

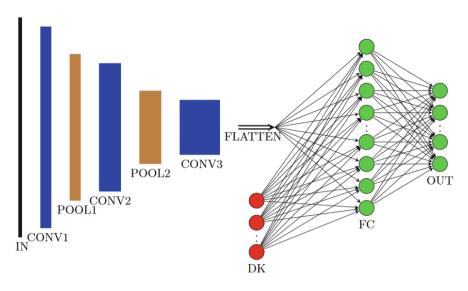

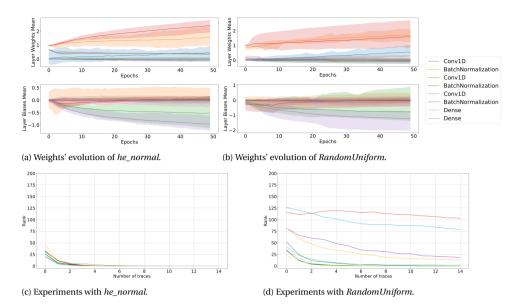

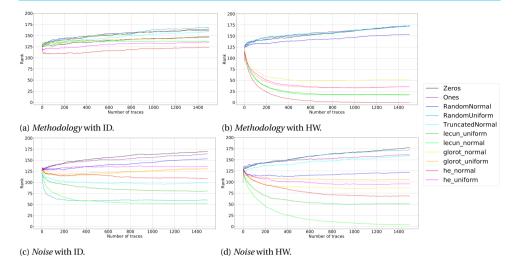

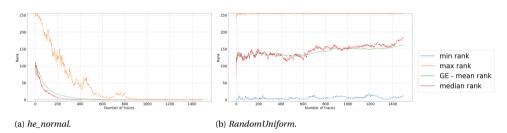

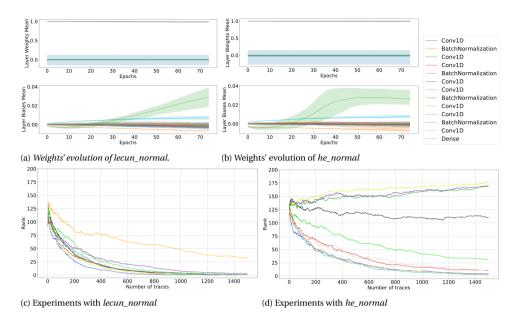

In Chapter 7, we focus on an investigation to understand the influence of weight initializers on the performance of deep neural networks within the realm of profiled SCA. The application of deep learning-based profiled SCA requires careful consideration of neural network hyperparameters. Recent publications have introduced various network designs as effective profiling methods against protected AES implementations, with different convolutional neural network (CNN) models showing comparable performance when applied to public side-channel trace databases. Our study focuses on a specific hyperparameter: the selection of different weight initializers directly responsible for the weight parameter. We aim to explore how these weight initializers impact the performance of the CNN architectures used, identify the most suitable initializer for a specific dataset and architecture, and determine whether a universal best weight initializer exists for all datasets. To achieve this, we evaluate a total of 11 weight initializers across three distinct datasets, two leakage models, and two CNN architectures. Our assessment of the weight initializers includes an examination of guessing entropy, result stability, and the evolution of weights during the training process. Related publication:

Li, Huimin, Marina Krček, and Guilherme Perin. "A comparison of weight initializers in deep learning-based side-channel analysis." Applied Cryptography and Network Security Workshops: ACNS 2020 Satellite Workshops, AIBlock, AIHWS, AIoTS,

Cloud S&P, SCI, SecMT, and SiMLA, Rome, Italy, October 19–22, 2020, Proceedings 18. Springer International Publishing, 2020.

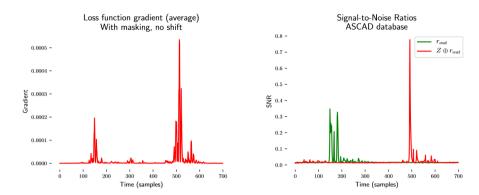

In Chapter 8, we conduct a series of systematic experiments to explore the advantages of using data augmentation techniques in the context of masked AES implementations enhanced with hiding countermeasures. The purpose of employing hiding countermeasures is to reduce the Signal-to-Noise Ratio (SNR) of measurements by introducing noise or desynchronization effects during cryptographic operations. In response to these protective measures, attackers employ signal processing methods such as pattern matching, filtering, averaging, or resampling. CNNs have demonstrated the ability to mitigate the impacts of countermeasures without necessitating trace preprocessing, particularly alignment, due to their shift-invariant property. Data augmentation techniques are also considered as a means to enhance the regularization capability of the network, thereby improving generalization and reducing attack complexity. To simulate a hiding countermeasure effect, we applied desynchronization and Gaussian noise to the original measurements. Initially, we introduce one of the aforementioned hiding countermeasures to the selected dataset. Subsequently, we conduct a hyperparameter search to identify the most effective CNN models capable of recovering the target key in a profiled attack scenario, even in the presence of added hiding countermeasures. Subsequently, to explore the optimal implementation of data augmentation for specific models, we carry out additional training for each CNN model. This involved considering various data augmentation techniques such as the number of augmented traces, as well as hyperparameters like the range of trace shifts for desynchronization or standard deviations for Gaussian noise. For each scenario, we test different desynchronization levels or noise levels to determine if there exists an optimal value that yields improved performance. Related publication:

• Li, Huimin, and Guilherme Perin. "A Systematic Study of Data Augmentation for Protected AES Implementations." Cryptology ePrint Archive (2023). (Under peer review)

### 1.2.4. PART IV: DISCUSSION

Part IV consists of a single concluding chapter titled "Discussion". This chapter offers a comprehensive summary of the thesis, including its contributions, limitations, and future works.

# **1.3.** ABOUT THE THESIS

This thesis comprises seven distinct publications, spanning from Chapter 3 to 8. The content in each chapter is essentially an expansion from one or two publications, or a derivation with minor modifications. The original titles of the publications are retained for most corresponding chapters. As these chapters are reproductions of previously published works, there may be some overlap in certain sections, such as the introduction, background, notations, and datasets, across multiple chapters.

12 1. Introduction

# 1.4. LIST OF EXCLUDED PUBLICATIONS

The following papers were published during the Ph.D. period but have been excluded as they fall outside the scope of the thesis. Related publication:

- Wu, Lichao, Léo Weissbart, Marina Krček, **Li, Huimin** and Guilherme Perin, Lejla Batina, and Stjepan Picek. "Label correlation in deep learning-based side-channel analysis." IEEE Transactions on Information Forensics and Security (2023).

- Mohamadreza Rostami, Chen, Chen, Rahul Kande, Li, Huimin, Jeyavijayan Rajendran, and Ahmad-Reza Sadeghi. (2024). "Fuzzerfly Effect: Hardware Fuzzing for Memory Safety." IEEE Security & Privacy (2024).

1

# 2

# **PRELIMINARY**

This chapter is structured as follows. Section 2.1 provides an introduction to cryptography. Section 2.2 presents preliminary information about side-channel analysis (SCA). Section 2.3 provides a review of trusted execution environments (TEEs). Section 2.4 introduces the RISC-V Instruction Set Architecture (ISA). Section 2.5 presents an overview of vector processing. Lastly, Section 2.6 introduces federated learning (FL), poisoning attacks, and privacy attacks.

## 2.1. CRYPTOGRAPHY

Cryptography, dating back over two millennia, is an ancient discipline with fundamental processes of encryption and decryption [21], [22]. Encryption is a process where a message is encoded in such a manner that it becomes incomprehensible to those who are not aware of the specific method (or keys) employed. The encrypted message is called ciphertext, while the unencrypted message is plaintext. The deciphering of the ciphertext to retrieve plaintext is referred to as decryption. Cryptographic algorithms today include intricate mathematical computations to ensure security within communication systems. Such applications render it highly improbable for a third party to obtain the original data without an increasing duration of time.

Contemporary communication has a significant focus on handling sensitive information, requiring features of confidentiality, identification, and data authentication [23]. The primary objective of cryptography is to maintain the confidentiality of transmitted data by preventing unauthorized parties from accessing it. Identification is possible through cryptographic techniques such as digital signatures [24], certificates [25], and secure protocols [26], which verify the authenticity and legitimacy of parties involved. Data authentication [27] plays a vital role in ensuring the validity and integrity of communicated data by preserving the content in its original unaltered state throughout transmission. Cryptographic hash functions and digital signatures are crucial in identifying and detecting any unauthorized alterations.

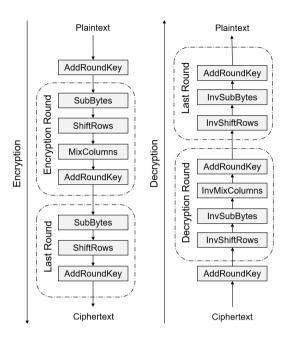

Figure 2.1: The Encryption and Decryption Process of AES [33], [34].

## 2.1.1. SYMMETRIC CRYPTOGRAPHY

Symmetric cryptography [28], also known as private key cryptography, is a technique that utilizes the same private key to both encryption and decryption operations. Symmetric cryptographic techniques that are frequently employed include the Data Encryption Standard (DES) [29] and the Advanced Encryption Standard (AES) [30]. The Data Encryption Standard (DES), which was adopted in 1977, was rendered vulnerable as a result of its relatively short key length of 56 bits. In order to tackle this concern, the introduction of Triple DES [31], also called 3DES, which is a form of DES that is cascaded three times, was proposed as a viable and secure solution. However, it should be noted that Triple DES could not fully satisfy the demands of forthcoming applications [32], prompting the National Institute of Standards and Technology (NIST) to initiate an open competition aimed at establishing a novel block cipher standard.

#### ADVANCED ENCRYPTION STANDARD

In 2001, the revelation of AES followed the conclusion of the above-mentioned NIST competition. After that, AES is widely acknowledged within the academic and industrial communities as a highly safe and efficient symmetric algorithm [34]. AES operates as a block cipher, processing fixed-length data blocks. During the encryption process, the plaintext input is divided into blocks of 128 bits, sequentially traversing multiple rounds. Each round uses a segment of the key, derived from a key schedule algorithm, where the original key generates several subkeys, one for each round. The selectable key sizes of 128, 192, or 256 bits correspond to the execution of 10, 12, or 14 rounds, respectively.

Figure 2.1 illustrates the sequence of operations within each round, comprising four

2

fundamental operations: SubBytes, ShiftRows, MixColumns, and AddRoundKey. SubBytes involves substituting bytes in the state matrix using a predefined substitution table (S-Box), enhancing confusion. ShiftRows manipulates bytes within the state matrix rows, ensuring diffusion. MixColumns performs a matrix multiplication operation on state matrix columns, augmenting diffusion and complicating the encryption process. AddRoundKey XORs each byte of the state matrix with a round key, injecting cryptographic strength derived from the expanded key schedule. Notably, the last round in AES excludes the MixColumns operation. The decryption process in AES mirrors the encryption process but employs inverse transformations for each step. The decryption structure in each round incorporates invShiftRows, invsubBytes, invMixColumns, and AddRoundKey functions, necessitating modifications in the key schedule to maintain this symmetry.

AES demonstrates exceptional performance across software and hardware platforms. It is widely utilized in diverse security frameworks and systems, such as WiFi-protected access [35], SSL/TLS protocols [36], and IoT environments [37]. This wide adoption underscores AES's prominence in contemporary cryptographic applications.

## 2.1.2. ASYMMETRIC CRYPTOGRAPHY

Symmetric cryptography can efficiently encrypt and decrypt data but encounters challenges in secure communication and signature validation due to inherent limitations [38], [39]. These challenges include secure key distribution, particularly in scenarios involving multiple pairs, resulting in complexities and scalability concerns in key management. Moreover, symmetric cryptography lacks mechanisms for partner authentication. To overcome these obstacles, the utilization of asymmetric cryptography [38], also referred to as public key cryptography, becomes relevant, such as Diffie-Hellman [40], Elliptic curve cryptography (ECC) [41] and Rivest-Shamir-Adleman (RSA) [42].

The concept of asymmetric cryptography refers to a cryptographic system that utilizes a pair of keys, namely a public key and a private key. The public key is widely accessible to all users and serves the purpose of encryption or signature verification, whereas the private key is securely held by its owner and is utilized for decryption or signature generation. The utilization of this cryptographic methodology facilitates the establishment of a safe data transmission channel between users, as the transmission is executed through the utilization of a unidirectional function. These algorithms can establish a mutually agreed-upon secret key between entities involved in communication, thereby facilitating subsequent communication through the utilization of efficient symmetric encryption techniques such as AES. Digital signature algorithms (DSA) are a distinct subset that employ a secret key to generate signatures and a public key to verify them, thereby guaranteeing the secrecy and integrity of digital communication.

### 2.1.3. HASH FUNCTIONS

In addition to symmetric and asymmetric cryptography, another fundamental category of cryptographic algorithms known as hash functions plays a significant role in modern cryptography [43], [44]. These functions are mathematical algorithms designed to transform messages of varying lengths into fixed-length values, commonly referred to as digest values or hash codes/values. Their fundamental objective lies in rendering it

2

computationally infeasible to deduce the original input that generated a specific hash value or to find two distinct messages that produce the same hash value. By generating a unique fixed-size output for each unique input message, hash functions facilitate the verification of data integrity during transmission and storage. Notably, these functions are extensively used in conjunction with other cryptographic methods, forming a vital component of digital signatures [45], message authentication codes (MACs) [46], and various security protocols. Well-known hash functions include the secure hash algorithms (such as SHA-1, SHA-2, and SHA-3), message-digest algorithms (such as MD4 and MD5), and Whirlpool [47].

## 2.1.4. POST-QUANTUM CRYPTOGRAPHY

Asymmetric cryptography, or public key cryptography, relies on complex mathematical problems that pose significant computational challenges. The security of cryptographic systems like RSA and ECC is based on computationally difficult tasks such as factorizing large integers and calculating discrete logarithms [48], [49]. These problems present considerable computational hurdles for conventional classical computers. However, the emergence of quantum computers poses a substantial threat to these public key algorithms. Quantum computers have the potential to perform calculations on a much larger scale, thereby challenging the security of existing cryptographic techniques. Shor's algorithm [48], [50], which falls under the category of quantum algorithms, demonstrates the capability to effectively solve these aforementioned problems. Although large-scale practical quantum computers are currently limited in availability, their development is anticipated in the coming decades [51], [52].

To address this imminent concern, there is a concerted effort to develop and deploy post-quantum cryptography (PQC) algorithms. The aim of PQC is to protect communication networks against attack from classical computers, and potential threats from quantum computers. NIST has initiated a competition focused on post-quantum cryptography [53]. The primary objective of this competition is to identify and establish secure PQC algorithms that can replace current asymmetric cryptography methods. PQC algorithms cover five different categories, including lattice-based cryptography [54], codebased cryptography [55], multivariate cryptography [56], hash-based encryption [56], and isogeny-based cryptography [57]. Lattice-based cryptography utilizes the mathematical framework of lattices to ensure security. Code-based cryptography employs error-correcting codes to establish cryptographic systems. Multivariate cryptography relies on multivariate polynomial equations to withstand different forms of attacks. Hashbased cryptography derives its security from the characteristics of cryptographic hash functions, making it resistant to attacks from quantum computers. Isogeny-based cryptography relies on problems involving isogenies of elliptic curves or other algebraic varieties to offer post-quantum security.

# 2.2. SIDE-CHANNEL ANALYSIS

Side-channel analysis (SCA) is a type of cryptography attacks that exploits system vulnerabilities by analyzing its physical properties [4], [5]. This thesis specifically focuses on power consumption and electromagnetic (EM) radiation as indicators of leakage when

executing security-related instructions or cryptographic algorithms. During the execution of these instructions or algorithms, sensitive variables that directly depend on the secret undergo manipulation as part of the computing tasks performed by devices. Changes in the status of registers, data buses, and memory, which typically have large capacitances, often result in significant fluctuations in power consumption or EM radiation [5], [58], which can disclose information about the circuit's calculations.

Malicious adversaries can exploit this information leakage from the actual implementation by analyzing the acquired traces. By understanding the relationship between the observed trace patterns and the corresponding instructions/operations, the secrets can be retrieved [59]. To obtain traces for digital exploitation and subsequent analysis, a carefully structured setup is necessary. This setup typically comprises devices serving as the platform for executing cryptographic algorithms, such as AES, a specialized probe employed to monitor power consumption or EM radiation, and a digital oscilloscope capable of observing, capturing, and storing variations in voltage levels. Ultimately, this procedure yields a set of recorded signals, collectively referred to as the "measurement". Each recorded signal is commonly known as a "trace," comprising a series of sample points. Adversaries can analyze a large dataset of traces, mitigate noise, and employ statistical methods to discern underlying patterns and extract sensitive information.

Let us consider a collection of traces, denoted as **T**, comprising of M traces. Each trace in  $T_i$  contains recorded data at N different time points. Therefore, **T** consists of elements  $t_{i,j} \in \mathbb{R}$ , where  $0 \le i \le M-1$  and  $0 \le j \le N-1$ . To simplify notation, we employ  $T_i$  to represent a finite sequence of length N, given by  $T_i = [t_{i,0}, t_{i,1}, \dots, t_{i,N-1}]$ . This sequence represents one trace sampled at different time points j.

$$\mathbf{T} = \begin{bmatrix} T_0 \\ T_1 \\ \vdots \\ T_{M-1} \end{bmatrix} = \begin{bmatrix} t_{0,0} & t_{0,1} & \dots & t_{0,N-1} \\ t_{1,0} & t_{1,1} & \dots & t_{1,N-1} \\ \vdots & \ddots & \vdots \\ t_{M-1,0} & t_{M-1,1} & \dots & t_{M-1,N-1} \end{bmatrix}$$

(2.1)

## 2.2.1. LEAKAGE MODEL

In SCA, attackers need to establish a correlation between the data values processed and the power consumption associated with those operations [5], [60]. To do so, it is necessary to identify a target intermediate value within the cryptographic algorithm. However, the intermediate value does not directly reveal the secret information. Instead, a leakage model is needed to characterize the relationship between the intermediate value and the corresponding power consumption. This model is then used to determine the selected leakage function. There are four widely recognized leakage models:

- *Bit-level model*: This model focuses on a single bit of the processed data. It assumes that the side-channel measurements are directly proportional to this particular bit at the attack point [4], [5], [61]. Consequently, the bit-level model results in two possible labels for each processed data: 0 and 1.

- Hamming weight (HW) and Hamming distance (HD) model: The HW model focuses on counting the number of ones in the processed data. HD model assumes

that the side-channel measurements are related to the number of  $0 \leftrightarrow 1$  transitions [5], [60]. HW and HD models lead to nine possible labels (ranging from 0 to 8) for a single byte.

2. PRELIMINARY

• *Identity (ID) model*: This model assumes that the side-channel measurements directly reflect the direct value of the data processed. As a result, this model yields 256 possible labels (ranging from 0 to 255) for a single byte [62].

These leakage models offer distinct perspectives on the vulnerabilities that may be exploited. Let us denote the input plaintext/ciphertext as  $pt_i$  and define the secret key as k. When considering the AES algorithm employing the HW model, targeting the output of the S-box as the intermediate value. We can define the leakage function as  $f(pt_i, k) = \{HW(Sbox[pt_i \oplus k])\}$ .

### 2.2.2. Non-profiled SCA and Profiled SCA

SCA can be divided into two categories: non-profiled SCA [63] and profiled SCA [7]. Non-profiled SCA, also known as direct attacks, involves utilizing traces directly. This category includes simple power analysis/simple electromagnetic analysis (SPA/SEMA) [4], [64], differential power analysis/differential electromagnetic analysis (DPA/DEMA) [4], [64]. On the other hand, profiled SCA, also referred to as two-stage SCA, assumes the availability of open devices or their clones that can be utilized for leakage characterization. With this information, attackers can construct a model to predict the leakage behavior of the target device. This category offers improved performance compared to non-profiled SCA since it can significantly reduce the number of attacks.

#### NON-PROFILED SCA

## **Simple Power Analysis**

Simple power analysis (SPA) refers to the technique of directly interpreting observed power as a means of retrieving information about the underlying processing. This attack method was initially documented by Kocher et al. [4]. The focus of this attack is on deducing sensitive values through the visual analysis of individual power traces or averaged traces. Generally regarded as an initial phase, SPA serves as a foundational step preceding more intricate attack [6], [65]. For instance, SPA can determine the cryptographic algorithms through visual observation and identify the optimal time window for subsequent attacks. Note that when the attacker utilizes EM radiation instead of power consumption in this case, it is called simple electromagnetic analysis (SEMA) [64].

#### **Differential Power Analysis**

Differential power analysis (DPA) was first introduced by Kocher et al. [4], utilizing a specific statistical method. The DPA attack aims to extract a secret key, denoted as  $k^*$ , by analyzing the gathered traces **T** from Equation 2.1. To perform the DPA attack, we consider a leakage function denoted as  $f(pt_i, k)$ , which processes an input (plaintext/ciphertext),  $pt_i$ , along with the unknown secret key,  $k^*$ . To extract the secret key, we generate a range of key hypotheses k. For each hypothesis, we construct a corresponding vector using the function f. Among these vectors, the one that is constructed with the correct hypothesis will exhibit the strongest dependency on the input  $pt_i$ . This is because the side-channel

signal carries information about the correct key. The goal of the DPA attack is to distinguish this correct key hypothesis from the incorrect one. When the attacker exploits the EM emissions of the chip in this case, it is referred to as differential electromagnetic analysis (DEMA) [64].

The Difference of Means (DoM) technique [4], represents the first side-channel distinguisher in the literature. The DoM technique involves testing the hypotheses using two groups:  $G_0$  and  $G_1$ , which can be determined by focusing on the Least Significant Bit (LSB) in the bit-level model. When the targeted function is applied, it yields either a 0 or a 1. By assigning each hypothetical value to one of the groups, we average the associated traces based on their respective group. Subsequently, a difference trace is computed for each key hypothesis. This is achieved by calculating the difference between the means of the two groups. Specifically, for attack variable at point j, the difference trace for the guess key k is computed as Equation 2.2 [65]:

$$\Delta_{f}[j] = G_{1} - G_{0} = \frac{\sum_{i=0}^{m-1} f(pt_{i}, k) * t_{i,j}}{\sum_{i=0}^{m-1} f(pt_{i}, k)} - \frac{\sum_{i=0}^{m-1} (1 - f(pt_{i}, k)) * t_{i,j}}{\sum_{i=0}^{m-1} (1 - f(pt_{i}, k))}$$

(2.2)

For the correct key hypothesis, when  $k = k^*$ , this difference will be significantly greater than zero, resulting in the largest spikes in the difference trace. On the other hand, for all other cases, the difference will be approximately zero because only when the correct key and the samples representing the target function are aligned, the side-channel signals exhibit a distinguishable difference in means.

Correlation power analysis (CPA) represents an advanced iteration of DPA, exploiting the inherent correlation between power consumption and internal data or operations within a targeted device [66], [67]. Unlike DPA, which solely considers one bit of side-channel information, CPA makes use of the full range of available side-channel information. In a CPA attack, the attacker carefully analyzes power traces to identify correlations with hypothetical power consumption models that would emerge for different secret key values or other sensitive information. Following the acquisition of traces, we obtain M power traces, each containing N data points. Utilizing subscript notation,  $t_{i,j}$  denotes point j in trace i. let's assume there are K different subkeys to test. Consequently,  $h_{i,k}$  represents our power estimate model in trace i, presuming the subkey is k ( $0 \le i \le M-1$ ,  $0 \le k \le K-1$ ). Subsequently, the hypothesized power consumption values are juxtaposed with the collected traces via Pearson's correlation coefficient, denoted as  $\rho$ , as illustrated in Equation 2.3 [67].

$$\rho_{k,j} = \frac{\sum_{i=0}^{M-1} \left[ \left( h_{i,k} - \overline{h_k} \right) \left( t_{i,j} - \overline{t_j} \right) \right]}{\sqrt{\sum_{i=0}^{M-1} \left( h_{i,k} - \overline{h_k} \right)^2 \sum_{d=0}^{M-1} \left( t_{i,j} - \overline{t_j} \right)^2}}$$

(2.3)

$\rho$  allows us to evaluate the degree of correlation between the power estimate model and the collected traces for each guess k and time j. A higher correlation indicates a more accurate key guess. The correlation is evaluated within the range of -1 to 1, where values close to  $\pm 1$  indicate a strong linear dependency, while zero suggests no linear dependency.

20 2. Preliminary

#### PROFILED SCA

Profiled SCA assumes the presence of an attacker with access to a cloned device. It involves a two-step process: profiling and attack. In the profiling phase, adversaries systematically gather traces from the clone device while varying the known key used in cryptographic operations. These traces form the basis for constructing a template or statistical model, which captures and describes the behavior of leaked information. The adversary constructs a model that maps from the traces  $\mathbf{T_p}$  to the labels  $Y_p$ , which are the results of the leakage function. In the attack phase, traces from an unknown key on the target device,  $\mathbf{T_a}$ , are collected. These traces are independent of the profiling phase. Then,  $\mathbf{T_a}$  is applied to the pre-constructed model, allowing for the identification of the most probable key values through statistical analysis and comparison.

Profiled SCA exploits complex relationships between side-channel leakage and sensitive information, making it a powerful attack technique. One of the advantages of profiled SCA is that it requires fewer attacks to recover the key in the attack phase. However, building a proper model still requires a substantial number of traces during the profiling phase. Traditional profiled SCA, Template Attack (TA) [68], was considered the most powerful attack from a theoretical perspective [69]. However, it faces challenges when dealing with traces consisting of numerous features, as calculating the covariance between all features becomes infeasible. To overcome this, selecting *points-of-interest (POIs)*, that leak the most is crucial [70], [71]. Typically, features with the highest variance are chosen.

Recently, machine learning algorithms have been explored in the context of SCA [72]–[74]. Various machine learning techniques such as Random Forest [72] and Support Vector Machines (SVMs) [73] have been employed for SCA, demonstrating good performance in various scenarios. Similar to TA, machine learning techniques perform better when *POIs* are selected before the attack. In addition to machine learning, deep learning techniques have garnered attention in the SCA community [75]–[78]. Previous studies have shown that deep learning achieves state-of-the-art results, even in the presence of countermeasures. Convolutional Neural Networks (CNNs), in particular, exhibit exceptional performance for various SCA problems.

#### MACHINE LEARNING-BASED SCA

Machine learning is a powerful methodology [79] that enables machines to solve complex problems that would be impractical to tackle using traditional algorithms. Unlike traditional algorithm development by human programmers, machine learning allows machines to discover their algorithms through experience and dataset analysis [80]–[82]. One key capability of machine learning algorithms is their ability to identify patterns in datasets, whether labeled or unlabeled. Based on the availability of labeled data and the problem objectives, machine learning can be broadly categorized into two types: supervised learning and unsupervised learning [83].

Supervised learning involves providing the computer with example inputs and their corresponding desired outputs, essentially acting as a "teacher" to train the model. The objective is for the computer to learn a general rule that maps inputs to outputs. A common application of supervised learning is classification problems [84], [85], where inputs are categorized into predefined classes. During the training phase, a classifier model is

constructed based on existing labeled training datasets [84]. The complexity of model training depends on the task difficulty and the complexity of the model itself. A well-trained classifier should ideally accurately determine the output class for new inputs not encountered during training, demonstrating its ability to generalize from the provided data. On the other hand, unsupervised learning does not rely on labeled data. Instead, the learning algorithm autonomously explores the input data to discover underlying structures or extract valuable features. Unsupervised learning techniques are frequently utilized for tasks such as clustering and dimensionality reduction [86].

Profiled SCA can be framed as a classification or regression problem, establishing a natural connection between supervised learning and profiled SCA. Both involve a learning phase (referred to as the profiling phase in SCA) and a prediction phase (known as the attack phase in SCA). During the profiling phase in SCA, machine learning algorithms learn patterns from a set of profiling traces and labels, known as the learning dataset, which consists of input-output pairs. By adopting machine learning techniques, statistics can be automatically learned from the unknown leakage distributions present in the profiling dataset.

## **DEEP LEARNING-BASED SCA**

Deep learning, which is a specialized branch of machine learning, focuses on the utilization of artificial neural networks (ANNs) [87]. Currently, deep learning is widely used in SCA. To understand neural networks, it is crucial to grasp the concept of neurons, which serve as the fundamental building blocks of ANNs. Neurons receive input values and compute the weighted sum using a weight matrix. Nonlinear activation functions are applied to the weighted sum to enable neural networks to learn nonlinear functions and models. The output of a neuron can be mathematically described by the equation  $y = \sigma * (\sum_{i=1}^{n} x_i w_i + b)$  where the input x has a size of n, w represents the weights, b denotes the bias, and  $\sigma$  signifies the activation function. The bias also acts as a weight for the input  $x_0$ , which is assigned a value of 1. Thus, the equation takes the form  $y = \sigma * (\sum_{i=0}^{n} x_i w_i)$ , with  $x_0 = 1$  and  $w_0 = b$ . This calculation is performed in all neurons within a layer, allowing us to describe it using matrices, where the input sample features can be arranged as columns or rows. Therefore, the equation becomes  $\mathbf{Y} = \sigma * (\mathbf{X} * \mathbf{W} + \mathbf{B})$ , where  $\mathbf{X}$  represents the input matrix,  $\mathbf{W}$  is the weight matrix,  $\mathbf{B}$  denotes the bias matrix, and  $\sigma$  denotes the activation function.

The essence of neural network learning lies in iteratively adjusting these weights and biases during each epoch. Within an epoch, two critical stages occur: the forward pass and the backward pass. During the forward pass, predictions are made based on input data from the training or test dataset. On the other hand, the backward pass focuses on updating the model's weights and biases to refine the network's predictions. This backward pass commonly employs a technique called backward propagation. To optimize the effectiveness of this procedure, a loss function is established to quantify the discrepancy between the predicted output and the actual ground truth. Subsequently, during the backward propagation stage, each adjustable parameter is updated using various optimization algorithms such as Stochastic Gradient Descent, RMSprop, and Adam [88] to efficiently locate the minimum of the loss function. These steps are repeated until the network reaches an optimal minimum that satisfies the predefined criteria.

22 2. Preliminary

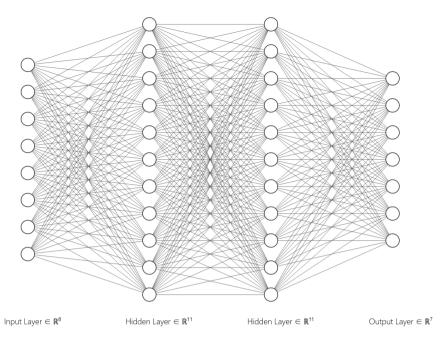

Figure 2.2: Example of MLP with 8 units in the input layer, 2 hidden layers, and 7 units in the output layer. The figure is generated by NN-SVG: http://alexlenail.me/NN-SVG/index.html.

A deep learning model is a sophisticated architecture comprising multiple interconnected layers of neurons. Each layer plays a specific role in acquiring knowledge and extracting complex features from input data. The input layers receive and preprocess raw input data, establishing the foundation for subsequent processing. As information flows through the network, hidden layers play an important role in transforming and refining representations learned from previous layers. Ultimately, the output layer generates conclusive predictions or classifications based on the transformed features. One example of a deep learning model is the multilayer perceptron (MLP) with more than one hidden layer, illustrated in Figure 2.2. MLP contains several hidden layers and takes a set of inputs to produce a corresponding set of outputs. The interconnections and multilayered structure of neurons allow deep learning models to effectively capture complex data distributions and comprehend intricate decision boundaries.