**Delft University of Technology**

#### High-Speed Interfaces for Capacitive Displacement Sensor

Xia, Sha

DOI 10.4233/uuid:9f4042e1-ceb3-4894-90c5-3602bd0a1276

Publication date 2019

**Document Version** Final published version

Citation (APA) Xia, S. (2019). High-Speed Interfaces for Capacitive Displacement Sensor. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:9f4042e1-ceb3-4894-90c5-3602bd0a1276

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

## High-Speed Interfaces for Capacitive Displacement Sensor

Sha Xia

# High-Speed Interfaces for Capacitive Displacement Sensor

# High-Speed Interfaces for Capacitive Displacement Sensor

Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen Chair of the Board for Doctorates to be defended publicly on Monday 11 November 2019 at 12.30 o'clock

by

### Sha XIA

Master of Science in Electrical Engineering Delft University of Technology, The Netherlands born in Wuhan, P.R. China This dissertation has been approved by the promoter.

| Composition of the doctoral committee: |                                          |  |  |  |

|----------------------------------------|------------------------------------------|--|--|--|

| Rector Magnificus,                     | chairperson                              |  |  |  |

| Dr. S. N. Nihtianov                    | Delft University of Technology, promotor |  |  |  |

| TU Eindhoven / ASML            |

|--------------------------------|

| NXP                            |

| Delft University of Technology |

|                                |

ISBN: 978-94-028-1785-0

Copyright © 2019 by Sha Xia

All rights reserved. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the author.

Printed in The Netherlands

To my beloved parents and my wife Jie 致我亲爱的父母亲和钟洁

## **Table of Contents**

| 1. IN  | TRODUCTION                                                                       | 1     |

|--------|----------------------------------------------------------------------------------|-------|

| 1.1.   | Motivation                                                                       | 1     |

| 1.2.   | Main question and research methodology                                           | 3     |

| 1.3.   | Organization of this thesis                                                      | 4     |

| 2. BA  | ACKGROUND OVERVIEW                                                               | 9     |

| 2.1.   | Capacitive displacement sensors                                                  | 9     |

| 2.1.1. |                                                                                  | 9     |

| 2.1.2. |                                                                                  | 11    |

| 2.1.3. | · ·                                                                              | 13    |

| 2.1.4. |                                                                                  | 14    |

| 2.2.   | Capacitive sensor interfacing approaches                                         | 14    |

| 2.2.1. |                                                                                  | 15    |

| 2.2.2. | 1 1 2 8                                                                          | 17    |

| 2.2.3. |                                                                                  | 20    |

| 2.2.4. |                                                                                  | 21    |

| 2.2.5. | Comparison and Discussion                                                        | 22    |

| 2.3.   | Capacitance measurement systems                                                  | 25    |

| 2.3.1. |                                                                                  | 25    |

| 2.3.2. |                                                                                  | 27    |

| 2.3.3. | 1 0                                                                              | 29    |

| 2.3.4. |                                                                                  | 30    |

| 2.4.   | Conclusion                                                                       | 31    |

| 3. HI  | GH-SPEED HIGH-PRECISION DISPLACEMENT MEASUREMENT                                 |       |

| SYSTI  | EM BASED ON CAPACITIVE SENSORS                                                   | 39    |

| 3.1.   | Introduction                                                                     | 39    |

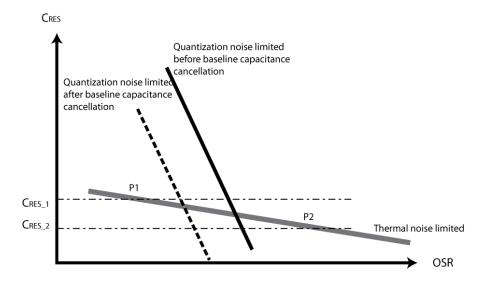

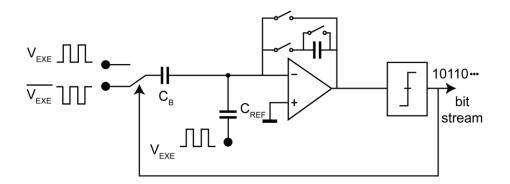

| 3.2.   | Baseline Capacitance Compensation                                                | 40    |

| 3.2.1. | Baseline sensor capacitance                                                      | 40    |

| 3.2.2. | Circuit implementation issues of baseline capacitance compensation               | 43    |

| 3.3.   | Displacement Measurement with a Capacitive Sensor Incorporating Baseline Capacit | tance |

| Canc   | ellation                                                                         | 46    |

| 3.3.1. | System-level consideration                                                       | 46    |

| 3.3.2. | System error budgeting                                                           | 48    |

| 3.4.   | Discussion and conclusion                                                        | 51    |

| 3.4.1. | Appropriate interfacing principles                                               | 52    |

| 3.4.2. | Conclusion                                                                       | 53    |

|        |                                                                                  |       |

## 4. CAPACITIVE SENSOR INTERFACE USING A CHARGE-BALANCING PRINCIPLE

| PRINCIPLE                                        |                                                                                                             |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Introduction                                     | 55                                                                                                          |

| System-level considerations                      | 56                                                                                                          |

| Overview                                         | 56                                                                                                          |

| Power-efficient capacitance-to-digital converter | 57                                                                                                          |

| Charge-balancing operation                       | 62                                                                                                          |

|                                                  | Introduction<br>System-level considerations<br>Overview<br>Power-efficient capacitance-to-digital converter |

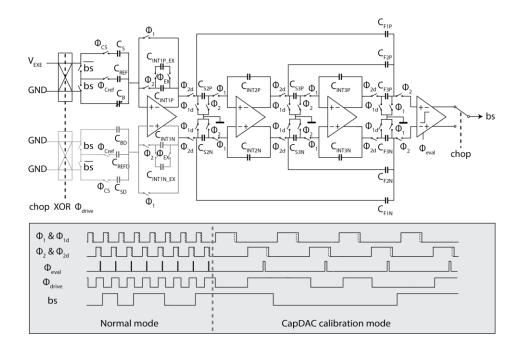

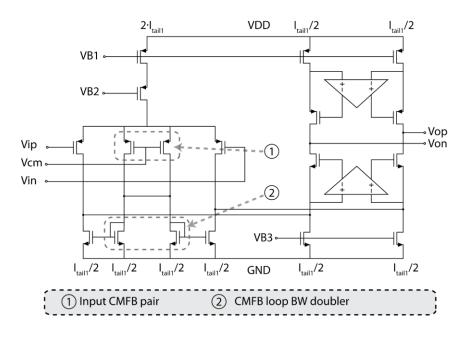

| 4.3.   | Circuit-level techniques                                                | 68 |

|--------|-------------------------------------------------------------------------|----|

| 4.3.1. | Overview                                                                | 68 |

| 4.3.2. | Third-order incremental $\Sigma\Delta$ capacitance-to-digital modulator | 68 |

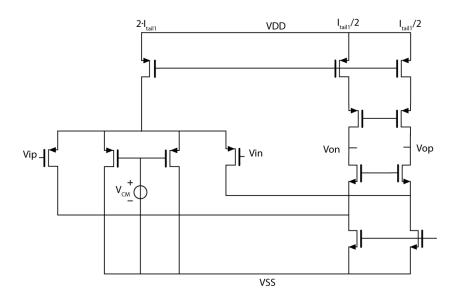

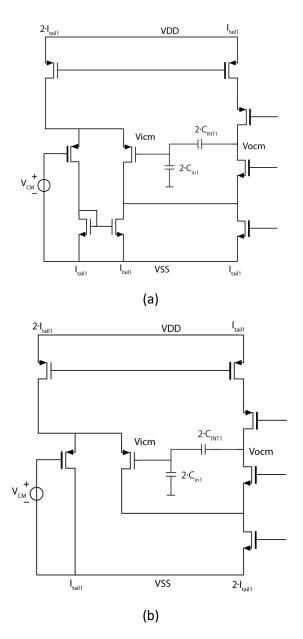

| 4.3.3. | Input stage design considerations                                       | 70 |

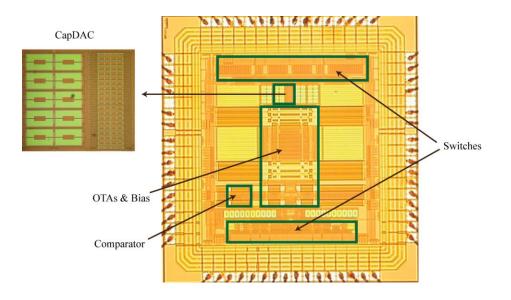

| 4.4.   | Realizations and measurement results                                    | 73 |

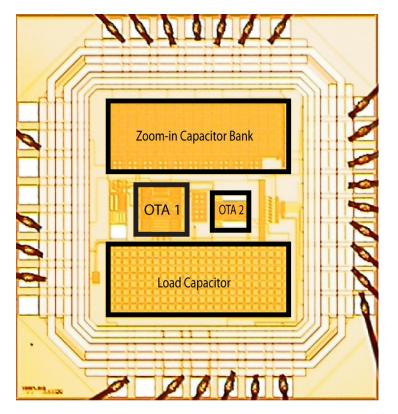

| 4.4.1. | Layout                                                                  | 73 |

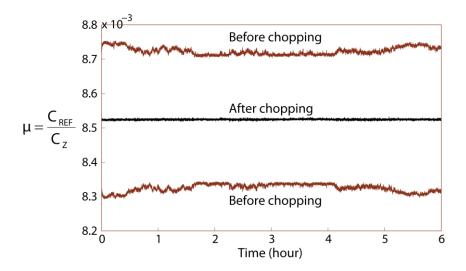

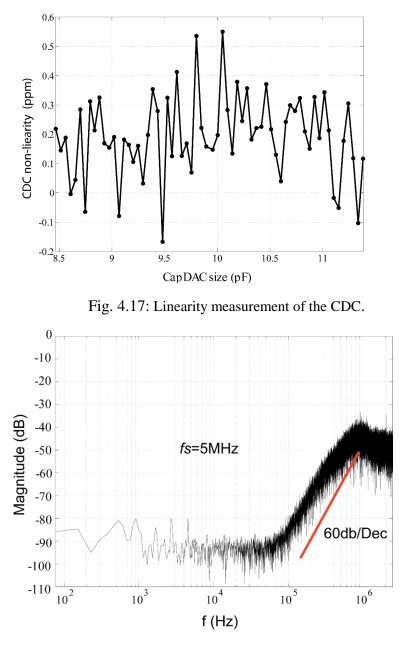

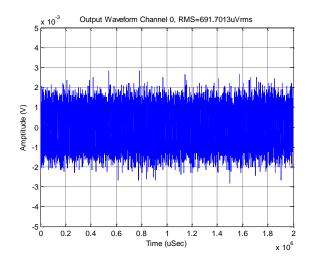

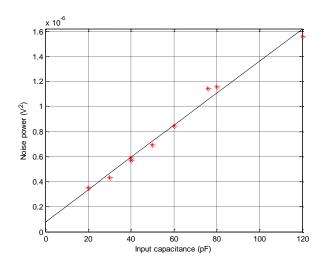

| 4.4.2. | Measurement results                                                     | 74 |

| 4.5.   | Conclusions                                                             | 79 |

| 5. CA  | PACITIVE SENSOR INTERFACE USING CAPACITANCE-TO-                                |           |

|--------|--------------------------------------------------------------------------------|-----------|

| VOLTA  | AGE CONVERSION                                                                 | 81        |

| 5.1.   | Introduction                                                                   | 81        |

| 5.2.   | Operating principle                                                            | 83        |

| 5.2.1. |                                                                                | 83        |

| 5.2.2. | Capacitance-to-voltage converter                                               | 83        |

| 5.2.3. | Baseline capacitance cancellation                                              | 83        |

| 5.2.4. | Practical realization of the capacitance-to-voltage converter with baseline ca | pacitance |

| cancel |                                                                                | - 84      |

| 5.3.   | Circuit implementation                                                         | 87        |

| 5.4.   | Realizations and measurement results                                           | 89        |

| 5.5.   | Conclusions                                                                    | 91        |

| 6. DI  | SCUSSIONS AND CONCLUSIONS                                                      | 93        |

| 6.1.   | Benchmark                                                                      | 93        |

| 6.2.   | Main findings and contributions                                                | 98        |

| 6.3.   | Future research directions                                                     | 99        |

| SUMM   | ARY                                                                            | 111       |

| LIST O | <b>F PUBLICATIONS</b>                                                          | 113       |

| ACKN   | OWLEDGEMENTS                                                                   | 115       |

| ABOU   | T THE AUTHOR                                                                   | 119       |

## **Chapter 1**

## Introduction

## **1.1. Motivation**

Capacitive sensors are one of the most widely used sensors today, as they offer a number of distinct advantages: compactness, simple principle of operation, and relatively low cost [1-13]. Capacitive sensors can achieve very high resolution due to the fact that, ideally, they consume no electric energy and therefore generate no electric noise [14,15]. A key application of capacitive sensors is position/displacement measurement. Over the last several years, interest in implementing capacitive sensors for measuring extremely small displacements in the sub-nanometer range has increased. For example, such sensors are now used as inertial sensors, accelerometers, and pressure sensors.

Capacitive displacement sensors are also used in high-precision mechatronic systems where the position/vibration of critical mechanical components must be dynamically stabilized with sub-nanometer precision. Any unwanted motion must be sensed in real time and be corrected for. For example, in the next generation extreme ultraviolet (EUV) lithography machines, the required precision in displacement/position measurement will be in the picometer range [16,17].

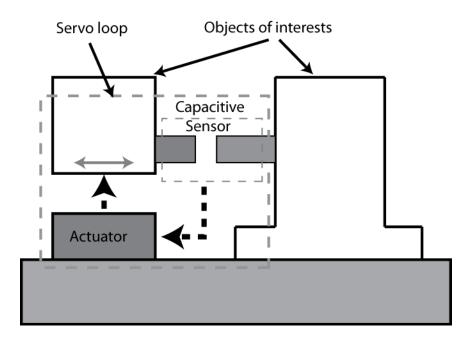

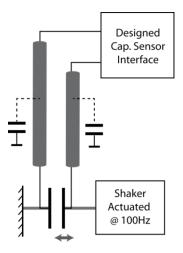

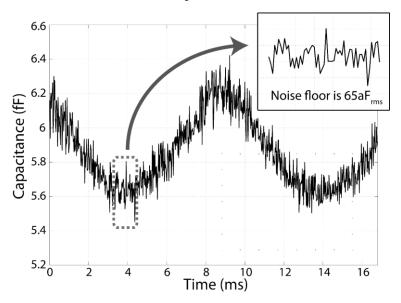

The correction of such small displacements/vibrations can be achieved with the help of a servo loop consisting of a displacement sensor and an actuator, as shown in Fig. 1.1. The performance of the servo-loop depends heavily on that of the displacement sensor. However, achieving sub-nanometer displacement measurement with a capacitive

Fig.1.1: Lithography machine in which the wafer stage is dynamically aligned with the lens columns by measuring the small displacement.

displacement sensor is quite challenging, both in terms of the sensor design and the interface electronics. On the one hand, the sensitivity of a capacitive displacement sensor, which is determined by the mechanical structure of the sensor head, is limited by a number of non-idealities such as electrode surface roughness and tilt. On the other hand, the reduced sensitivity as a result of these non-idealities puts more pressure on the interface circuit, which must then compensate for the drop in sensor sensitivity.

This thesis will not address the sensor head design, the focus of this work is on the interface circuit. The interface circuit should have the following characteristics:

#### Precision

To digitize the capacitance  $C_{sen}$  of a precision displacement sensor, a precision reference is required, which can either be a physical reference capacitor  $C_{ref}$ , or an 'equivalent' reference capacitor derived from a combination of other references, such as resistors, inductors, time references, current references, and voltage references [18]. While most of the recently reported capacitance-to-digital converters (CDC) directly employ a physical reference capacitor and demonstrate good resolution, measurement speed, and energy efficiency, their precision is

ultimately limited by the quality of the capacitive reference used.

#### Speed

Because the result of the capacitive displacement measuring system is used in a servo loop, the measurement speed of the CDC is also very important. If it is too slow the servo loop will not have sufficient bandwidth to correct for errors, causing the correction to be insufficient. It can be seen as a feedback system with delay in the loop filter, in which excess delay can cause instability.

#### Power

High speed measurement often leads to high power consumption. In an precision mechatronics environment, low power operation is also vital. Excess power consumption generates heat, which leads to a rise in temperature. Since capacitive sensors can be used to sense a lot of physical quantities, it is also quite easy to get cross-sensitivity from temperature changes. In that case, the measurement system cannot distinguish if the change in sensor capacitance is from a displacement change or temperature change. Therefore, the power consumption of the CDC must be limited to a certain degree.

A broad literature study (chapter 2) has shown that most existing capacitive interface circuits have either a low conversion speed or low capacitive resolution, which has led to the conclusion that no existing solution demonstrates all of the above-mentioned properties at the same time. This is due to the fact that no prior applications require such a stringent set of specifications. An in-depth investigation of the limitations of capacitive displacement sensors will therefore provide valuable information that could expand the application territory of capacitive sensors even further, which is the motivation behind the research described in this thesis.

# 1.2. Main research question and research methodology

The main research question of this thesis is: can the capacitive sensor interfaces be designed to enable capacitance measurements with high resolution and short measurement latency in a power-efficient way, so that it becomes compatible with high-precision real-time servo systems operating in tightly controlled working environments. At the same time, the stability of the interface should be high enough to avoid the need for recalibration.

To be more specific, the goal is to find a way to realize picometer level resolution displacement measurement using capacitive sensors that have stand-off distance of several micrometers, with a measurement time in microseconds range. On top of this, the power consumption should be kept as low as possible.

To answer the research question, the research methodology described below has been followed:

The first step is to take an overall look from a system point of view and to identify the limiting factors in the system. This is needed to find an optimum capacitance measurement system, possibly consisting of multiple sub-systems, each addressing a certain aspect of the requirements. This step is necessary, since a single system that can achieve all the requirements may be too impractical to realize.

Next, state-of-the-art solutions for interfacing high-performance capacitive sensors are studied so as to evaluate the potential benefits for the target application. The investigation of capacitance measurement principles is geared toward their potential use in low-power, high-speed and high-accuracy applications.

The final step is to solve each of the challenges by proposing and implementing proper techniques. The validity of the proposed solution is verified with experimental results.

## **1.3. Organization of this thesis**

The thesis is organized in the following way, in order to answer the main question:

Chapter 2 provides a detailed survey of state-of-the-art voltage-driven, also called "twoport" capacitance, measurement circuits. The result of the survey provides a solid understanding of the limitations of the existing solutions and the pros and cons of each circuit topology.

Chapter 3 introduces the baseline capacitance cancellation technique and the implementation of this in the context of displacement measurement using capacitive sensor.

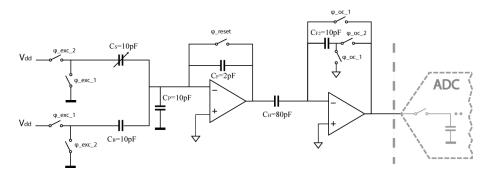

Chapter 4 presents a reconfigurable low-power CDC that can be used to realize both zoomin, high-resolution, high-speed capacitance measurement and high-resolution, large dynamic range, low-speed capacitance measurement. This is a circuit solution that can be used as the main CDC.

Chapter 5 presents an alternative solution that can be used to deliver a zoom-in, high-resolution, high-speed capacitance measurement with low power consumption. The pros and cons with respect to the work presented in Chapter 4 will be elaborated on.

In Chapter 6, a benchmark is provided that includes other recent works in this field. This chapter concludes the thesis and provides recommendations for future works.

## Reference

[1] H. Omran, M. Arsalan, K. N. Salama, 'A robust parasitic-insensitive successive approximation capacitance-to-digital converter', Proc. IEEE CICC, pp. 1-4, 2014.

- [2] H. Omran, A. Alhoshany, H. Alahmadi, K. N. Salama, 'A 33fJ/Step SAR capacitance-to-digital converter using a chain of inverter-based amplifiers', IEEE Trans. Circuits and Systems I, Vol. 64, No. 2, pp. 310-321, Feb. 2017.

- [3] B. Boser, 'Capacitive interface electronics for sensing and actuation', Berkley: University of California, 21st Workshop on Advances in Analog Circuit Design, AACD, Valkenburg aan de Geul, The Netherlands, 2012.

- [4] Z. Tan, R. Daamen, A. Humbert, K. Souri, Y. Chae, Y. V. Ponomarev, M. A. P. Pertijs, 'A 1.8V 11μW CMOS smart humidity sensor for RFID sensing applications,' Proc. IEEE Asian Solid-State Circuits Conference (A-SSCC), 2011.

- [5] S. Xia, K. Makinwa, S. Nihtianov, 'A capacitance-to-digital converter for displacement sensing with 17b resolution and 20 μs conversion time,' Digest of Technical Papers, ISSCC, 2012.

- [6] Z. Tan, R. Daamen, A. Humbert, et al., 'A 1.2-V 8.3-nJ CMOS humidity sensor for RFID applications', IEEE Journal of Solid-State Circuits, Vol. 48, No. 10, pp. 2469-2477, 2013.

- H. Ha, D. Sylvester, D. Blaauw, 'A 160nW 63.9 fJ/conversion-step capacitance-todigital converter for ultra-low-power wireless sensor nodes' Digest of Technical Papers, ISSCC, 2014.

- [8] R. Yang, S. Nihtianov, 'A time/resistor-referenced capacitive sensor interface for displacement measurement in the sub-nanometer range', IEEE International Symposium on Industrial Electronics, pp.1-5, 2013.

- [9] S. Oh, Y. Lee, J. Wang, Z. Foo, Y. Kim, et al., 'A dual-slope capacitance-to-digital converter integrated in an implantable pressure-sensing system', IEEE Journal of Solid-State Circuits, Vol. 50, No. 7, pp. 1581-1591, 2015.

- [10] H. Omran, M. Arsalan, K. N. Salama, '7.9 pJ/step energy-efficient multi-slope 13bit capacitance-to-digital converter', IEEE Transactions on Circuits and Systems II, Vol. 61, No. 8, pp. 589-593, 2014.

- [11] J. P. Sanjurjo, E. Prefasi, 'A high-sensitivity reconfigurable integrating dual-slope CDC for MEMS capacitive sensors', Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), pp. 149-152, 2015.

- [12] J. P. Sanjurjo, E. Prefasi, C. Buffa, 'An energy-efficient 17-bit noise-shaping dualslope capacitance-to-digital converter for MEMS sensors', Proc. ESSCIRC, 2016.

- [13] Y. He, Z. Chang, L. Pakula, et al., 'A 0.05 mm<sup>2</sup> 1V capacitance-to-digital converter based on period modulation', Digest of Technical Papers, ISSCC, 2015.

- [14] L. K. Baxter, Capacitive Sensors: Design and Applications. New York: IEEE Press, 1997.

- [15] S. Nihtianov, 'Capacitive and eddy current displacement sensors: advantages and limitations', IEEE Industrial Electronics Magazine (IEM), pp. 6-15, Mar. 2014.

- [16] R. Y. Oscar, S. van de Ven, S. Xia, J. P. van Schieveen, J. W. Spronck, R. H. Munning Schmidt, S. Nihtianov, 'Autonomous self-aligning and self-calibrating capacitive sensor system', in Autonomous and Intelligent Systems (AIS2012), Aveiro, Portugal, 2012, pp. 10-17.

- [17] S. Xia, J. P. Van Schieveen, S. Nihtianov, J. W. Spronck, 'Concept evaluation of a high performance self-aligning capacitive displacement sensor', in Industrial Technology (ICIT), 2010 IEEE International Conference on, 2010, pp. 1575-1580.

- [18] R. Yang, 'A High-Precision Capacitive Sensor System for Displacement Measurements', PhD Thesis, Delft University of Technology.

## Chapter 2

## **Background Overview**

## 2.1. Capacitive displacement sensors

This section focuses on the principle of operation and the main characteristics of a parallelplate capacitive displacement sensor. An electrical model of the sensor is introduced, followed by a discussion on the challenges and limiting factors in high-performance applications.

#### 2.1.1. Operating principles of capacitive displacement sensors

Capacitive displacement sensors come in a variety of structures. The parallel-plate capacitive sensor is however the most commonly utilized structure when high sensitivity is required for very small displacement measurements. As the name suggests, a parallel-plate capacitive sensor comprises two parallel electrodes with an overlapping area A and plate distance d. When d is much smaller than the plate dimensions, the electrical field can be considered to be perpendicular to the parallel plates, and the capacitance of the structure can be approximated as:

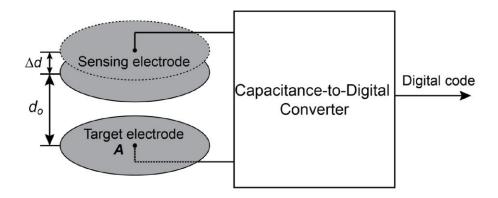

Fig. 2.1: Parallel-plate capacitive displacement sensor and the readout circuit.

$$C = \epsilon \frac{A}{d} \tag{2.1}$$

where  $\epsilon$  is the dielectric constant of the material between the two plates. In a capacitive displacement sensor, variations in *d* result in a change in capacitance, therefore the displacement information can be obtained by means of capacitance measurement. For a small displacement  $\Delta d$  which satisfies  $\Delta d \ll d$ , we have:

$$\Delta C = \epsilon \frac{A}{d \pm \Delta d} - \epsilon \frac{A}{d} \approx \mp \epsilon \frac{A}{d^2} \cdot \Delta d \qquad (2.2)$$

The term  $\epsilon \frac{A}{d^2}$  is called the sensitivity of the capacitive displacement sensor. It describes how much capacitance *C* changes ( $\Delta C$ ) in response to a change in distance ( $\Delta d$ ). It is clear that the capacitive displacement sensor is not linear and that the sensitivity is inversely proportional to the square of the plate distance *d*. From this relationship, it can be inferred that for higher sensitivity, the plate distance should be reduced.

A more insightful view can be obtained by looking at the relative sensitivity of the capacitive displacement sensor. If we divide Eq. 2.2 by Eq. 2.1, we can obtain:

$$\frac{\Delta C}{C} \approx \mp \frac{\Delta d}{d} \tag{2.3}$$

which suggests that the relative change in the capacitance is approximately proportional to the relative change in the plate distance. As the relative changes in capacitance directly translates into the resolution requirements of the sensor readout circuit, with Eq. 2.3 we can estimate the required nominal plate distance based on the target displacement resolution.

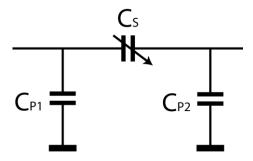

#### 2.1.2. Electrical model of capacitive displacement sensors

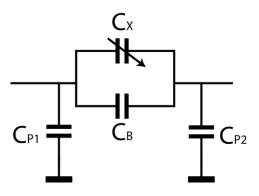

Figure 2.2 shows an electrical model of a capacitive sensor. Besides the sensor capacitor  $C_S$ , also included in the model are two parasitic capacitors  $C_{P1}$  and  $C_{P2}$  at the two terminals of  $C_S$ . Parasitic capacitance is inevitable in the realization of capacitive sensors. It plays an important role in the performance of the capacitive sensor measurement systems, as it tends to increase their energy consumption. Therefore, minimizing the parasitic capacitance can be an important step toward building an energy-efficient capacitive sensor measurement system.

Capacitive sensors are high-impedance sensors, and so they are quite sensitive to electrical disturbances [1]. Therefore, the connection between such sensors and their interface circuits is often realized with coaxial cables, leading to a significant amount of parasitic capacitance to ground. The longer the cable, the larger the parasitic capacitance becomes. Minimizing the parasitic capacitance can be achieved by co-integrating the interface circuit with the sensor head in order to keep the distance as short as possible. This is also seen as one of the motivation for integrating capacitive sensors on the chip. In such realizations an interface circuit realized on the same chip or in the same package with the sensor can be an important way to improve the energy efficiency of the system.

Fig. 2.2: Electrical model of the capacitive displacement sensor.

Fig. 2.3: Electrical model of the capacitive displacement sensor, splitting the sensor capacitance into baseline capacitance and varying capacitance.

The simple model shown in Fig. 2.2 does not fully describe how the measurand modulates the sensor capacitor  $C_S$ . For instance, due to displacement, only a fraction of  $C_S$  varies. This can be modelled by defining a mean, or baseline capacitance  $C_B$  and a varying capacitance  $C_X$ , as is shown in Fig. 2.3. A modulation index can be defined as in [2]:

$$C_B = \frac{C_{S,max} + C_{S,min}}{2} \tag{2.4}$$

$$\alpha = \frac{C_{S,max} - C_{S,min}}{C_B} \tag{2.5}$$

The modulation index  $\alpha$  expresses the ratio of the capacitance variation range to the baseline capacitance, and is in most cases in the order of 0.1 or smaller. A low modulation index often means that a large portion of the dynamic range of the interface will be wasted

on the baseline capacitance, leading to low energy efficiency [3]. Therefore, it is important to find a way to increase the modulation index of the capacitive sensor.

The reason for a low modulation index is the stand-off distance between the two plates d, which is much larger than the maximum displacement of interest  $\Delta d_{max}$ . The reasoning behind this will be discussed in the next section.

## 2.1.3. Alignment of capacitive displacement sensors

As discussed in the previous sections, the stand-off distance between the plates of a capacitive sensor plays an important role, as it determines its sensitivity as well as the modulation index. In industrial applications, the stand-off cannot be smaller than a few hundred micrometers [4], due to mounting and machining tolerances, error from tilt. However, such a stand-off is a serious challenge for the readout electronics design.

This is especially true for the types of applications for which the solutions presented in this thesis are intended: the stabilization and vibration reduction of essentially static objects. Due to the fact that the objects to be measured are almost still, the variation in their displacement will often be smaller than the practically achievable stand-off distance between the target and the capacitive sensor head. This inevitably leads to low sensitivity and a low modulation index, and hence to wasted power in the capacitance measurement system [3,5].

In order to improve the alignment accuracy, several methods can be used. One method is to fabricate all the relevant parts with small tolerances. However, not only does this method significantly increases cost, but parts manufactured with micrometer accuracy are still not suitable for systems that need to be transported in an assembled state, because of the associated risk that accidental vibrations may destroy the sensor. Another method is manual alignment after the sensor assembly. However this leads to inefficiency, or may even be practically impossible. A better solution is to incorporate a self-alignment mechanism into the sensor head, as described in [6]. In that work, a thermally actuated auto-alignment

system called a "thermal stepper" is proposed. It is simple, cheap and reliable, and can achieve relatively precise alignment.

With a thermal stepper, the stand-off distance of the sensor head can be reduced to 10~20 µm, in practice. Consequently, for applications requiring nanometer sensitivity, modulation indexes are in the order of 0.01, in the best-case scenario.

#### 2.1.4. Discussion

This section discusses the basic operating principles and the electrical modelling of a parallel-plate capacitive displacement sensors. It has been shown that the alignment challenges of capacitive displacement sensors lead to low sensitivity and a very low modulation index. These place large dynamic range requirements on the succeeding interface circuit.

Since, in the target application, the displacement measurement will be used in a servo-loop, the speed requirement of the interface circuit is also high. In the next section, the principles of interface circuits that convert capacitance into electrical signal will be addressed, including the possible structures and references used for the conversion.

## 2.2. Capacitive sensor interfacing approaches

Many principles have been investigated in the past to measure capacitance. For the purposes of this thesis, we can classify these principles in the following two categories.

1) Indirect capacitance-to-digital conversion

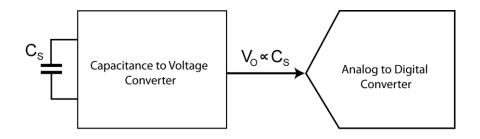

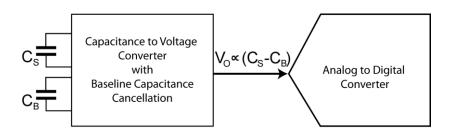

In many cases, the unknown capacitor is first converted into another unit, for instance a voltage, by a capacitance-to-voltage converter (CVC) [7-13] or into frequency (time period) by a capacitance-to-frequency converter (CFC) [14-27]. The capacitor is then converted into a digital code by either a conventional voltage-input analog-to-digital converter (ADC) or a time-to-digital converter (TDC).

2) Direct capacitance-to-digital conversion

Many ADCs make use of switched-capacitor circuitry allowing them to be readily converted into a capacitance-to-digital converter (CDC) by using the capacitor bank as a reference capacitor  $C_{REF}$ . Examples of such designs include switched-capacitor sigma-delta ( $\Sigma\Delta$ ) based CDCs [28-32] and successive approximation register (SAR) based CDCs [33-35]. These types of CDCs benefit from the charge-balancing/charge-redistribution nature of the corresponding ADCs and can achieve capacitance conversion. By applying the same reference voltage to both the sensor capacitor and the reference capacitor, the exact value of the reference voltage does not affect the conversion result. The output digital code is a representation of the ratio between the sensor capacitor  $C_S$  and the reference capacitor  $C_{REF}$ .

In the following sections, the operating principles of those capacitance conversion methods will be introduced, and the characteristics will be compared.

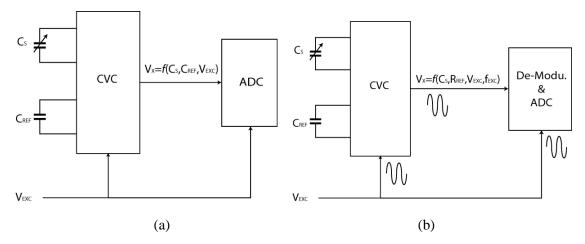

#### 2.2.1. Capacitive sensor interface employing a CVC

A CVC converts an unknown capacitance into a voltage signal. This is usually done with either charge amplifiers or trans-impedance amplifiers. The most commonly used CVCs can be classified into two categories: switched-capacitor (SC) CVCs [7-10] and continuous-time (CT) CVCs with synchronous demodulation [11-13].

Figure 2.4 shows the block diagrams of such circuits. CVCs require an excitation voltage and other passive components, usually in the form of a fixed reference capacitance, to

Fig. 2.4: CDCs based on a CVC followed by an ADC: (a) direct approach; (b) modulation approach.

convert the sensor capacitance into a voltage signal. In Fig. 2.4 (a), the output voltage of a CVC  $V_X$  can be expressed as a function of the unknown sensor capacitance  $C_S$ , the (equivalent) reference capacitance  $C_{REF}$ , and the excitation voltage  $V_{EXC}$ , as given in the following equation:

$$V_X = f(C_S, C_{REF}, V_{EXC})$$

(2.6)

The applied excitation voltage  $V_{EXC}$  usually has either a sinusoidal or a square-wave shape. As shown in Fig. 2.4 (b), with a resistor reference and a sinusoidal excitation signal, the CVC (in this case usually realized as an active RC integrator) outputs a modulated output voltage signal the amplitude of which is a function of the excitation voltage amplitude  $V_{EXC}$ , the excitation frequency  $f_{EXC}$ , the reference resistor value  $R_{REF}$ , and the unknown sensor capacitance  $C_s$ , as given in the following equation:

$$V_X = f(C_S, R_{REF}, V_{EXC}, f_{EXC})$$

(2.7)

This signal, together with the excitation signal, is fed into a demodulator. The demodulated signal is then converted by an ADC.

However, generating a sinusoidal excitation voltage is relatively complicated, as the extra sinusoidal-signal generation block makes the whole system power hungry [36]. It is therefore not often used, especially in chip-level solutions. On the other hand, square-wave

excitation can be implemented with just switches, which fits very well with CMOS technology and is hence very popular.

Using a CVC is one of the most popular methods for measuring capacitance and is often used as the signal-conditioning circuit in capacitive sensors. The advantage is that the signal conditioning and the AD conversion can be optimized separately, which can be useful in some cases.

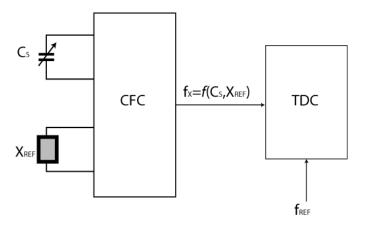

## 2.2.2. Capacitive sensor interface employing a CFC

Another class of capacitive sensor interface circuits is based on a capacitance-to-frequency converter (CFC) which converts capacitance into frequency/time signals, as shown in Fig. 2.5. The unknown capacitor  $C_s$  modulates the output time signal, which can be measured by a time-to-digital converter (TDC). In its simplest form, a TDC can be realized with a counter. Examples of these types of circuits are period-modulators and duty-cycle modulators.

Fig. 2.5: CDCs based on a CFC followed by a TDC.

Fig. 2.6: CDCs based on a relaxation oscillator followed by a TDC.

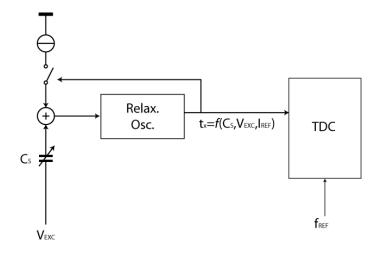

In essence, a CFC is a type of oscillator which generates a time-domain signal (frequency, pulse-width or phase shift) that is proportional to the sensor capacitance  $C_s$ . A CFC can be realized as an RC relaxation oscillator [14, 15], current source relaxation oscillator [16-21], LC oscillator [22,23], or ring oscillator [24-27].

In the case of an RC relaxation oscillator, the capacitance value determines the time constant of the discharge process, and thus changing the oscillation frequency. The advantage of an RC relaxation oscillator is that it can be implemented with simple digital logic, which can be compact and low-power [15]. However, the oscillation frequency is highly dependent on the shunting capacitance and resistance. Therefore, they are used in applications where the power budget is limited, and the accuracy requirement is relaxed.

Instead of discharging the capacitor with a resistor, a current source can also be used, which is the case in [16]. The discharging current source is controlled by the output of the oscillator, as shown in Fig. 2.6. The charge associated when exciting the sensor capacitance results in a voltage jump which is detected by the relaxation oscillator. Once the voltage has crossed a certain threshold, the oscillator controls the current source to discharge the capacitor until the threshold is crossed again. Because the current source discharges the capacitor with a fixed current, the amount of time it takes for the capacitor to be discharged will be linearly related to the unknown capacitance. Recent work has shown that this measurement principle can achieve good capacitance resolution in an energy-efficient manner. However, the operating speed of these circuits is generally on the low side, with conversion times in the order of a few milliseconds [16,21].

It is also possible to build an oscillator with a capacitance and an inductance, i.e. an LC oscillator [22]. The output frequency of an LC oscillator is a function of the sensor capacitance  $C_s$  and an inductance reference  $L_{REF}$ . The frequency signal produced by the LC oscillator can range from several hundred kHz to a few GHz. Because it is insensitive to the lossy component around  $C_s$ , it can be used for the measurement of sensor capacitor made from high loss materials [22]. This solution is favorable in chemical and bio-material applications, as many chemical properties show large sensitivity at RF/Microwave frequencies [23]. In industrial applications, where the physical changes such as displacement and acceleration must be detected, striving for very high frequency results in a waste of energy [5].

For very low-voltage and low-power applications, a ring oscillator can also be used. Two forms of circuits have been proposed. The unknown sensor capacitance  $C_s$  can be incorporated into the ring oscillator loop as a load capacitor, with which the output frequency of the ring oscillator will become a function of  $C_s$  [25]. Alternatively, the unknown charged sensor capacitance  $C_s$  can be used as a power supply for a ring oscillator. As time passes the ring oscillator discharges  $C_s$  causes the voltage to drop. During this process the oscillation frequency of the ring oscillator will also decrease accordingly over time. The time required for the ring oscillator frequency to drop down to a reference frequency will be a function of the sensor capacitance  $C_s$  [26,27], allowing it to be utilized to measure the sensor capacitance. One of the advantages of this approach is that the interface circuit is predominantly composed of digital circuit parts such as inverters and comparators, thus lending them very favorable for use in low-voltage operations and advanced technology nodes. It has also been shown that such interfaces can achieve superior energy efficiency [26]. However, this approach is highly sensitive to the parasitic capacitance to ground and to process variations, thus it is only suitable for relatively lowprecision applications.

### **2.2.3.** Capacitive sensor interface employing a $\Sigma\Delta$ -based CDC

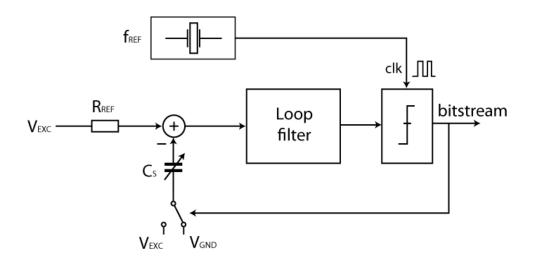

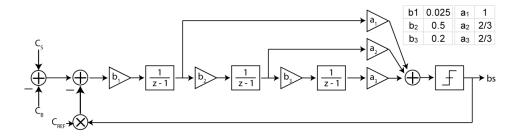

One popular way of measuring the charge stored by the sensor capacitor is the so-called charge-balancing principle [28-32]. This principle is often used in normal switched-capacitor  $\Sigma\Delta$  ADCs, where the input quantity is a voltage signal. Nevertheless, due to the charge-balancing nature of switched-capacitor  $\Sigma\Delta$  ADCs, with a small modification, the principle can also be applied to capacitance measurement [29].

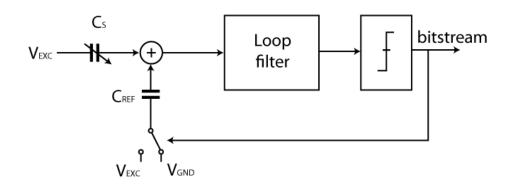

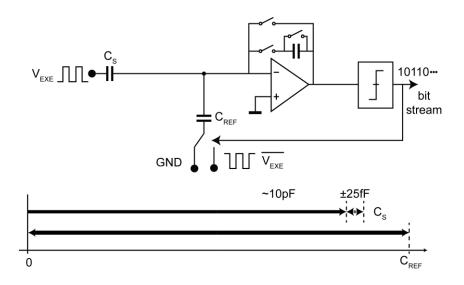

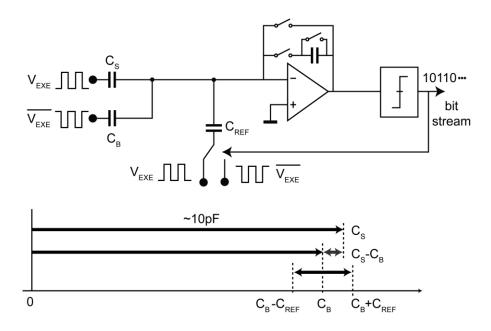

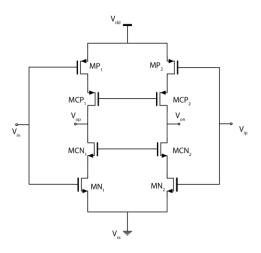

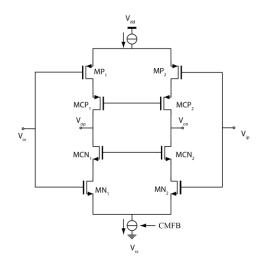

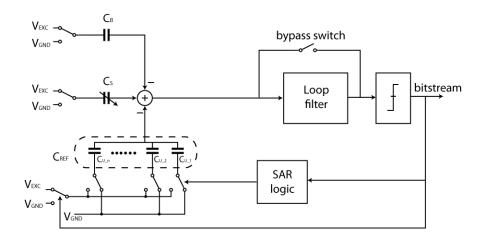

Figure 2.7 shows a block diagram of a  $\Sigma\Delta$ -based CDC. The charge that is supplied by the unknown capacitor  $C_S$  is in the input branch, while the charge supplied by the reference capacitor  $C_{REF}$  is in the feedback path. The charge difference is integrated by the loop filter, which keeps track of the total amount of charge difference over time. The polarity of the loop filter output is determined periodically by a comparator. Depending on the output of the comparator, the charge supplied by the feedback path will also have a different polarity. Since the negative feedback loop keeps the output of the integrator bounded, over time the total charge supplied by the input branch will be balanced by the charge supplied by the feedback branch, hence the term "charge-balancing".

$\Sigma\Delta$ -based CDCs have many advantages. Because  $\Sigma\Delta$ -based CDCs do not rely on component matching they can be used to realize high-resolution CDCs that also have a good linearity. The disadvantage, on the other hand, is their relatively low conversion speed due to their oversampling nature.

Fig. 2.7: CDC based on  $\Sigma\Delta$  converters.

Fig. 2.8: CDC based on SAR converters.

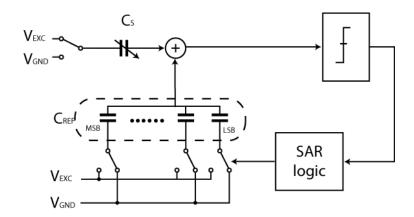

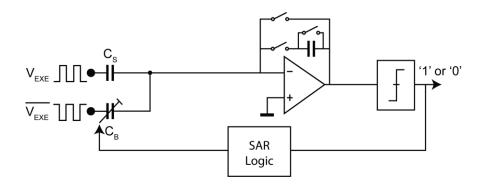

#### 2.2.4. Capacitive sensor interface employing a SAR-based CDC

Another way of measuring capacitance is with a SAR-based CDC. Figure 2.8 shows a block diagram of a SAR-based CDC. The binary-weighted capacitor bank normally used as a sampling capacitor in a SAR ADC will be used here as the reference capacitor  $C_{REF}$ . The SAR-based CDC works in two steps. The first step is the sampling step: The input of the comparator is shorted to ground  $(V_{GND})$ , (not shown in Fig. 2.8) and  $C_S$  is tied to the excitation voltage  $V_{EXC}$  while the reference capacitor array is connected to  $V_{GND}$ . The second step is the conversion step: The switch connecting the input of the comparator to ground  $(V_{GND})$ , (not shown in Fig. 2.8) is open. The switches connected to  $C_S$  and  $C_{REF}$  will be controlled by a SAR logic, which will compare  $C_S$  to the units of  $C_{REF}$  starting from the MSB element and ending with the LSB element. The input voltage  $V_X$  of the comparator will indicate the relative relationship between  $C_S$  and the compared capacitor because of charge conservation.

Depending on the sign of  $V_X$ , the corresponding digital bit is determined to be either '1' or '0'. If the bit is '1' the corresponding capacitor unit will be connected to  $V_{REF}$  in the remaining SAR conversion cycles. The conversion continues until the LSB is defined [34].

SAR-based CDCs can be made relatively fast, and due to their simple structure, they can be made very power-efficient as well. However, due to the limitations in component mismatch, the maximum resolution of this type of CDCs is limited to the low- or mediumresolution ranges, and so is the precision.

## 2.2.5. Comparison and Discussion

As can be seen from the discussions in this section, over the years a variety of interface principles for capacitive sensors have been developed. These solutions cover a wide range of application specifications. It is therefore important to compare the performance of different interfacing principles from different angles to be able to select the most suitable principles for use in building a capacitive displacement sensor interface system that can address the challenging specifications presented in Chapter 1. The performance of the prior art has been summarized below.

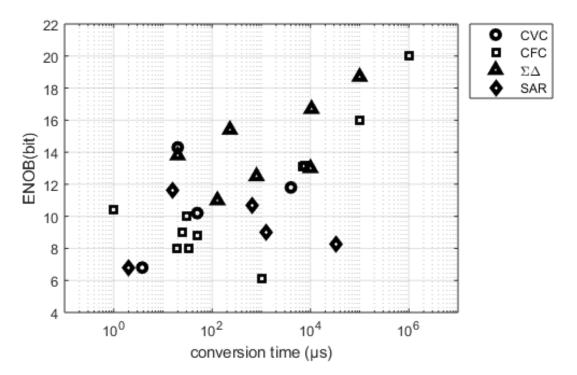

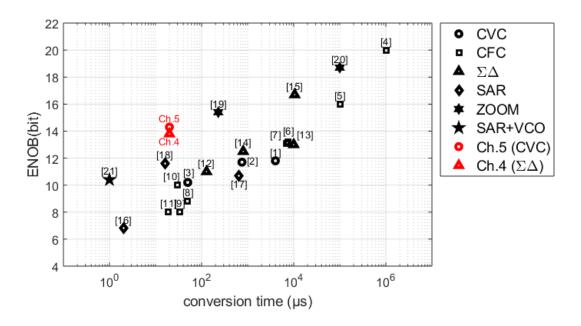

Fig. 2.9: Achievable ENOB and conversion time of various capacitive sensor interfaces

Fig. 2.10: Energy efficiency of different types of capacitive interface circuits.

The effective number of bits (ENOB) of an interface is a very important performance indicator as it not only captures the resolution of a circuit, but also its linearity. In Fig. 2.9, the ENOB achieved by various capacitance interfaces are plotted in relation to their conversion time.

Included in this survey are representative designs from recent years of CVC [8, 11-13, 37], CFC [15-17, 21, 24, 26, 27, 38-40],  $\Sigma\Delta$ -based CDC [31, 32, 42-46], and SAR-based CDC [33-35, 47, 48]. It can be seen from Fig. 2.9 that generally speaking, the higher the resolution target, the longer conversion time is needed. The upper left corner in Fig. 2.9 stands for high-resolution, high-speed applications. Among those principles, only  $\Sigma\Delta$ -based CDCs and CDCs based on a CFC with relaxation oscillator/period modulator realization have been able to achieve ENOBs greater than 13 bits. Both principles make use of the intrinsic linearity offered by the architecture and utilize oversampling to increase resolution [29,36]. However, CFC-based interfaces show speed disadvantages compared to their  $\Sigma\Delta$ -based counterparts.

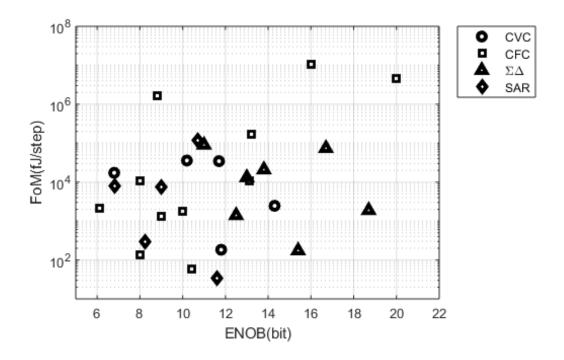

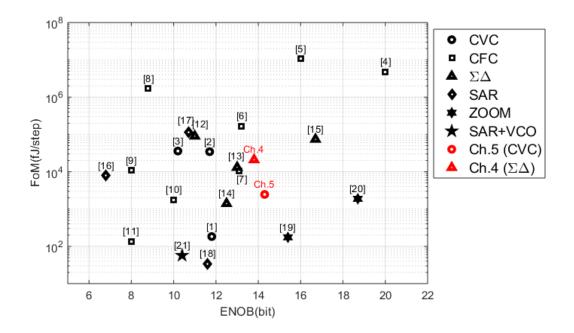

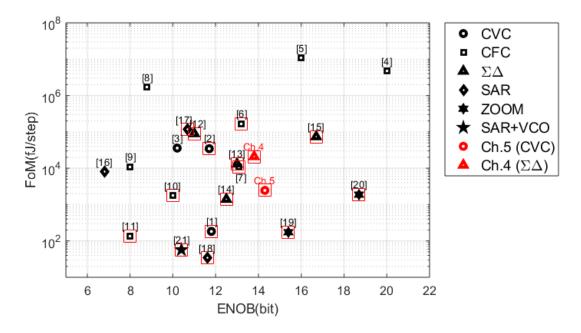

To facilitate the comparison of energy efficiency across interface circuits with different ENOBs, the figure-of-merit (FoM) is defined as:

$$FoM = \frac{Energy\ per\ conversion}{2^{ENOB}} \tag{2.8}$$

Figure 2.10 shows the energy consumption per conversion step of various CDC designs as a function of the ENOBs. For the same ENOB, the lower the amount of energy that is consumed per conversion step, the better the energy efficiency achieved. The unit of this FoM is energy/step. In Fig. 2.10, the designs situated closer to the bottom have better energy efficiency.

Generally speaking, the FoMs that can be achieved by CDCs are lower compared to those of ADCs. This is because unlike ADCs, the reported CDCs may operate under quite different circumstances. For example, CDCs often operate with large parasitic input capacitances, which influences power efficiency in a negative way, while lowering the resulting FOMs of the CDCs.

It is noticeable that SAR-based CDCs achieves the best FoMs. However, all the designs are in low to medium ENOB regions. CVC-based CDCs can also achieve good energy efficiency, because an optimal power budget can be made available for the CVC and the ADC separately. The CFC-based capacitive interface circuits cover a large spectrum of ENOB values ranging from low to high. On the low ENOB side, designs utilize relatively simple building blocks, thus facilitating good energy efficiency. When higher ENOBs are required, the energy efficiency drops.

It can also be seen that among designs that have achieved high ENOBs,  $\Sigma\Delta$ -based CDCs achieve better energy-efficiency compared to CFC-based CDCs, while at the same time achieving a shorter conversion time. As we will see from the discussion in the next section,  $\Sigma\Delta$ -based CDCs at the same time have a very versatile architecture that has the potential to further increase the conversion speed and energy efficiency.

## 2.3. Capacitance measurement systems

A capacitive displacement measurement system consists of a sensor head and an interface circuit, which also contains the reference. In order to achieve accurate displacement measurement, the accuracy of both the sensor head and the interface matters. For the interface circuit, the properties of the reference are also an important point of consideration. In the previous two sections the capacitive displacement sensor modeling and the capacitive sensor interface circuit principles were introduced. In this section, a system-level analysis will be presented.

#### **2.3.1. Reference selection**

For precision capacitance measurement, the interface circuit needs to provide accurate signal processing, for which the reference plays an important role. The reference quality includes: stability, aging, tolerances, all of which are important when it comes to precision capacitance measurement.

From the discussion in Section 2.2, it became clear that the capacitive interface circuit works by comparing the unknown capacitance with a reference capacitance, or an equivalent reference capacitance that is built from a combination of other references. The ultimate precision of the measurement is thus determined by the quality of the reference that is used in the system.

The selection of the reference used in a capacitive interface circuit is determined by the accuracy requirements of the targeted application. In most of the literature that we could find, the stability of the reference used in the capacitive sensor interface circuit was not separately discussed. The reason is that for most capacitance measurement systems, the absolute accuracy of measurement is often not that important. For instance, the capacitive humidity sensor discussed in [3] aims for an accuracy in the order of 1%, because the target humidity-sensing error after calibration is only in the order of 1%. In such cases, a reference capacitance is the natural reference choice, since a comparison with the unknown capacitance can be directly made.

However, capacitive references have limited accuracy, and even after calibration, show noticeable temperature drift and aging. In [5], a benchmark of possible capacitance references shows that the best available off-the-shelf capacitors have a roughly 30 ppm/°C temperature drift, 0.1 % tolerance and 300 ppm/year time drift (aging). The study also shows that the better the quality of the capacitor, the bulkier it is. For example, capacitive standards used in metrology have a thermal drift of only 2 ppm/°C,  $\pm 0.005\%$  tolerance, and below 20 ppm/year aging [5]. However, those capacitance references are enormous in size and not practical.

The integrated capacitors have a comparable temperature coefficient. Both Metal-Insulator-Metal (MIM) and Polysilicon-Insulator-Polysilicon (PIP) capacitors report a nearly 30 ppm/°C temperature coefficient, while their long-term drift is often not reported.

Fig. 2.11: Charge-balancing that measures a sensor capacitor with the combination of a precision resistor reference and precision frequency reference.

On the other hand, as was pointed out in [5], both resistive references and frequency/time references exist that have better accuracy and stability than practically available capacitive references. For instance, VPG VHA412Z metal foil resistors have a rated temperature coefficient of 2 ppm/°C and a long-term drift of 2 ppm/6 years [49], while commercially available temperature-compensated crystal oscillators provide accuracy up to 0.1 ppm while having a sub-ppm/°C level temperature coefficient [50]. Although both components are still off-chip, their sizes are much smaller compared to the primary capacitance standard.

Despite the added complexity of comparing an unknown capacitor with an equivalent capacitive reference, the design with a resistive and frequency reference has the potential of achieving better accuracy and long-term stability. By utilizing ultra-stable reference resistors and a crystal oscillator, the interface circuit in [5] achieves thermal stability of  $\pm$  7.5 ppm/°C, which also demonstrates good long-term stability.

#### 2.3.2. Speed-accuracy trade-off

From the point of view of the measurement accuracy, it is clear from the last section that because of the better stability offered by resistive and frequency references, a capacitive interface based on these types of references could have both better thermal and long-term stability. However, since the comparison between an unknown capacitor and an 'equivalent' reference capacitor created by a reference resistor and a crystal oscillator is not a direct one, there are also limitations with respect to power efficiency.

The design in [5] employs a  $\Sigma\Delta$ -based CDC with two charge balancing branches, as shown in Fig. 2.11. The unknown capacitor is used to create a switched-capacitor branch, just as in a conventional  $\Sigma\Delta$ -based CDC. The reference resistor is first converted into current by a resistance-to-current converter, using a reference voltage  $V_{EXC}$ . Then, the combination of this current and a crystal-based time reference generates an equivalent reference charge. The sensor capacitor is incorporated into a switched-capacitor circuit which turns the sensor capacitance into a signal charge using the same reference voltage  $V_{EXC}$ . The modulator balances the signal charge against the charge supplied by the reference current. Since both the signal charge and the reference charge are proportional to  $V_{EXC}$ , the output is thus insensitive to the exact value and the drift of  $V_{EXC}$ , provided that the drift of  $V_{EXC}$  is much slower than the conversion time.

While this principle works reasonably well at lower speeds (clock frequency of 200 kHz in [5]), achieving the same level of performance while greatly improving the measurement speed is challenging, as two major limitations are present. First, the finite speed at which the switches turn the reference current, which has a continuous-time nature, on and off will create clock non-idealities. Second, the finite speed of the resistance-to-current converter also limits the maximum operating speed of this type of CDC [5].

It seems very difficult to find a single interface circuit that can achieve both high speed and high accuracy. However, from a system-level point of view, the problem can potentially be solved.

#### 2.3.3. System-level solution

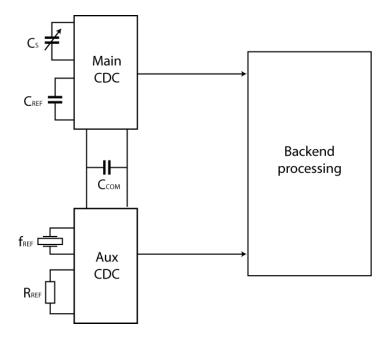

It is important to understand that solving all issues with a single design is not necessary. In fact, we can combine different designs to construct a capacitance measurement system, in which each design inside the system addresses one or several specific properties.

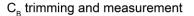

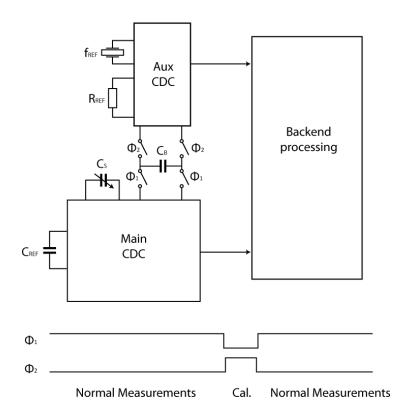

This idea is further illustrated in the block diagram shown in Figure 2.12. A high-speed, high-resolution, low-power CDC (main CDC) can be built by utilizing a good capacitor as its reference. Since no reference conversion is needed, by directly using a capacitor as the reference of the CDC the circuit solution can be quite straightforward. At the same time, being a switched-capacitor circuit, it is less prone to many circuit errors such as clock jitter, etc. [17]. To deal with the slow drifting of the capacitance reference value due to temperature and aging, an additional low-speed, low-power and high-precision CDC (auxiliary CDC) can be used to periodically calibrate the reference capacitor inside the main CDC. Such a calibration can for instance be realized by consequently measuring the same capacitor with both the main CDC and auxiliary CDC, as shown in Fig. 2.12. The

Fig. 2.12: Capacitance measurement system composed of a fast main CDC and a slow but high-precision auxiliary CDC.

results can then be compared, and the calibration can be applied to the main CDC. The periodicity of the calibration will depend on the application precision requirement and the drift of the capacitance reference. The main CDC only needs to guarantee that the drift is negligible within a relatively short time between two calibrations, which is much easier to achieve.

#### 2.3.4. Placement of interface circuit

In some situations, the capacitive sensor is directly integrated on-chip where the interface circuit is located [3], whereas if the sensor fabrication technology is not compatible with that of the interface circuit, they are placed in the same package. The motivation here is to minimize the associated parasitic capacitance to ground, because excessive parasitic capacitance will not only degrade the achievable resolution of the interface circuit, but also loads the interface and causes extra energy consumption.

When interfacing an off-chip sensor, it is also the case that the best performance of an interface circuit can be achieved when it is integrated into the sensor head, thus avoiding the use of cables between the capacitive sensor and the interface circuit.

The sensor head of an advanced displacement sensor is very sensitive to variations in the environment such as temperature and humidity changes, because all these changes will affect the property of the sensor head. Therefore, it is important to keep the dissipation of the interface circuit from self-heating to a reasonable and constant level.

# 2.4. Conclusion

In this chapter, the background of capacitive displacement sensors and capacitance interface circuits is discussed. The discussion of the interface circuit is extended to the references used.

The biggest limiting factor on the sensor head is alignment, since stand-off distance must be minimized to maximize resolution. Advanced alignment techniques are required to bring down the stand-off distance, so that the dynamic range requirement of the interface circuit can be more realistic. Many interface principles for capacitive sensors are available, however, most of the interface circuits have relatively low precision and low stability, mainly due to the quality of the references used in those interface circuits. An alternative, more stable and more accurate reference struggles reaching a high conversion speed and good power efficiency.

A promising solution is to combine two interface circuits onto a single chip (a system-onchip) or in a single package (system-in-package): (i) one fast, highly sensitive and energyefficient interface operating continuously in real time, periodically calibrated by a (ii) second stable and accurate interface, which is "sleeping" between two calibrations and hence does not dissipate noticeable additional energy during normal operation.

The rest of the thesis presents an investigation of this approach with focus on the fast and energy-efficient interface. Methods are proposed, and implementations are reported which improve the conversion speed and the energy efficiency of the interface circuit using a capacitive reference. An accurate and stable, but relatively slow interface solution, which can be integrated with the solutions proposed here, is reported in [32].

### **References:**

- L. K. Baxter, Capacitive Sensors: Design and Applications. New York: IEEE Press, 1997.

- [2] W. Bracke, R. Puers and C. Van Hoof, Ultra Low Power Capacitive Sensor Interfaces. Dordrecht, the Netherlands: Springer, 2007.

- [3] Z. Tan, "Energy-efficient capacitive-sensor Interfaces," Ph.D. dissertation, Delft University of Technology, Delft, the Netherlands, 2013.

- [4] J. P. Van Schieveen, R. Yang, S. Nihtianov, and J. W. Spronck, "Performance optimization of a self-alignment system for capacitive sensors," in Mechatronics (ICM), 2011 IEEE International Conference on, 2011, pp. 648-653.

- [5] R. Yang, "A high-precision capacitive sensor system for displacement measurements," Ph.D. dissertation, Delft University of Technology, Delft, the Netherlands, 2015.

- [6] S. Xia, J. P. Van Schieveen, S. Nihtianov, and J. W. Spronck, "Concept evaluation of a high performance self-aligning capacitive displacement sensor," in Industrial Technology (ICIT), 2010 IEEE International Conference on, 2010, pp. 1575-1580.

- [7] J. C. Lotters, W. Olthuis, P. H. Veltink, and P. Bergveld, "A sensitive differential capacitance to voltage converter for sensor applications," Instrumentation and Measurement, IEEE Transactions on, vol. 48, pp. 89-96, 1999.

- [8] S. Xia and S. Nihtianov, "Power-efficient high-speed and high-resolution capacitive-sensor interface for sub-nanometer displacement measurements," Instrumentation and Measurement, IEEE Transactions on, vol. 61, pp. 1315-1322, 2012.

- [9] C. Cheng-Ta, W. Chi-Shen, and H. Yu-Chung, "A monolithic CMOS auto compensated sensor transducer for capacitive measuring systems," Instrumentation and Measurement, IEEE Transactions on, vol. 57, pp. 2472-2486, 2008.

- [10] A. Heidary and G. C. M. Meijer, "An integrated interface circuit with a capacitanceto-voltage converter as front-end for grounded capacitive sensors," Measurement Science and Technology, vol. 20, 2009.

- [11] W. Bracke, P. Merken, R. Puers, and C. Van Hoof, "Ultra-low-power interface chip for autonomous capacitive sensor systems," Circuits and Systems I: Regular Papers, IEEE Transactions on, vol. 54, pp. 130-140, 2007.

- [12] X. Zhang, M. Liu, B. Wang, H. Chen, et al., "A wide measurement range and fast update rate integrated interface for capacitive sensors array," Circuits and Systems I: Regular Papers, IEEE Transactions on, vol. PP, pp. 1-10, 2013.

- [13] S. A. Jawed, D. Cattin, M. Gottardi, N. Massari, et al., "A 828µW 1.8V 80dB dynamic range readout interface for a MEMS capacitive microphone," in Solid-State Circuits Conference, 2008. ESSCIRC 2008. 34th European, 2008, pp. 442-445.

- [14] S. Nihtianov, G. P. Shterev, B. Iliev, and G. C. M. Meijer, "An interface circuit for R-C impedance sensors with a relaxation oscillator," Instrumentation and Measurement, IEEE Transactions on, vol. 50, pp. 1563-1567, 2001.

- [15] J. H. L. Lu, M. Inerowicz, J. Sanghoon, K. Jong-Kee, et al., "A low-power, widedynamic-range semi-digital universal sensor readout circuit using pulse-width modulation," Sensors Journal, IEEE, vol. 11, pp. 1134-1144, 2011.

- [16] Z. Tan, S. H. Shalmany, G. C. M. Meijer, and M. A. P. Pertijs, "An energy-efficient 15-Bit capacitive-sensor interface based on period modulation," Solid-State Circuits, IEEE Journal of, vol. 47, pp. 1703-1711, 2012.

- [17] P. Bruschi, N. Nizza, and M. Piotto, "A current-mode, dual slope, integrated capacitance-to-pulse duration converter," Solid-State Circuits, IEEE Journal of, vol. 42, pp. 1884-1891, 2007.

- [18] C. Cheng-Ta, W. Chi-Shen, and H. Yu-Chung, "A CMOS integrated capacitanceto- frequency converter with digital compensation circuit designed for sensor interface applications," in Sensors, 2007 IEEE, 2007, pp. 954-957.

- [19] R. Aragones, X, P. Ivarez, J. Oliver, et al., "A capacitance-to-frequency converters comparison for a frequency acquisition platform," in Sensors, 2010 IEEE, pp. 1431-1436, 2010.

- [20] S. Chatzandroulis and D. Tsoukalas, "Capacitance to frequency converter suitable for sensor applications using telemetry," Analog Integrated Circuits and Signal Processing, vol. 27, pp. 31-38, 2001.

- [21] Y. He, Z. y. Chang, L. Pakula, S. H. Shalmany and M. Pertijs, "A 0.05mm2 1V capacitance-to-digital converter based on period modulation," 2015 IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers, San Francisco, CA, 2015, pp. 486-487.

- [22] S. M. Huang, A. L. Stott, R. G. Green, and M. Beck, "Electronic transducers for industrial measurement of low value capacitances," Journal of Physics E: Scientific Instruments, vol. 21, p. 242, 1988.

- [23] A. A. Helmy, J. Hyung-Joon, L. Yung-Chung, A. J. Larsson, et al., "A selfsustained CMOS microwave chemical sensor using a frequency synthesizer," Solid-State Circuits, IEEE Journal of, vol. 47, pp. 2467-2483, 2012.

- [24] H. Danneels, K. Coddens, and G. Gielen, "A fully-digital, 0.3V, 270 nW capacitive sensor interface without external references," in ESSCIRC (ESSCIRC), 2011

Proceedings of the, 2011, pp. 287-290.

- [25] C.-L. Dai, "A capacitive humidity sensor integrated with micro heater and ring oscillator circuit fabricated by CMOS-MEMS technique," Sensors and Actuators B: Chemical, vol. 122, pp. 375-380, March 26, 2007.

- W. Jung, S. Jeong, S. Oh, D. Sylvester and D. Blaauw, "27.6 A 0.7pF-to-10nF fully digital capacitance-to-digital converter using iterative delay-chain discharge," 2015

IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, 2015, pp. 484-485.

- [27] H. Fan, "A High-Resolution Capacitance-to-Digital Converter based on Iterative Discharging," M.Sc. thesis, Delft University of Technology, Delft, the Netherlands, 2017.

- [28] R. Gallorini and N. Abouchi, "A capacitance meter based on an oversampling sigma-delta modulator and its application to capacitive sensor interface," in Electronics, Circuits and systems, 2001. ICECS 2001. The 8th IEEE International Conference on, 2001, pp. 1537-1540, vol.3.

- [29] J. O'Dowd, A. Callanan, G. Banarie, and E. Company-Bosch, "Capacitive sensor interfacing using sigma-delta techniques," in Sensors, 2005 IEEE, p. 4, 2005.

- [30] S. Dong-Yong, L. Hyunjoong, and K. Suhwan, "A Delta Sigma interface circuit for capacitive sensors with an automatically calibrated zero point," Circuits and Systems II: Express Briefs, IEEE Transactions on, vol. 58, pp. 90-94, 2011.

- [31] S. Xia, K. Makinwa, and S. Nihtianov, "A capacitance-to-digital converter for displacement sensing with 17b resolution and 20µs conversion time," in Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2012 IEEE International, 2012, pp. 198-200.

- [32] Z. Tan, R. Daamen, A. Humbert, Y. V. Ponomarev, et al., "A 1.2-V 8.3-nJ CMOS humidity sensor for RFID applications," Solid-State Circuits, IEEE Journal of, vol. PP, pp. 1-1, 2013.

- [33] D. W. B. Bechen, T. v. d. Boom, B. J. Hosticka, "A 10 bit very low power CMOS SAR ADC for capacitive micro-mechanical pressure measurement in implants," in Adv. Radio Sci., pp. 243-246, 2006.

- [34] K. Tanaka, Y. Kuramochi, T. Kurashina, K. Okada, et al., "A 0.026mm2 capacitance-to-digital converter for biotelemetry applications using a charge redistribution technique," in Solid-State Circuits Conference, 2007. ASSCC '07. IEEE Asian, 2007, pp. 244-247.

- [35] Y. K. Tuan Minh Vo, M. Miyahara, T. Kurashina and A. Matsuzawa, "A 10-bit 290fJ/conv. steps, 0.13mm2, zero-static power self-clocking capacitance to digital converter," in Proc. SSDM, 2009.

- [36] A. Heidary, "A low-cost universal integrated interface for capacitive sensors," Ph.D. dissertation, Delft University of Technology, Delft, the Netherlands, 2011.

- [37] H. Ha, D. Sylvester, D. Blaauw and J. Y. Sim, "A 160nW 63.9fJ/conversion-step capacitance-to-digital converter for ultra-low-power wireless sensor nodes," 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, 2014, pp. 220-221.

- [38] A. Heidary and G. C. M. Meijer, "Features and design constraints for an optimized SC front-end circuit for capacitive sensors with a wide dynamic range," IEEE Journal of Solid-State Circuits, vol. 43, no. 7, July 2008, pp. 1609-1616.

- [39] A. Heidary, S. Heidary Shalmany and G. C. M. Meijer, "A flexible low-power highresolution integrated interface for capacitive sensors," in Proc. Int. Symp. on Industrial Electronics (ISIE), July 2010, pp. 3347-3350.

- [40] P. Bruschi, N. Nizza and M. Dei, "A low-power capacitance to pulse width converter for MEMS interfacing," ESSCIRC 2008 - 34th European Solid-State Circuits Conference, Edinburgh, 2008, pp. 446-449.

- [41] A. Sanyal and N. Sun, "An energy-efficient hybrid SAR-VCO ΔΣ capacitance-todigital converter in 40-nm CMOS," in IEEE Journal of Solid-State Circuits, vol. 52, no. 7, pp. 1966-1976, July 2017.

- [42] D.-Y. Shin, H. Lee and and S. Kim, "A delta-sigma interface circuit for capacitive sensors with an automatically calibrated zero point," IEEE Trans. Circuits and Systems II, vol. 58, no. 2, pp. 90-94, Feb. 2011.

- [43] Z. Tan, R. Daamen, A. Humbert, K. Souri, Y. Chae, Y. V. Ponomarev and M. A. P. Pertijs, "A 1.8V 11μW CMOS smart humidity sensor for RFID sensing applications," in Proc. IEEE Asian Solid-State Circuits Conference (A-SSCC), Jeju, Korea, Nov. 2011, pp. 105-108.

- [44] R. Yang, M. A. P. Pertijs and S. Nihtianov, "A precision capacitance-to-digital converter with 16.7-bit ENOB and 7.5-ppm/°C thermal drift," in IEEE Journal of Solid-State Circuits, vol. 52, no. 11, pp. 3018-3031, Nov. 2017.

- [45] S. Oh, W. Jung, K. Yang, D. Blaauw and D. Sylvester, "15.4b incremental sigmadelta capacitance-to-digital converter with zoom-in 9b asynchronous SAR," 2014 Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, 2014.

- [46] B. Yousefzadeh, W. Wu, B. Buter, K. Makinwa and M. Pertijs, "A compact sensor readout circuit with combined temperature, capacitance and voltage sensing functionality," 2017 Symposium on VLSI Circuits, Kyoto, 2017, pp. C78-C79.

- [47] H. Omran, M. Arsalan and K. N. Salama, "A robust parasitic-insensitive successive approximation capacitance-to-digital converter," Proceedings of the IEEE 2014 Custom Integrated Circuits Conference, San Jose, CA, 2014, pp. 1-4.

- [48] H. Omran, A. Alhoshany, H. Alahmadi and K. N. Salama, "A 33fJ/Step SAR capacitance-to-digital converter using a chain of inverter-based amplifiers," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 64, no. 2, pp. 310-321, Feb. 2017.

- [49] New generation of secondary standards hermetically sealed construction ultra-highprecision Z-foil technology resistors with TCR of  $\pm$  0.2 ppm/°C, tolerance of  $\pm$ 0.001 % and load life stability of  $\pm$  0.002 % [Online]. Available: www.vishayfoilresistors.com

- [50] Agilent, "Fundamentals of Quartz oscillators," in Application Note 200-2, ed.

# Chapter 3

# High-Speed High-Precision Capacitive Sensor Interface with Baseline Capacitance Compensation

# **3.1. Introduction**

As discussed in the previous chapter, capacitive sensor interface circuits based on a capacitive reference suffer from low stability, mainly due to the limited stability of the capacitive reference. On the other hand, circuits that utilize a more stable and more accurate reference have been shown to have difficulty in achieving a high conversion speed. Towards the end of Chapter 2, it was shown that it is possible to split the functionality of the capacitive sensor interface into two types of operation. The first is a real-time high-speed, high-resolution, low-power operation with the addition of an auto-alignment function in the sensor head (mechanical zoom-in), and the second is a low-speed, high-stability, high-precision and relatively low-power operation, to be used periodically for self-calibration. In this chapter, the focus will be on the investigation of a capacitive sensor interface with real-time high-resolution and low-power.

In order to build an interface circuit that can achieve a high speed, high resolution, and at the same time low power consumption, we can first try to determine the limiting factors that impede this goal. From Chapter 2 we know that most capacitive sensors suffer from a small modulation factor which results in a relatively large baseline capacitance. This baseline capacitance increases the dynamic range requirement for the interface dramatically and limits the achievable energy efficiency of the interface circuit. Therefore, this baseline capacitance would need to be processed.

# **3.2. Baseline Capacitance Compensation Principle**

The most significant limiting factor for increasing the sensitivity of a capacitive displacement sensor is the minimum amount of stand-off distance to the target which is necessary to compensate for any misalignment of the sensor plates [1]. Although with advanced alignment techniques the stand-off distance could be reduced to tens of micrometers [2], it would still be too large when a limited displacement needs to be measured in the nanometer range. As discussed in Section 2.1, this limit on the stand-off distance would result in a small modulation factor and lead to reduced sensitivity and increased demand on the dynamic range of the interface circuit. Eventually this would lead to energy being wasted, which in capacitive sentence interface circuits located close to the sensor head must be avoided due to stringent power consumption requirement. This section focuses on the circuit technique that can help increase the energy efficiency of a capacitive sensor interface circuit.

#### 3.2.1. Baseline sensor capacitance

For all the capacitive interface principles illustrated in the previous chapter, the allowable variation range of the input capacitance can span from zero to a maximum value that is

Fig. 3.1: Baseline capacitance compensation.

determined by the circuit parameters of the interface circuit. In the case of the chargebalancing principle, for instance, the maximum allowable sensor capacitance value should not exceed the value of the reference capacitor. The maximum input capacitance to be handled by the interface circuit is determined by the maximum expected value of the sensor capacitance, while the minimum detectable variation of the capacitance is defined by the interface resolution.

It is important to note than the measurement range of a capacitive sensor never starts from zero. In the case of a parallel-plate capacitive displacement sensor, zero capacitance translates into an infinite plate distance. When the displacement measurement range is specified, the capacitance variation range is also determined. In most cases, the full range of the capacitive interface circuit is not utilized in an optimal way, leading to a waste in energy consumption. The static part of the capacitance that makes up for the sensor capacitance is sometimes called baseline capacitance. Since for a capacitive sensor the interest is often in the variation component, it is desired to have the baseline capacitance removed.

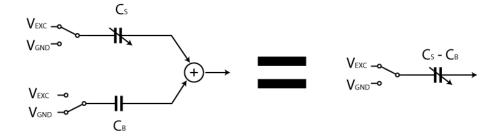

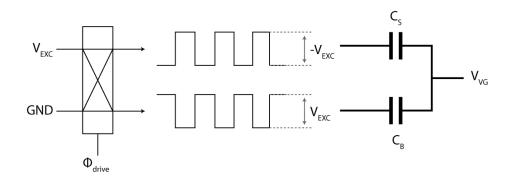

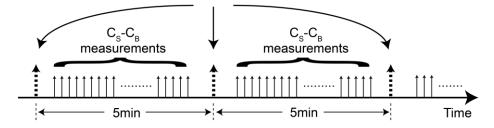

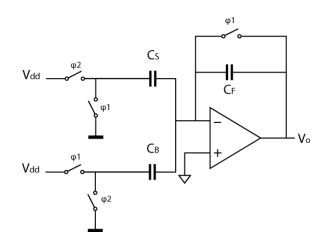

One of the most commonly used methods to electrically cancel the baseline capacitor is shown in Fig. 3.1 [3,4]. Conceptually we can split the sensor capacitor  $C_S$  into the baseline capacitor  $C_B$  and the signal capacitance  $C_X$ . Since the baseline capacitance  $C_B$  contributes to a charge amounting to  $V_{EXC} \cdot C_B$ , if we create a charge that amounts to  $V_{EXC} \cdot C_B$  and subtract that from the charge contributed by the sensor capacitor, it is then equivalent to removing the baseline capacitance. This can be realized by physically connecting another capacitor with a value equal to  $C_B$ , to the circuit and applying an excitation signal  $V_{EXC}$  with an opposite sign. Since the charge contributed becomes  $-V_{EXC} \cdot C_B$ , the net effect is

Fig. 3.2: Baseline capacitance compensation with adjustable  $C_B$ .

equivalent to  $C_B$  being removed from the sensor capacitor  $C_S$  in the transfer function of the interface circuit. The dynamic range of the interface circuit after the removal of the base capacitance needs only to cover the varying part of the sensor capacitance, which is often much smaller. The range of the capacitive sensor interface has been effectively zoomed in to the range of interest. We name the factor between the baseline compensation capacitor and the capacitance variation range of the interface circuit with baseline capacitor compensation the "zoom-in factor"  $\alpha_Z$  [1]:

$$\alpha_Z = \frac{C_B}{C_{S-max} - C_{S-min}} \tag{3.1}$$

Baseline capacitance compensation can be applied to most of the capacitive sensor interfacing principles discussed in Section 2.2, with a few exceptions. Generally speaking, circuits that employ an active amplifier and have a virtual ground node are best suited for implementing the baseline capacitance compensation. Other than those circuits, a SAR-based interface with passive charge redistribution, as discussed in Section 2.2.4, can also incorporate baseline capacitance compensation, given that the parasitic capacitance to ground is small enough. Circuits where baseline capacitance compensation cannot be implemented include circuits based on ring oscillators and LC oscillators, where a charge subtraction cannot be facilitated.

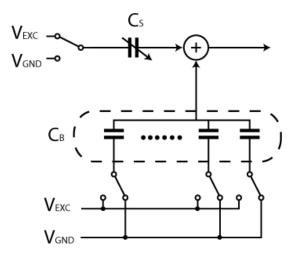

In cases where the baseline capacitance is a fixed part of the sensor capacitor,  $C_B$  can be realized with an invariable capacitor. However, that baseline capacitance is also a subject to variations due to mounting tolerances and drift [5]. Moreover, the capacitor  $C_B$  can deviate from its nominal value due to process variations. This is especially a problem when the baseline capacitance takes up much larger portion of the sensor capacitance, compared to the signal-carrying part of the sensor capacitance. In this case a small change in the baseline capacitance will already be equivalent to the sensor variation range. In order to avoid out-of-range operation, the gain applied in baseline capacitance compensation must be limited, reducing the dynamic range advantage that could be gained with this technique.

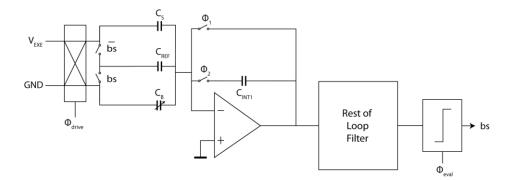

This issue can be partially solved by making the baseline capacitor  $C_B$  adjustable [4], as shown in Fig. 3.2. In the initialization phase, an algorithm such as a successive approximation register algorithm can be used to determine the approximate value of the baseline part of the sensor capacitor by adjusting the value of  $C_B$  according to the relative size of  $C_B$  and  $C_S$ , which is available through a comparison algorithm similar to the successive approximation algorithm. This would also allow the interface circuit to cover a wider sensing capacitance variation range, while still maintaining a high zoom-in factor within each sub-range.

# **3.2.2.** Circuit implementation issues of baseline capacitance compensation

Although there are many advantages of applying baseline capacitance compensation to capacitive sensor interface circuits, so far we have only discussed the benefits. However, it makes sense to also point out the implications of applying such a technique from a circuit design point of view, as these implications have a great impact on circuit performance, especially when the desired zoom-in factor becomes large.

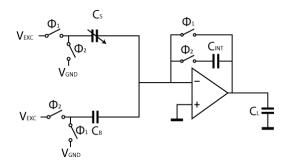

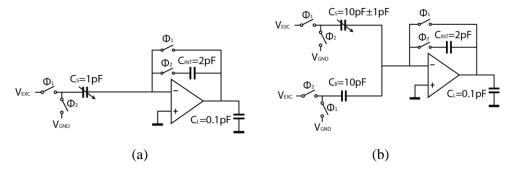

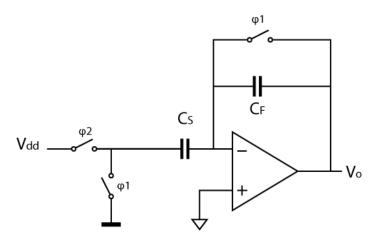

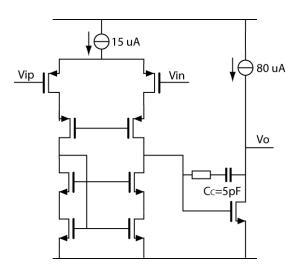

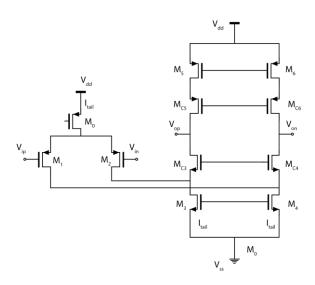

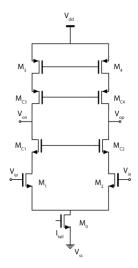

We begin our analysis by first studying a typical switched-capacitor integrator stage as shown in Fig. 3.3. The circuit works in two phases. In  $\Phi_1$  the OTA is set to unity-feedback mode and the input capacitors are reset, while in  $\Phi_2$  the charge is transferred from the input capacitors onto the integration capacitor. The amount of charge that is transferred to the integration capacitor can be approximated as:

$$V_o = V_{EXC} \frac{c_S - c_B}{c_{INT}} \tag{3.2}$$

Here it is assumed that the OTA holds the virtual ground node still and that the voltage remains unchanged before and after the charge transfer. In reality, for various reasons, the virtual ground voltage will change slightly, which in turn leads to an error term in Eq. 3.2.