Delft University of Technology

# Testing STT-MRAM: Manufacturing Defects, Fault Models, and Test Solutions

Wu, L.

DOI 10.4233/uuid:088a3991-4ea9-48a0-9b92-cc763748868c

**Publication date** 2021

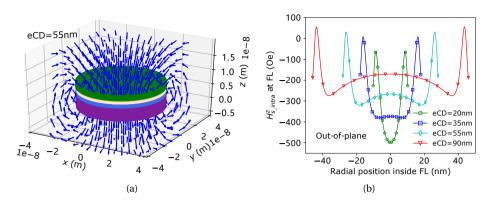

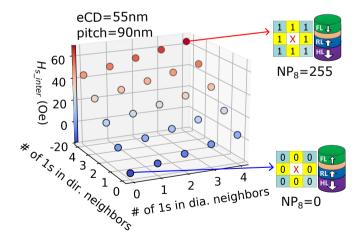

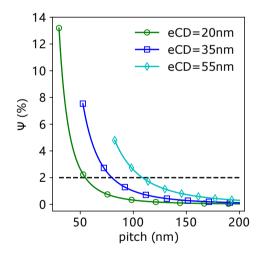

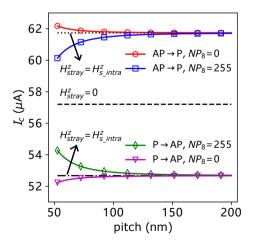

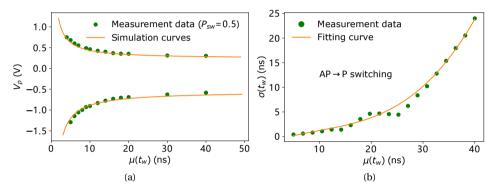

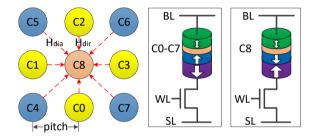

**Document Version** Final published version

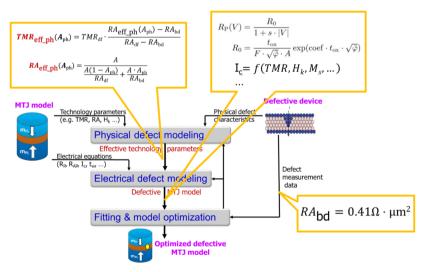

Citation (APA)

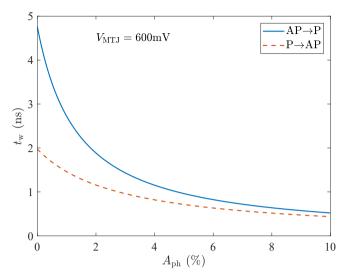

Wu, L. (2021). Testing STT-MRAM: Manufacturing Defects, Fault Models, and Test Solutions. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:088a3991-4ea9-48a0-9b92cc763748868c

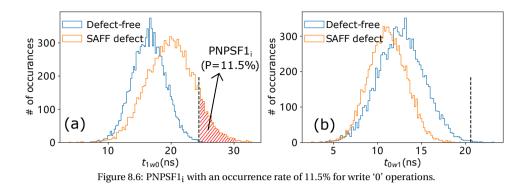

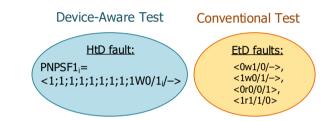

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

# Testing STT-MRAM: Manufacturing Defects, Fault Models, and Test Solutions

# TESTING STT-MRAM: MANUFACTURING DEFECTS, FAULT MODELS, AND TEST SOLUTIONS

# TESTING STT-MRAM: MANUFACTURING DEFECTS, FAULT MODELS, AND TEST SOLUTIONS

# Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus prof. dr. ir. T.H.J.J. van der Hagen chair of the Board for Doctorates to be defended publicly on Monday 22 February 2021 at 15:00 o'clock

by

# Lizhou WU (吴利舟)

Master of Engineering in Computer Science & Technology National University of Defense Technology, China born in Quzhou, Zhejiang, China This dissertation has been approved by the promotors.

Composition of the doctoral committee:

| Rector Magnificus         | chairperson                                |

|---------------------------|--------------------------------------------|

| Prof. dr. ir. S. Hamdioui | Delft University of Technology, promotor   |

| Dr. ir. M. Taouil         | Delft University of Technology, copromotor |

*Independent members:* Prof. dr. K.A.A. Makinwa Prof. dr. M. Sachdev Prof. dr. P. Girard Dr. S. Rao Dr. B. Kruseman Prof. dr. ir. W.A. Serdijn

Delft University of Technology University of Waterloo, Canada LIRMM Laboratory, France IMEC, Belgium NXP Semiconductors, the Netherlands Delft University of Technology, reserve member

unec

*Keywords:* memory test, device-aware test, manufacturing test, STT-MRAM, MTJ, manufacturing defect, fault model, robust design, magnetic coupling

Printed by: Ipskamp Printing, the Netherlands

Front & Back: designed by Yu Zhang & Lizhou Wu

Copyright © 2020 by Lizhou Wu Author email: njuwulizhou@163.com

ISBN 978-94-6384-199-3

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

Dedicated to: my parents for raising me up and supporting me in education, my wife for encouraging and accompanying me in this journey.

# **SUMMARY**

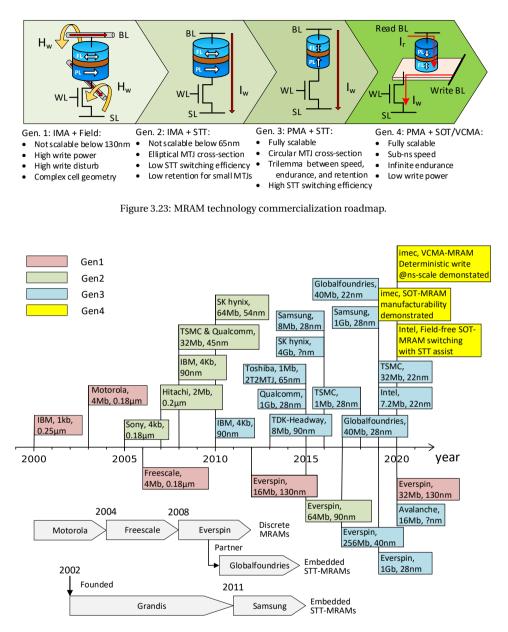

As one of the most promising emerging memory technologies, spin-transfer torque magnetic random access memory (STT-MRAM) offers non-volatility, fast access speed, high density, nearly unlimited endurance, radiation immunity, and low-power consumption. Thanks to these advantageous features, STT-MRAM is customizable as both embedded and discrete memory solutions for a variety of applications such as enterprise SSD, AIoT, automotive, and aerospace. Therefore, numerous start-ups (e.g., Everspin) have been founded focusing on STT-MRAM commercialization, and major foundries worldwide (e.g., TSMC, Samsung, and Intel) also invest heavily on it. As STT-MRAM mass production and deployment in industry is around the corner, high-quality yet cost-efficient manufacturing test solutions are needed to ensure the required quality of products being shipped to end customers.

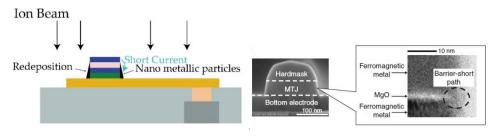

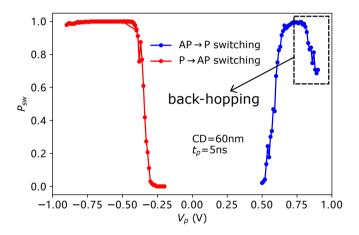

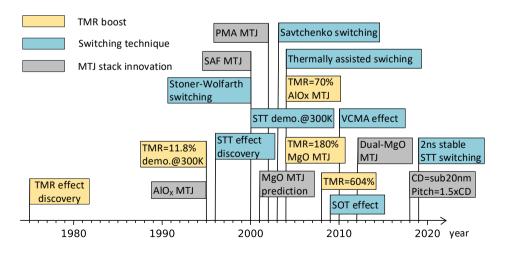

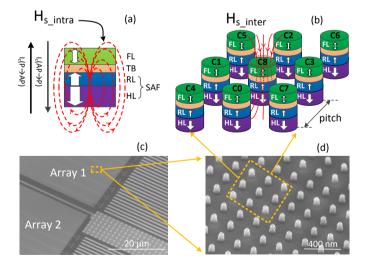

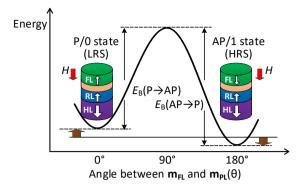

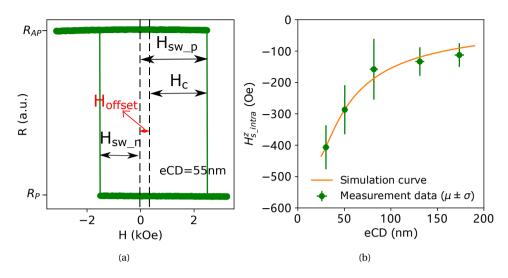

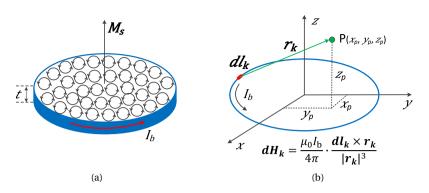

This dissertation mainly focuses on robust design and high-quality test for STT-MRAM. We first investigate the manufacturing process of STT-MRAM and physical defects that may take place in each step based on literature survey and silicon measurements. Special attentions are given to those unique steps and defects related to the fabrication of magnetic tunnel junction (MTJ) devices, which are the data-storing elements in STT-MRAMs. We build a complete STT-MRAM simulation platform, composed of a Python simulation controller and an STT-MRAM circuit design. The former controls and automates all simulation procedures, whereas the latter is a circuit netlist consisting of a 1T-1MTJ memory array and peripheral circuits such as write drivers and sense amplifiers. To enable fast and accurate electrical/magnetic co-simulations of STT-MRAM, we propose a magnetic-field-aware compact model for MTJs with perpendicular magnetic anisotropy; it is optimized and calibrated with comprehensive measurement data of MTJ devices fabricated at imec. This model can be used for robust device/circuit co-design of STT-MRAM under PVT variations and various magnetic configurations including external disturbance fields and internal magnetic coupling effects.

Based on this simulation platform, we explore STT-MRAM testing with the conventional fault modeling and test approach. In this approach, any physical defect irrespective of its physical nature is modeled as a linear resistor (i.e., open, short, or bridge), which is then injected into our STT-MRAM netlist for fault analysis. Test development is also covered based on the fault modeling results. Although it is convincing to model defects in interconnects as linear resistors, this approach has never been validated for defects inside semiconductor devices such as MTJ. Based on comprehensive characterization on fabricated MTJ devices, we demonstrate that modeling an MTJ-internal defect as a linear resistor is inaccurate. This is because linear resistors cannot reflect the defectinduced changes in MTJ's magnetic properties which are as important as electrical ones. Furthermore, we experimentally observed extremely low, intermediate, and extremely high resistances in some defective MTJs; these resistance values are out of the specification of logic '0' and '1'. We also observed that some MTJ faulty behaviors are intermittent rather than permanent. Hence, the conventional fault modeling and test approach is unable to derive high-quality test solutions for STT-MRAMs.

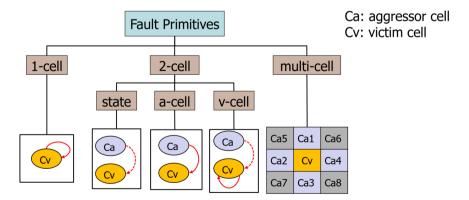

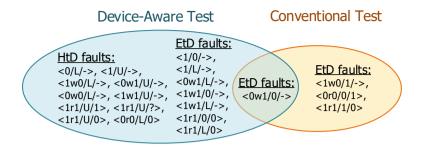

To address these issues, we propose Device-Aware Test (DAT) approach which goes beyond cell-aware test and specifically targets device-internal defects. DAT consists of three steps: 1) device-aware defect modeling, 2) device-aware fault modeling, and 3) device-aware test development. In the first step, a physical defect is characterized and modeled physically; the impact of the defect on the technology parameters of the defective device is determined. Subsequently, such impact is incorporated into the device's electrical parameters to obtain a parameterized defective device model which can be calibrated by silicon data if available. In the second step, we define a complete fault space using an upgraded fault primitive notation to cover all possible resistive states in STT-MRAMs; a systematic fault analysis is then performed to validate realistic faults within the pre-defined fault space in the presence of the defect. Finally, the obtained faults are used to develop appropriate test solutions; e.g., March tests, DfT designs, and stress tests.

We have applied the proposed DAT to three key types of MTJ-internal defects as casestudies in this thesis. They are pinhole defects, synthetic anti-ferromagnet flip (SAFF) defects, and intermediate (IM) state defects. For each type of MTJ defects, we perform comprehensive characterization on fabricated MTJ devices, and develop a defective MTJ compact model with defect parameters as inputs; the model is also calibrated with the measured silicon data. By applying device-aware fault modeling, accurate and realistic faults are obtained. Comparing the results to those obtained using the conventional approach reveals two observations: 1) The conventional approach leads to wrong fault models which in turn would lead to test escapes and a waste of test time and resources; 2) Our DAT approach results in more accurate fault models which reflect the physical defects, thus ensuring high-quality tests at minimal cost. With the obtained faults using our DAT approach, we propose optimized test solutions for the above-mentioned three types of MTJ-internal defects.

# SAMENVATTING

Als een van de meest veelbelovende opkomende geheugentechnologieën biedt spintransfer torque magnetic random access memory (STT-MRAM) niet-vluchtigheid, hoge lees- en schrijfsnelheid, hoge dichtheid, nagenoeg onbeperkt schrijfuithoudingsvermogen, een hoge robuustheid tegen straling en een laag energieverbruik. Deze eigenschappen zorgen dat STT-MRAM zowel kan worden toegepast als ingebedde en als discrete geheugenoplossing voor een verscheidenheid aan applicaties, zoals enterprise SSD, kunstmatige intelligentie voor het internet der dingen en in de auto-, lucht- en ruimtevaartindustrie. Daarom zijn er talloze startups (bijv. Everspin) opgericht die zich richten op de commercialisering van STT-MRAM, maar ook grote chipproducenten over de gehele wereld (bijv. TSMC, Samsung en Intel) doen grote investeringen in deze technologie. Aangezien de massaproductie en -implementatie van STT-MRAM nabij is, zijn hoogwaardige maar toch kostenefficiënte productietestoplossingen cruciaal om de vereiste kwaliteit van de producten die naar de eindklanten worden verzonden te garanderen.

Dit proefschrift richt zich voornamelijk op het robuust ontwerpen en het ontwikkelen van hoogwaardige tests voor STT-MRAM. We onderzoeken eerst het fabricageproces van STT-MRAM en de fysieke defecten die in elke stap kunnen optreden op basis van literatuuronderzoek en siliciummetingen. Speciale aandacht wordt geschonken aan de unieke stappen en defecten die verband houden met de fabricage van de magnetische tunneljunctie (MTJ), welke het gegevensopslagelement is in STT-MRAM's. We ontwikkelen een compleet STT-MRAM-simulatieplatform, bestaande uit een simulatiecontroller geschreven in Python en een STT-MRAM-circuitontwerp. De eerstgenoemde controleert en automatiseert alle simulatieprocedures, terwijl de laatstgenoemde een circuitbeschrijving is van een 1T-1MTJ-geheugenraster en randcircuits zoals schrijfcircuits en leesversterkers. Om snelle en nauwkeurige elektrische/magnetische co-simulaties van STT-MRAM mogelijk te maken, introduceren we een compact model voor MTJ's met loodrechte magnetische anisotropie, dat rekening houdt met het magnetisch veld. Het model is geoptimaliseerd en gekalibreerd met uitgebreide meetgegevens van MTJ's die bij imec zijn vervaardigd. Dit model kan worden gebruikt om robuuste MTJ's en STT-MRAM-circuits te ontwerpen met inachtneming van proces-, spannings- en temperatuurvariaties alsook verschillende magnetische configuraties, waaronder externe storingsvelden en interne magnetische koppelingseffecten.

Op basis van dit simulatieplatform bestuderen we het testen van STT-MRAM middels de conventionele foutmodellerings en testbenadering. In deze benadering wordt elk fysiek defect, ongeacht zijn fysieke aard, gemodelleerd als een lineaire weerstand (d.w.z. als een open verbinding, een kortsluiting of een overbruggingsverbinding), die vervolgens wordt toegevoegd aan ons STT-MRAM-circuitontwerp voor foutanalyse. Testontwikkeling wordt ook behandeld op basis van de foutmodelleringsresultaten. Hoewel het overtuigend is om defecten in verbindingen te modelleren als lineaire weerstanden, is deze benadering nooit gevalideerd voor defecten in halfgeleidercomponenten zelf, zoals in MTJ's. We laten op basis van uitgebreide karakterisering van gefabriceerde MTJ's zien dat het modelleren van een intern MTJ-defect als een lineaire weerstand onnauwkeurig is. Dit komt doordat lineaire weerstanden de door defecten veroorzaakte veranderingen in de magnetische eigenschappen van MTJ, die even belangrijk zijn als elektrische, niet kunnen weerspiegelen. Daarnaast hebben we extreem lage en extreem hoge weerstanden alsook weerstanden die tussen de twee gewenste weerstandswaarden liggen experimenteel waargenomen in sommige defecte MTJ's. Deze weerstandswaarden vallen buiten de specificaties van een logische '0' en '1'. We hebben ook vastgesteld dat het foutieve gedrag van sommige defecte MTJ's niet permanent is maar met tussenpozen optreedt. Om deze redenen is het onmogelijk om met de conventionele foutmodelleringsen testbenadering hoogwaardige testoplossingen voor STT-MRAM te genereren.

Om deze problemen aan te pakken, stellen we een Componentbewuste Test (CBT) -benadering voor die verder gaat dan celbewuste tests en specifiek gericht is op interne defecten van de component. De CBT-benadering bestaat uit drie stappen: 1) componentbewuste defectmodellering, 2) componentbewuste foutmodellering en 3) componentbewuste testontwikkeling. In de eerste stap wordt een productiedefect gekarakteriseerd en de consequenties ervan gemodelleerd. Hiermee wordt de uitwerking van het defect op de technologieparameters van de defecte component bepaald. Vervolgens wordt de impact opgenomen in de elektrische parameters van de component om een geparametriseerd model van de defecte component te verkrijgen dat, indien beschikbaar, kan worden gekalibreerd met siliciummetingen. In de tweede stap definiëren we een volledige foutruimte met behulp van een verbeterde notatie van foutprimitieven om alle mogelijke weerstandstoestanden in STT-MRAM's te beschrijven. Vervolgens wordt een systematische foutanalyse uitgevoerd om de foutruimte te valideren in de aanwezigheid van een defect en dus realistische fouten te determineren. Ten slotte worden de gevalideerde fouten gebruikt om geschikte testoplossingen te ontwikkelen. Dit kunnen bijvoorbeeld marcheertests, ontwerp-voor-test-structuren en stresstests zijn.

In dit proefschrift passen wij als casestudy de CBT-benadering toe op drie belangrijke MTJ-defecten. Deze defecten zijn: een minuscule gaten in de MgO-tunnelbarrière, synthetische anti-ferromagnetische omkeringsdefecten en tussenliggende-toestanddefecten. Voor elk MTJ-defect voeren we een uitgebreide karakterisering uit op gefabriceerde MTJ's en ontwikkelen we een compact MTJ-defectmodel met defectparameters als invoer; het model is tevens gekalibreerd aan de hand van de uitgevoerde metingen. Door componentbewuste foutmodellering toe te passen, worden nauwkeurige en realistische fouten gevonden. Wanneer de resultaten van deze aanpak vergeleken worden met die verkregen middels de conventionele benadering, kunnen de volgende twee waarnemingen gemaakt worden. (1) De conventionele aanpak leidt tot verkeerde foutmodellen die op hun beurt zouden leiden tot valsnegatieve testresultaten en verspilling van testtijd en -middelen. (2) Onze CBT-benadering resulteert in nauwkeurigere foutmodellen die de werkelijke productiedefecten beschrijven, waardoor hoge testkwaliteit tegen minimale kosten kan worden gegarandeerd. We leggen voor elk van de drie bovengenoemde interne MTJ-defecten geoptimaliseerde testoplossingen voor die gebaseerd zijn op de fouten verkregen middels onze CBT-benadering.

# **ACKNOWLEDGEMENTS**

The year 2020 represents crisis and hardship to most people, as the novel coronavirus hits every corner in the world. To me, this year has a special meaning apart from COVID-19. After doing research for four years in pursuit of the PhD degree, I am so delighted that I will be soon hitting the finish line. Four years' investment with hard working day and nigh, eventually results in a small book advancing the state of the art a little bit in the knowledge of human being. Pretty cool and worth it! During this tough "marathon", there are obviously a lot of ups and downs. At this moment, when looking back, I feel so grateful to all who appear in my life, especially those who helped me in accomplishing this dissertation which I consider as the best achievement in my life so far.

First of all, I would like to express my deepest gratitude to my supervisory team at TU Delft: Prof.dr.ir. Said Hamdioui and Dr.ir. Mottaqiallah Taouil. A big thanks to my promotor and daily supervisor Said. Thank you for getting me on board and providing me with an unbelievable platform to carry out research work. Thank you for giving me hard time in writing papers and in preparing presentations. In my first year, you taught me how to do research by quoting an old Chinese proverb: teaching someone how to fish is better than just giving him a fish (授人以鱼不如授人以渔). You taught me how to think critically and independently. This covers the entire cycle in research; it applies when we review someone else's work, when we look for research issues, when we discuss my progress, when we revise papers together, when we polish slides for conference presentations. No matter how busy you are, you always manage to join my progress meetings and correct my paper manuscripts. In addition, You emphasize the importance of collaboration in research, which I benefit from significantly especially when collaborating with imec. Looking back, there are so many vivid moments popping up in my mind. When you were correcting my first ITC paper at TU Delft in 2017, you praised me for doing a good job in writing the introduction section. Frankly speaking, that was such a great encouragement to me after being overwhelmed by depression in my first year. But of course, I was happy to hear that and did not tell you the paper had been corrected by Motta many times already. Earlier this year, we were preparing another paper for ITC submission. On a beautiful Sunday, April 12, you sent me an email, saying that "I have to say that you have really learned how to write! I am very impressed with the quality which shows how much you improved!" Being your student, I am used to your critical style of education, and this came so surprisingly. Thank God, this made me happy for the entire week. After four years' training process with your guidance, I am proud to say that I am an independent "fisherman" now. I would also like to thank Motta who is my co-promotor and daily supervisor as well. Thank you for brainstorming with me and helping me improve my writing skills. Honestly, the first year of my PhD is definitely not a sweet memory. I will not forget the comfort and encouragement you gave me when I was in frustration. Also, I will take the original manuscripts of my first ITC paper with full of your corrections and comments back to China and keep them for the rest of my life. In recent years, you have your hardware security group and are getting busier and busier, but you still manage to be an active member in our STT-MRAM testing team. I am very lucky to have a supervisor like you who is also my friend and mentor. When I have problems in work or personal issues, you are always there for help. You are a big bro who cares about students' feelings and always clears up a messy situation for us. You also serve as a bridge between students and Said. Said is the bitter flavor in life, and you are the sweet one. Don't say that you are too nice to students, we appreciate your nice trait which is so precious. Thank you, Motta, for adding sugar in my PhD life.

I also want to thank my supervisors: Dr. Siddharth Rao and Dr. Erik Jan Marinissen from imec, Belgium. Special thanks to Dr. Gouri Sankar Kar for continuously supporting this collaboration project. Sid, thank you for being my daily supervisor at imec. The internship at imec opens a new world for me. I can clearly remember how you trained me to use the RRAM characterization tool to characterize MTJ devices. A lot of manual setups before the start of an auto. measurement. I messed up a couple of times. But you never got upset and were always patient to me. Thank you. Later on, we luckily moved to the Hprobe tool for our measurements, which was so much easier to use. I have also learned a lot from you in MTJ physics, device characterization and modeling, data analysis etc. You are dubbed as a magneticist in our team. By the way, you are also the guy who led my way to Python. Before going to imec, I was a MATLAB guy. Because of your persuasion, I changed to Python, which I found so much better and powerful that I had been using it until now. Putting aside work, you are also a very good friend of mine. Without you, I would not have adapted to the working environment at imec very quickly. Angelo is a nice, smart Italian guy. We had a lot of fun together including lunch breaks and several times of BBQ with his Italian friends. Giuseppe cooked tasty pasta with all ingredients shipped from Italy by his lovely Mom. I would also like to thank everyone in the MRAM device team: Kevin, Woojin, Jackson, and Simon, for their help and forming a friendly and relaxing atmosphere. I cherish the memory of beer gatherings at Café Belge. Belgium beers are amazing, although I can only name a few brands. I would like to thank the other supervisor: Erik Jan. I feel very honored to work with you, frankly. The first time we met is still fresh and clear in my mind as if it happened yesterday. On June 23, 2017, I delivered a presentation to you about STT-MRAM technology, design, and test. I was a bit nervous despite the fact that I had prepared this presentation for a week (Said told me there was a big guy visiting us from imec). In the end, this meeting went well and we had some Q&As during the presentation in a relaxing vibe. Since then, you became an indispensable member in our STT-MRAM testing team. There are countless moments of you in my mind that I would never forget. For example, When I moved to Leuven, you invited me along with some other students to your home for dinner. That was so sweet and unforgettable. When I gave my first ITC talk at ITC'18 in Phoenix, Prof. Mehdi asked me a tricky question, which I did not response to well. But luckily, you defended me in a very concise and elegant way. In the summer of 2019, when most people went for vacation, we had a lot of discussions on the magnetic coupling work via emails and confcalls. This work ended up winning the best paper award at DATE'20. I will also remember all the long emails we exchanged for discussing our work and papers. Writing these emails were never easy, neither reading them. Thanks for investing so much time on me. All in all, many thanks to both of you: Sid and Erik Jan. The winter in Leuven is as cold and windy as in Delft. But because of you two, I feel warm inside.

I would like to thank all my previous and current office mates: Daniël, Innocent, Peyman, Moritz, and Guilherme. Daniël, no matter how my office and colleagues change, you are always the one who sits beside me. When I need to read some Dutch documents or have troubles in my personal life, I always turn to you for help. Thanks for dealing with all this stuff for me over the past years. I will never forget the amazing conference trips we had in Phoenix and Baden-Baden. Innocent, thanks for nice conversations with you in the office. I also appreciate your invitations to join church prayers. Peyman, thanks for your lucky coin when I was in depression. Moritz, thanks a lot for translating both my thesis summary and propositions with many annoying updates. Don't forget to shout to the audience at least three times, device-aware test, when you give your conference presentations. Guilherme, thanks for running the simulations for our ETS paper. I am impressed by your enthusiasm in our office discussions, which are always very fruitful obviously. BTW, guys, our FP notation and naming scheme are the best innovation in the world. Sharing the same office with you gives me a lot of good memories: complaining about work and life, survival run crossing TU campus, chatting in a bar, etc. I wish all of you a bright future.

I would like to extend my thanks to all colleagues at the QCE department. Thanks to Prof. Koen Bertels for your efforts in creating a nice working environment and supporting all different kinds of social events such as football, Karting, bowling, barbecue, borrel, and Xmas party etc. Lei, Jintao, thank you for sharing your experience with me in living in the Netherlands and working with Said. Thanks to Anh and Guilherme for organizing QCE colloquia, which broaden my knowledge beyond my PhD topics. Many thanks to my Chinese fellow PhD friends: Shanshan, Jian, Xiang, Lingling, Yande, Wanghe, and **Baozhou**. Although we have different supervisors, we have a lot of things in common. With you guys, my four-year PhD life in Delft becomes colorful. Mahdi, Muath, Abdulqader, thank you for being my colleagues. I have learned many things from you especially about different cultures. We had an amazing week in Beijing during the 2019 Sino-Dutch Summer School, together with Abid. Thanks to Cezar, Abdullah, Haji, Troya, Mark, for having daily lunch and interesting conversations with jokes and laughs. These are the things that I miss so much in the days of working from home. I also want to acknowledge Lidwina, Joyce, Laura, Trisha, and Paul for taking care of management, paperwork, and other secretary-related tasks. Thanks to Erik for fixing computer problems and maintaining websites, servers, software etc.

I would like to mention our QCE indoor football game that takes place every week. I enjoyed it so much during my entire PhD. It not only serves as a social event for all colleagues in our department, but also provides a good chance to do some exercise to refresh myself. Thanks to all who have participated in this event. Special thanks to **Imran** for organizing it and sending us a reminder email every Wednesday. This role shifted to my dear colleague **Daniël** in the recent two years, thank you as well. I cannot stop laughing when recalling the moments of **Leon** shouting with a Megaphone "Guys, football, time for football" in the corridor. Said, Motta, Lei, Jintao, Daniël, Innocent, Luca, Peyman, Mohammod etc., it was so much fun playing football with you guys. I will keep my QCE football shirt as a memento forever.

I also want to express my gratitude to some of my Chinese PhD fellows at TU Delft,

friends, and professors. **Bowen**, it is my luck to be your friend. We shared some amazing moments living in DUWO studios at Roland Holstlaan in the first year. I have to say you are an excellent cook. **Shuaiqiang**, **Yande**, thanks for being my house mates at Arthur Schendelplein. **Xiaohui**, thank you for organizing some interesting activities. Special thanks to **Zhan**. We are both Erik Jan's students. This special network connects us and builds our friendship. I love talking to you about research and any other matters. Thanks to **Yachao** and **Luge**. We built our friendship many many years ago back in China. After moving to Europe to do our PhDs, we always keep in touch and share joys and sorrows in work and life. I enjoy all the trips with you in Europe. **Xindi**, thanks for handling all stuff for me in China. May our friendship last forever! Many thanks to Prof. **Liu Fang** and **Xiao Nong** for supporting me in doing a PhD overseas and many fruitful discussions related to my research.

Last but most importantly, I would like to express my deepest thanks to my family. My wife, **Zhang Yu**, is the most beautiful girl on earth (in my heart). Years ago in China, you did not even know how to cook. But you are apparently a Michelin 3-star chef now. The amazing food you cook gives me endless energy for work. Thank you for always staying with me no matter where I go, from China to Netherlands, then to Belgium, and back to Netherlands. The tulips at Keukenhof, the windmills at Kinderdijk, the world cup cheers at Leuven, and the church bells at Delft, all have witnessed our love. Thanks to my parents-in-law and brother-in-law for understanding and supporting me in the past few years. My parents, there are no words that I can express my gratitude to you. Your love and support give me courage to face any challenges in my life. I would also like to thank my sister, brother-in-law, and big uncle for contributing to a lovely and warm big family. Once in a while, we have a family video call on weekends and share interesting daily stories to each other. This really helps to get my mind off work and cheer me up sometimes. Many thanks to all of you!

Lizhou Wu Delft, October, 2020

# **CONTENTS**

| Su | mma  | ary     |                                        | vii |

|----|------|---------|----------------------------------------|-----|

| Sa | men  | vatting | ž                                      | ix  |

| Ac | knov | vledge  | ments                                  | xi  |

| 1  |      | oducti  |                                        | 1   |

|    | 1.1  | VLSI 7  | Test Philosophy                        |     |

|    |      | 1.1.1   | Position and Role of VLSI Tests        | 2   |

|    |      | 1.1.2   | Classification of VLSI Tests           | 4   |

|    |      | 1.1.3   | Test Escapes And Yield Loss            |     |

|    | 1.2  | Emerg   | ging Non-Volatile Memory Technologies  |     |

|    |      | 1.2.1   | Present Memory Hierarchy.              |     |

|    |      | 1.2.2   | Types of Semiconductor Memories        |     |

|    |      | 1.2.3   | Comparison of Semiconductor Memories   | 13  |

|    | 1.3  |         | of the Art in Memory Testing           | 15  |

|    |      |         | Traditional Memory Testing             |     |

|    |      |         | STT-MRAM Testing                       |     |

|    | 1.4  |         | rch Topics                             |     |

|    |      |         | Defect Modeling                        |     |

|    |      |         | Fault Modeling.                        |     |

|    |      |         | Test Development                       | 19  |

|    |      |         | ibutions of the Thesis                 |     |

|    | 1.6  | Thesis  | s Organization.                        | 22  |

| 2  | STT  | -MRAN   | A Behavior and Architecture            | 23  |

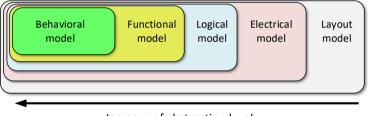

|    | 2.1  |         | IRAM Modeling Hierarchy                |     |

|    | 2.2  | Behav   | rioral STT-MRAM Model                  | 25  |

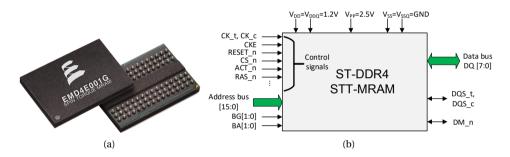

|    |      | 2.2.1   | STT-MRAM Package and Block Diagram     | 25  |

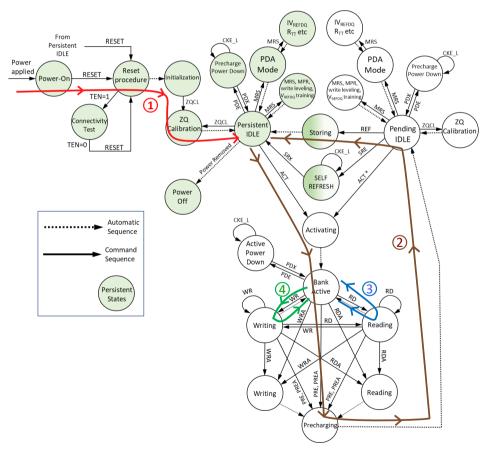

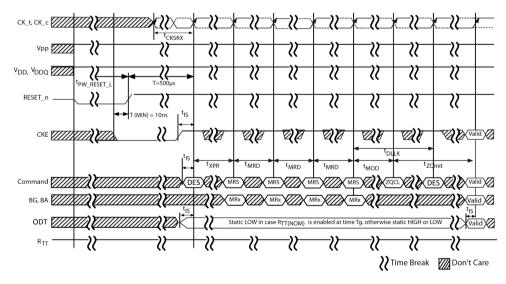

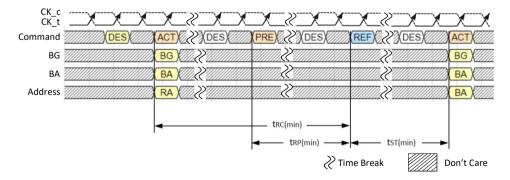

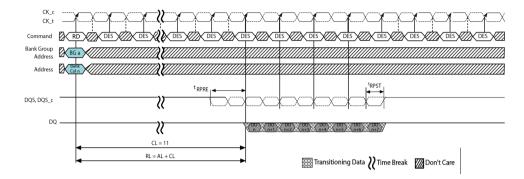

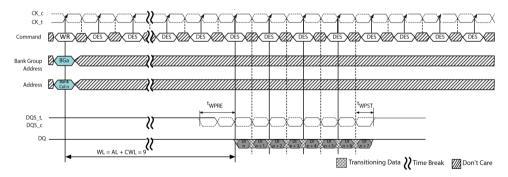

|    |      | 2.2.2   | ST-DDR4 Operations and Timing Diagrams |     |

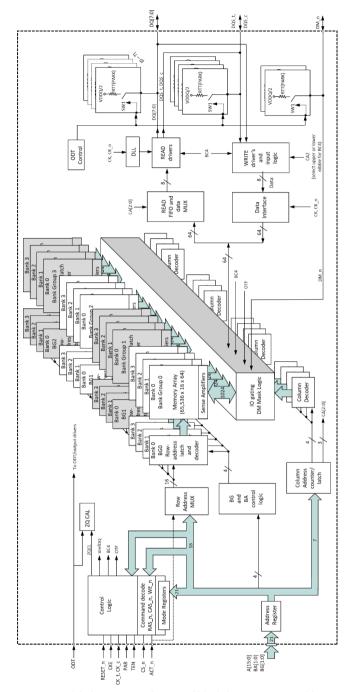

|    | 2.3  | Funct   | ional STT-MRAM Model                   | 34  |

|    |      | 2.3.1   | Functional Block Diagram               | 34  |

|    |      | 2.3.2   | Organization of Memory Arrays          |     |

|    |      | 2.3.3   | Internal Behavior                      | 38  |

| 3  | STT  | -MRAN   | A Technology and Implementation        | 43  |

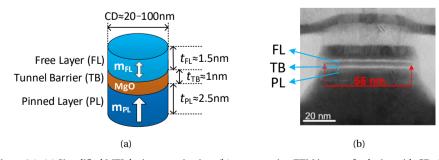

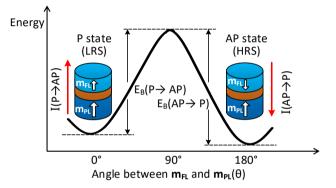

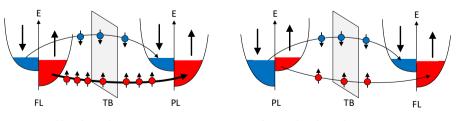

|    | 3.1  | MTJ T   | echnologies                            | 44  |

|    |      | 3.1.1   | MTJ Organization                       | 44  |

|    |      | 3.1.2   | Working Principles.                    | 45  |

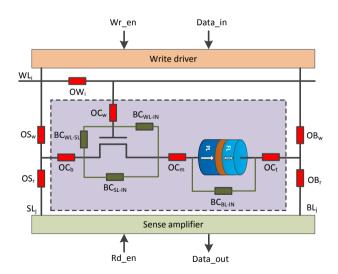

|   | 3.2                                           | Electrical STT-MRAM Model    50                                                                                 |  |  |  |  |  |

|---|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|   |                                               | 3.2.1 STT-MRAM Bit Cell                                                                                         |  |  |  |  |  |

|   |                                               | 3.2.2 STT-MRAM Peripheral Circuits                                                                              |  |  |  |  |  |

|   | 3.3                                           | STT-MRAM Layout Model                                                                                           |  |  |  |  |  |

|   | 3.4                                           | STT-MRAM Manufacturing Defects and Classification                                                               |  |  |  |  |  |

|   |                                               | 3.4.1 Conventional Defects in FEOL                                                                              |  |  |  |  |  |

|   |                                               | 3.4.2 Conventional Defects in BEOL 58                                                                           |  |  |  |  |  |

|   |                                               | 3.4.3 MTJ-Related Defects in BEOL                                                                               |  |  |  |  |  |

|   | 3.5                                           | STT-MRAM Past, Present, and Future                                                                              |  |  |  |  |  |

|   |                                               | 3.5.1 MTJ Evolution Course                                                                                      |  |  |  |  |  |

|   |                                               | 3.5.2 MRAM Commercialization                                                                                    |  |  |  |  |  |

|   |                                               | 3.5.3 STT-MRAM Potential Applications                                                                           |  |  |  |  |  |

|   |                                               | 3.5.4 STT-MRAM Remaining Challenges                                                                             |  |  |  |  |  |

| 4 | Testing STT-MRAM with Conventional Approach 7 |                                                                                                                 |  |  |  |  |  |

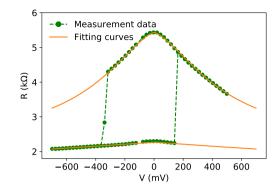

| т |                                               | Verilog-A Compact Model for Defect-Free MTJs                                                                    |  |  |  |  |  |

|   | 1,1                                           | 4.1.1 Bias Dependence of MTJ Resistance                                                                         |  |  |  |  |  |

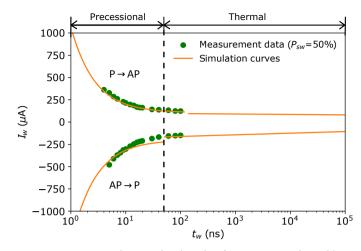

|   |                                               | 4.1.2 Switching Current at Various Pulse Widths                                                                 |  |  |  |  |  |

|   | 4.2                                           | Defect Modeling With Linear Resistors                                                                           |  |  |  |  |  |

|   | 4.3                                           | Fault Modeling   78                                                                                             |  |  |  |  |  |

|   | 4.4                                           | Test Development.   84                                                                                          |  |  |  |  |  |

|   |                                               |                                                                                                                 |  |  |  |  |  |

| 5 |                                               | metic-Field-Aware Compact Model of pMTJ 85                                                                      |  |  |  |  |  |

|   | 5.1                                           | Motivation and Prior Work                                                                                       |  |  |  |  |  |

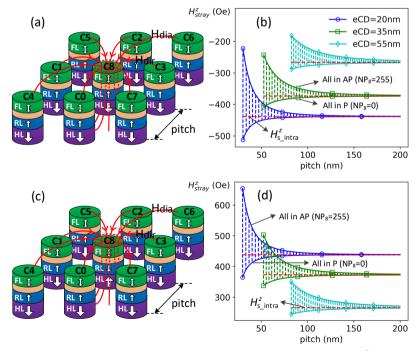

|   | 5.2                                           | Three Sources of Magnetic Field Disturbance   87                                                                |  |  |  |  |  |

|   | 5.3                                           | Characterization of Intra-Cell Stray Fields                                                                     |  |  |  |  |  |

|   | 5.4                                           | Modeling of Internal Stray Fields       90         5.4.1       Jata Call Stray Fields                           |  |  |  |  |  |

|   |                                               | 5.4.1 Intra-Cell Stray Field                                                                                    |  |  |  |  |  |

|   | 5.5                                           | 5.4.2       Inter-Cell Stray Field       92         Impact of Internal Stray Fields on MTI Performance       94 |  |  |  |  |  |

|   | 5.5                                           | There is a star for the star star star star star star star star                                                 |  |  |  |  |  |

|   |                                               | 5.5.1 Impact on the Critical Switching Current955.5.2 Impact on the Average Switching Time.96                   |  |  |  |  |  |

|   |                                               |                                                                                                                 |  |  |  |  |  |

|   | E C                                           | 5.5.3 Impact on the Thermal Stability Factor97Implementation of MTJ Model in Verilog-A98                        |  |  |  |  |  |

|   | 5.6                                           | 5.6.1 Overview of the Compact MTJ Model                                                                         |  |  |  |  |  |

|   |                                               | 5.6.2 Modeling of MTJ Resistance                                                                                |  |  |  |  |  |

|   |                                               | 5.6.3 Modeling of MTJ Switching Behavior                                                                        |  |  |  |  |  |

|   |                                               | 5.6.4 Modeling of Other Key Characteristics                                                                     |  |  |  |  |  |

|   | 5.7                                           | MTJ Electrical Characteristics Under Various                                                                    |  |  |  |  |  |

|   | 5.7                                           | Magnetic Configurations                                                                                         |  |  |  |  |  |

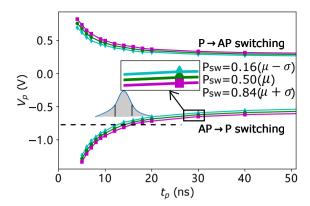

|   |                                               | 5.7.1 DC Simulations: R-V Loops                                                                                 |  |  |  |  |  |

|   |                                               | 5.7.2 Transient Simulations: WER Statistics                                                                     |  |  |  |  |  |

|   | 5.8                                           | Robustness Analysis of STT-MRAM Designs                                                                         |  |  |  |  |  |

|   | 5.0                                           | 5.8.1 Transient Simulations Under Different eCDs and Pitches 104                                                |  |  |  |  |  |

|   |                                               | 5.8.2 Design Space With Various Variation Sources                                                               |  |  |  |  |  |

|   |                                               | 5.5.2 Design opace with various variation obtrices                                                              |  |  |  |  |  |

| 6 |     |               |                                                           | 109 |

|---|-----|---------------|-----------------------------------------------------------|-----|

|   | 6.1 | Motiv         | ation and Prior Work                                      | 110 |

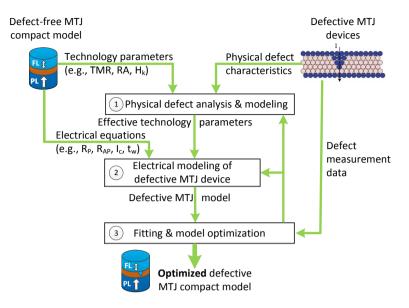

|   | 6.2 | Devic         | e-Aware Test Flow                                         | 111 |

|   | 6.3 | Devic         | e-Aware Defect Modeling                                   | 112 |

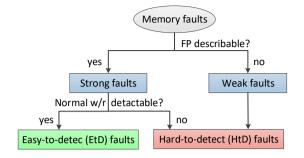

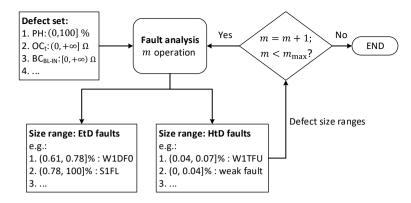

|   | 6.4 | Devic         | e-Aware Fault Modeling                                    | 113 |

|   |     |               | Fault Space and Classification                            |     |

|   |     |               | Fault Analysis Methodology                                |     |

|   | 6.5 |               | e-Aware Test Development                                  |     |

|   | 6.6 | DAT A         | dvantages and Challenges                                  | 120 |

| 7 | DAT | <b>for Pi</b> | nhole Defects                                             | 123 |

|   | 7.1 | Pinho         | le Defect Mechanism                                       | 124 |

|   | 7.2 | Pinho         | le Defect Characterization                                | 124 |

|   |     | 7.2.1         | Characterization at <i>t</i> =0                           | 125 |

|   |     | 7.2.2         | Characterization at $t>0$                                 | 126 |

|   | 7.3 | Limita        | ations of the Conventional Test Approach                  | 127 |

|   | 7.4 | Devic         | e-Aware Defect Modeling for Pinholes                      | 128 |

|   | 7.5 | Devic         | e-Aware Fault Modeling for Pinholes                       | 132 |

|   | 7.6 | Devic         | e-Aware Test Development for Pinholes                     | 134 |

| 8 | DAT | for Sv        | nthetic Anti-Ferromagnet Flip (SAFF) Defects              | 137 |

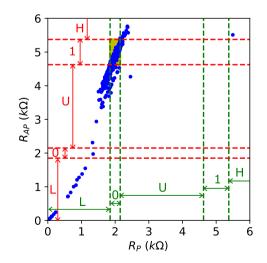

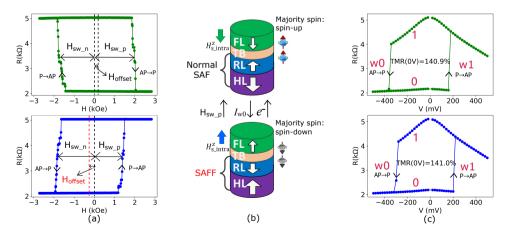

| Ū |     |               | Defect Characterization                                   |     |

|   |     |               | Magnetic Characterization.                                |     |

|   |     |               | Electrical Characterization.                              |     |

|   |     |               | SAFF Defect Mechanism and Potential Causes                |     |

|   | 8.2 |               | ations of the Conventional Test Approach                  |     |

|   | 8.3 | Devic         | e-Aware Defect Modeling for SAFF                          | 141 |

|   |     | 8.3.1         | Physical Defect Analysis and Modeling.                    | 141 |

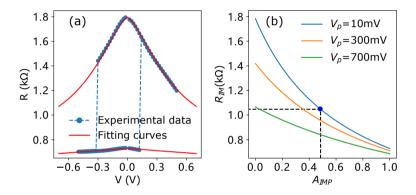

|   |     | 8.3.2         | Electrical Modeling of SAFF-Defective MTJ Devices         | 143 |

|   |     | 8.3.3         | Fitting and Model Optimization                            | 144 |

|   | 8.4 | Devic         | e-Aware Fault Modeling for SAFF                           | 146 |

|   | 8.5 | Devic         | e-Aware Test Development for SAFF                         | 147 |

| 9 | DAT | for In        | termediate (IM) State Defects                             | 149 |

|   |     |               | ate Defect Mechanism.                                     | 150 |

|   | 9.2 | IM Sta        | ate Defect Characterization                               | 151 |

|   |     | 9.2.1         | Measurement Set-up.                                       | 151 |

|   |     | 9.2.2         | Identification of IM State Defects                        |     |

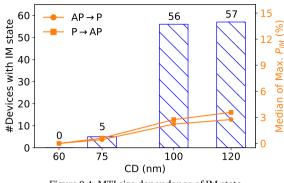

|   |     | 9.2.3         | Dependence of IM State Defects                            | 152 |

|   | 9.3 | Limita        | ations of the Conventional Test Approach                  |     |

|   | 9.4 | Devic         | e-Aware Defect Modeling for IM State.                     | 155 |

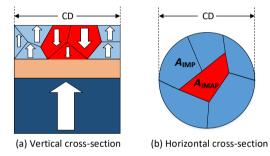

|   |     | 9.4.1         | Physical Defect Analysis and Modeling.                    | 155 |

|   |     | 9.4.2         | Electrical Modeling of MTJ Devices with a Single IM State |     |

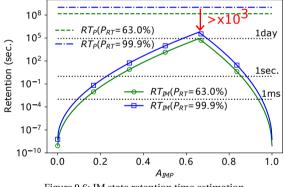

|   |     | 9.4.3         | Fitting and Model Optimization                            | 160 |

| 9.5     | Device-Aware Fault Modeling for IM State       | 162         |

|---------|------------------------------------------------|-------------|

| 9.6     | Device-Aware Test Development for IM State     | 165         |

|         | 9.6.1 Test Philosophy                          | 165         |

|         | 9.6.2 Test Solution With Weak Write Operations | 167         |

| 10 Con  | Iclusion                                       | l <b>69</b> |

| 10.1    | Summary                                        | 170         |

| 10.2    | Proture Research Directions                    | 173         |

| Referen | nces                                           | 177         |

| Nomen   | nclature J                                     | 95          |

| Currice | ulum Vitæ 2                                    | 201         |

| List of | Publications 2                                 | 203         |

# 1

# **INTRODUCTION**

# 1.1 VLSI Test Philosophy 1.2 Emerging Non-Volatile Memory Technologies 1.3 State of the Art in Memory Testing 1.4 Research Topics 1.5 Contributions of the Thesis 1.6 Thesis Organization

Spin-transfer torque magnetic random access memory (STT-MRAM) is considered as one of the most promising non-volatile memory technologies. After more than 40 years' research and development, its mass production is around the corner as numerous foundries and start-ups worldwide swarm into its commercialization. Like any semiconductor product, effective yet cost-efficient test solutions are of great importance to ensure high-quality STT-MRAM products being shipped to end customers. The main subject of this dissertation is to investigate STT-MRAM-specific manufacturing defects, accurately model them to derive realistic fault models, and eventually develop high-quality test solutions for STT-MRAMs. This chapter serves as a brief introduction to this dissertation. We start with highlighting the role of VLSI test, its importance, and basic concepts. Second, we introduce emerging non-volatile memory technologies covering three main classes: PCM, RRAM, and MRAM. Their working principles are briefly reviewed and their performance is compared to each other as well as to existing charge-based memories: SRAM, DRAM, and flash. Their development status, potential applications, and positioning in the present memory hierarchy is also discussed, with an emphasis on STT-MRAM. Third, we present the state of the art in both conventional memory testing and STT-MRAM testing. Fourth, we explain the research topics explored over the course of this PhD project. Fifth, we present the main contributions of this dissertation advancing the state-of-the-art in STT-MRAM testing. Finally, we detail the thesis organization.

## **1.1.** VLSI TEST PHILOSOPHY

This section introduces the VLSI test philosophy as well as some basic concepts and terminologies in this field. It first identifies the position and role of VLSI tests within the broad scope of electronic testing. Thereafter, a classification of VLSI tests is discussed. Finally, the concepts of test escape and yield loss in production tests are elaborated.

## 1.1.1. POSITION AND ROLE OF VLSI TESTS

With the successful advancement in *very large scale integration* (VLSI) technology for nearly half a century, semiconductor chips have become indispensable components in any modern electronic system. For example, smartphones are probably the most commonly known and used electronic system in our daily lives nowadays. Typically, a smartphones contains a large number of semiconductor chips, of which the system-on-chip (SoC) is undoubtedly the most important one. A SoC is a monolithic VLSI circuit including a variety of modules; an example is the Kirin 990 5G processor which integrates a central processing unit (CPU), neural processing unit (NPU), graphics processing unit (GPU), 5G modem, on-chip memories etc., which together are built with 10.3 billion transistors in a single chip of 113.31 mm<sup>2</sup> using TSMC's 7 nm process[1]. It is obvious that fabricating such a sophisticated VLSI chip is a complicated and time-consuming process which is prone to manufacturing defects. Therefore, to guarantee the quality and reliability of semiconductor chips, it is crucial to rigorously test them in different manners at different phases of lifetime.

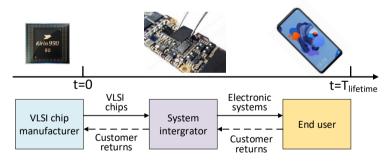

Typically, the lifetime of a VLSI chip can be divided into three phases involving three key parties, as illustrated in Figure 1.1. The first phase is the gestation period, where the

Figure 1.1: Three key phases and involved parties in the lifetime of a VLSI chip.

involved party is the VLSI chip manufacturer which defines the specifications of semiconductor chip products and subsequently designs and mass produce them. Note that the design company of a semiconductor chip may also be different from the one which eventually manufactures it. In the semiconductor industry, this is also a typical business model where a fabless company designs a product and get it fabricated in a foundry company which is dedicated to manufacture instead of designs. In the second phase, the fabricated chips are delivered to the system integrator which mounts them into electronic systems such as smartphones, laptops, and servers; these electronic systems are intended to be sold to the electronic market. The third phase mainly involves the end

1

user which buys these electronic devices and use them to accomplish a specific task. From a semiconductor chip's perspective, its life starts (typically referred to as t=0) when being shipped out from the manufacturer. Obviously, most of its lifetime is with the end user where it performs its designed functions in a system in the field of operation until wear-out.

In the above-mentioned three phases, VLSI chips are subjected to different tests. The VLSI chip manufacturer needs to conduct various manufacturing tests to weed out defective parts and guarantee that the outgoing parts to customers perform good functions as designed at t=0. Typically, the quality of VLSI chips is evaluated using a metric called *defective part per million* (DPPM). For instance, ten-DPPM means statistically ten parts out of one million parts shipped to the system integrator are defective. The test efforts that the manufacturer would make vary significantly depending on the chip quality requirements that are demanded by the system integrator. The chip quality requirements are in turn determined by the specific application that the system integrator expects its electronic system products to be used for. For example, a VLSI chip product targeting healthcare or aerospace applications requires much higher quality and therefore more stringent tests than that for kids' toys or consumer electronics.

In phase II, the second party, system integrator, may perform some basic tests (known as *incoming inspection*) with much less efforts and time than the previous manufacturing tests on certain number of selected samples of purchased VLSI chips, depending on the chip quality and system requirement. The purpose of incoming inspection is to avoid assembling defective chips into systems. But this practice is gradually disappearing, as companies nowadays expect the received chips to be high-quality and are often pressured by the time to market. Nevertheless, the system integrator focuses on a different type of test called *system test*. In other words, once a system composed of a large number of VLSI chips and other electronic components such as resistors, capacitors, batteries, and screens is manufactured, it also necessitates extensive tests before delivering to a customer. During this stage of testing, VLSI chips which are identified to be defective or cause system failures will be sent back to the manufacturer in the form of customer returns. The manufacturer is then expected to investigate these returned chips for failure analysis and diagnosis, which will be useful for improvements in either the test program or manufacturing process.

In phase III, the end user as the third party is not expected to conduct any testing work on the received product other than setting it up for regular usage. Similar to the customer returns from the system integrator to the chip manufacturer, the end user sends back defective products to the system integrator for reparation or replacement. However, as modern electronic systems are becoming increasingly complex and CMOS technology has entered into sub-10 ns era raising more reliability concerns, *on-line test* have become an important field for testing especially for some mission-critical industrial sectors such as satellites, automotive, and medical electronics [2]. On-line test is the test procedures running without the engagement of the end user in the field of operation, to monitor the hardware status so as to detect defective parts and enhance reliability or robustness. It can take place either concurrently during the normal operation mode or periodically during the idle mode.

Despite the fact that defective chips can be detected in all three phases of their life-

1

time, the first phase and the chip manufacturer should be primarily relied on to ensure the chip quality. This is because of the exponential increase in the cost of detecting a defective chip after being integrated into increasingly more complicated systems. A widely accepted rule of thumb in test economics in the electronics industry is the *rule of ten* [3]. It suggests that if a defective chip is not caught by chip-level testing, then finding it at printed circuit board level costs ten times as much as at the chip level. This cost factor continues to apply when the defective chip is incorporated into higher-level systems. Apart from the economic reason, selling defective chips to customers and receiving them back also have a negative impact on the manufacturer's reputation. In the worst case, a system failure due to a defective chip in the field may lead to a catastrophic accident or even the loss of human lives in some mission-critical applications such as automotive and healthcare.

All of the above aspects emphasize the importance of VLSI tests in phase I before t=0, which are mainly performed by the chip manufacturer. Since this test stage plays the most critical role in determining the chip quality, it incurs the biggest investment in testing, thus having the highest possibility of payback on research. Due to this reason, this thesis will be focused on this domain.

### 1.1.2. CLASSIFICATION OF VLSI TESTS

If a VLSI chip product is designed, fabricated, and tested, and it fails the test, then there must be a cause for the failure [3]. The cause can be the following: 1) the test is wrong, 2) the manufacturing process is faulty, 3) the design is incorrect, and 4) the specifications have a problem. Anything can go wrong. The responsibility of VLSI tests is to detect whether there is something wrong. If all chips fail, probably the first cause applies, i.e., the test is wrong. If the test is good and only a very small fraction of fabricated chips are tested negative, then we suspect 2), 3) and 4) might be the potential cause. To determine which type of cause leading to a chip failure, typically a variety of tests will be performed over the entire course of developing a VLSI chip product. Next, the classification of VLSI tests will be discussed.

VLSI tests taken by the chip manufacturer in phase I can be classified into three types as follows, depending on the test objectives and the development stage of a VLSI chip product [3].

1) Characterization: also known as design debug or verification test. This test form is performed on a new design before being sent to mass production. The first objective of characterization test is to verify that the design is correct and meets all specifications. Functional tests along with comprehensive AC and DC parametric measurements are run at this stage, to determine the limits of chip operation conditions such as supply voltage, temperature, and speed. Typically, these conditions are swept in given ranges and functional tests are performed repetitively for each combination of the above parameters. The measured results are plotted as a Shmoo plot where both the pass (P) and fail (F) regions are marked [4]. Other objectives of characterization tests include measuring chip characteristics for setting final specifications and determining a final production test program.

2) *Production*: every fabricated chip has to go through production tests. The objective of production tests is to enforce the quality requirements by determining whether

the chip under test meets all specifications. Production tests are go/no-go decision making processes which are less comprehensive than the previous characterization tests. The tests at this stage may not cover all possible functions, but they must guarantee a high coverage of modeled faults such that defective chips can be weeded out with a high confidence. As every chip must be tested, production test time for each chip is typically very short and the cost needs to be minimized as much as possible but without sacrificing the effectiveness of test.

*3) Burn-in*: passing production tests means that the passed chips meet design specifications at t=0, but it does not guarantee that they perform their functions as long as expected when getting to actual usage. Burn-in tests ensure the reliability of those chips which have passed production tests by testing either continuously or periodically over a long period of time at elevated voltage and/or temperature to force weak chips to fail at an accelerated speed [3]. Two types of failures can be isolated by burn-in tests: infant mortality and freak failures. The former are typically caused by weak defects or process variations; they can be screened out by short-term burn-in (10–20 hours) in a normal or slightly accelerated conditions. The latter occur to those chips which are as reliable as designed, thus requiring long burn-in time (100–1000 hours) in accelerated conditions. Compared to production tests, burn-in tests are much more expensive and time-consuming. Therefore, in practice, a manufacturer must take economics into account and make a trade-off between test overheads and chip reliability depending on the target applications.

## **1.1.3.** TEST ESCAPES AND YIELD LOSS

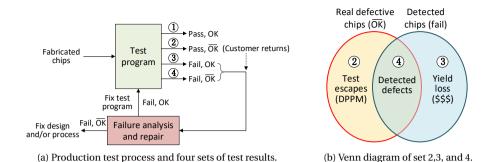

As introduced previously, a production test is a short and go/no-go decision making process for every single fabricated chip which is intended to going to costumers. Figure 1.2a depicts the production test process where all fabricated chips need to go through the test program and end up in four sets of test results as follow.

- (1) **Pass, OK**. Refer to chips which have passed the test and are real defect-free.

- (2) **Pass**, **OK**. Refer to chips which have passed the test but are defective actually.

- (3) Fail, OK. Refer to chips which have failed the test but are real defect-free.

- (4) Fail, OK. Refer to chips which have failed the test and are defective actually.

Ideally, we would like to have all defect-free chips pass the test and all defective chips fail the test. In other words, only set (1) and (4) are desired assuming that the test program is perfect. This maximize the interest of the manufacturer, as all chips being sold to customers would be as good as designed (i.e., 0 DPPM). However, this is almost impossible to achieve in practice, at least not achieved based on today's test technology at the point of writing this dissertation. A practical test program usually gives us a certain number of chips fallen into set (2) and (3), unfortunately. Both of these two sets of chips cost money to a manufacturer.

Set (2) contains defective chips that escape the test and therefore will be delivered to customers, along with other real defect-free chips in set (1). Test escapes can be caused by incomplete coverage of fault models due to high complexity or high cost. *Fault models*

1

Figure 1.2: Test escapes and yield loss in production tests.

typically are the target of production tests; they are the high-level abstraction of physical defects. Another cause could be that, in practice, not all physical defects are taken into account and are well modeled and represented by existing fault models. Some of these defective chips will be mounted onto PCBs and electronic systems, and subsequently leaked to the market. As a result, they may incur user complaints and even lead to accidents or loss of human lives in the worst case. Some will be sent back the their manufacturer in the form of customer returns if identified by higher-level tests such as system and on-line tests. costumer returns have a significant influence on the businessto-business relationship and may even damage the established reputation of the chip manufacturer.

Set (3) contains good chips which however fail the test. This can be caused by excessively stringent tests; an example is  $I_{\text{DDQ}}$  test [3] which may over kills some good chips by mistakenly identifying the increased leakage current due to process variations as defects. This set of chips directly lead to yield loss, thus increasing the cost of manufacturing a chip on average. In addition, rejecting good chips also indicates that the test itself needs to be improved so that this set would be minimized as much as possible in the future production.

Set (4) contains defective chips which are captured by the test. These chips do not meet design specifications and should go to the failure analysis and repair department along with the chips in set (3) and customer returns (belonging to set (2)). As illustrated in Figure 1.2a, investigating and understanding the failure mechanisms of chips in Set (4) are very important for yield learning process; the results can be used to fix design and/or manufacturing process.

Figure 1.2b shows a Venn diagram describing the relationship of set (2), (3), and (4). Set (2) and (3) are mainly caused by the incompetence of the test program. Thus, investigating the failure analysis of chips in these two sets are beneficial for an enhancement in the test program. From an economic point of view, the two circles in Figure 1.2b need to be as closely overlapped as possible for the purpose of reducing test escapes and yield loss. Since these two benefits literally mean higher quality and less cost in manufacturing for a VLSI chip product, identifying the real defective chips, i.e., making these two circles overlap, is the invariable goal of R&D investment in VLSI tests.

## **1.2.** Emerging Non-Volatile Memory Technologies

Memory is an indispensable component in any computer system, and it is also one of the biggest sectors in the semiconductor industry. As existing memories such as SRAM, DRAM, and flash gradually approach their down-scaling limits, they become increasingly power hungry, and less reliable while the fabrication is more expensive due to the increased manufacturing complexity. As alternative solutions, several promising nonvolatile memory (NVM) technologies have emerged and attracted extensive R&D attention for various levels in the memory hierarchy. This section starts with a brief overview of today's memory hierarchy. Then, a classification of mainstream existing and emerging memories is provided. Finally, a comparison of these memories is presented.

## **1.2.1.** PRESENT MEMORY HIERARCHY

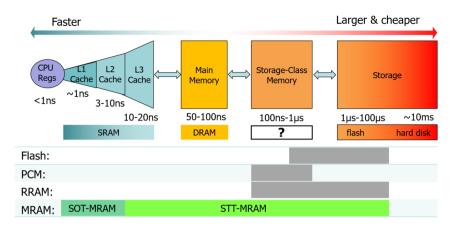

It is well recognized that the classical Von Neumann architecture comprises separate central processing unit (CPU) and memory unit. This means that data and instructions have to be frequently moved between these two units. Ideally, one would desire a system with its memory as fast as CPU, which maximizes the system performance. However, the reality is that the CPU speed is much higher than that of any type of existing memory nowadays. Starting from 1980 when their speeds are approximately the same, both CPU and memory have substantially evolved over the past four decades. The performance of CPU has improved tremendously by first boosting clock rate of single-core processor and subsequently incorporating multiple cores starting from around 2005. For instance, the Intel Core i7-960 processor contains 4 cores, each of which runs at 3.2 GHz (i.e., 0.3 ns per clock cycle). In contrast, the performance of main memory has not improved significantly in the past few decades, despite the fact that the density has increased considerably and the price per bit has become more and more affordable. Typically, the access latency of dynamic random access memory (DRAM) is 50-100 ns [5], which is more than three orders of magnitude slower than the speed of a high-end multi-core processor these days. This is well known as the "memory wall" [6], making memory the bottleneck of system performance. Compared to DRAM, static random access memory (SRAM) is much faster, up to  $\sim 1$  ns. However, the downsides of SRAM are its high cost per bit and large area of memory cell. Other memory technologies such as flash and magnetic disk are cheap and large in volume, but they are orders of magnitude slower than DRAM. Unfortunately, there is no such an ideal memory technology which is fast, cheap, and large in volume, combining the benefits of all aforementioned memories.

To build such a desirable memory system, an economical solution is a memory hierarchy, which takes advantage of locality and cost-performance trade-offs of memory technologies. The principle of locality means that programs tend to reuse data and instructions they have used recently [6]. Figure 1.3 shows a multi-layer memory hierarchy, including the typical access speed of each level and the position of each memory technology. Traditionally, the memory hierarchy consists of three major layers: cache, main memory, and mass storage, implemented by SRAM, DRAM, and hard drive disk, respectively. Cache is fast, small, and expensive; thus, it is located the closest to the CPU. Main memory provides medium performance and cost, thus following the cache as the next memory layer in the hierarchy. With the lowest speed and largest volume, mass storage layer is the farthest layer to the CPU. In most cases, the data contained in a farther layer

Figure 1.3: Present memory hierarchy in computer systems.

is a superset of data in the previous layer closer to the CPU. The goal of the memory hierarchy is to provide a memory system with cost per bit almost as low as the cheapest layer and speed almost as fast as the fastest layer.

With the CPU-memory performance gap becoming wider and the emergence of new memory technologies, the memory hierarchy has also been evolving over time. First, the cache layer has been split into several sub-layers to meet the ever-increasing memory access demand from the CPU. Figure 1.3 shows a three-level cache structure with the fastest L1 cache closest to the CPU and slower but larger L2 and L3 at lower levels. Second, flash memories are ubiquitous these days, serving as complementary storage media to the traditional hard disks. Thanks to their fast speed, non-volatility, and continuous bit cost reduction, they are widely used in solid-state drives (SSDs), smart phones, tablets, laptops, databases etc. Third, the gap in performance and price between the storage layer (including both flash and hard disk) and the main memory layer (DRAM) is still much wider than that between main memory and last-level cache. This has motivated the idea of adding a new memory layer which is commonly referred to as storage-class memory (SCM) [7] to fill in this gap in recent years. Flash memory, as a successful pioneer non-volatile memory technology, has the potential to adapt to the SCM layer. However, the main obstacles include its limited endurance and access speed in comparison to DRAM, making flash memory alone unable to serve as SCM. To address this issue, research attempts have been focused on hybridizing flash memory with other high-performance memory types such as DRAM [8].

Candidates for SCM also include emerging NVM technologies such as phase-change memory (PCM), resistive random access memory (RRAM), and magnetic random access memory (MRAM). These memory technologies offers storage-class retention, relatively higher endurance than flash memory, and attractive read/write performance as high as DRAM or even SRAM but with considerably less static power consumption [9]. Due to these advantageous features, they can not only adapt to the SCM layer, but also may even revolutionize the entire memory hierarchy once they are mass produced and their cost per bit drops. Figure 1.3 shows the potential application position of each of these NVM technologies in the memory hierarchy. Limited by endurance (primary) and speed

1

(secondary), PCM and RRAM are predicted to be suitable for the SCM layer and below [10]. In contrast, MRAM provides an excellent tailorability by making trade-offs between retention, endurance, and speed with different programming technologies. Therefore, many believe that MRAM including its sub-classes with different flavors can be a true universal memory technology in the future [11]. Next, we will introduce all these memory technologies in more detail.

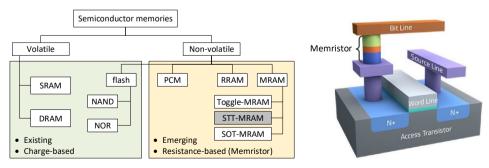

### **1.2.2.** Types of Semiconductor Memories

In general, semiconductor memories can be classified into two categories: volatile and non-volatile [10], as shown in Figure 1.4a. Volatile memories require continuous power supply to retain the stored data while non-volatile memories can retain the stored data even if the power is switched off. The mainstream volatile memories are SRAM and DRAM, which are ubiquitous in today's computer systems. Non-volatile memories include magnetic disk and flash memory conventionally. Note that magnetic disk is not considered as a type of semiconductor memory, as it is not based on transistors and involves slow mechanical movements in read and write operations. Thus, magnetic disk, through still the dominant storage medium at the moment, is not covered in our discussions in this thesis. Flash memory has two types: NAND and NOR. NAND flash features increasingly higher density and lower cost per bit, thanks multi-level cell and 3D stack technologies [8]. It is suitable for high-end storage applications in replacement of magnetic disk. In contrast, NOR flash memory is more expensive and faster in random access but lower in programming and erasing operations. These features make NOR flash more suitable for storage applications requiring fast read and occasional write (e.g., storing program code in mobile devices).

In addition, the majority of emerging memory technologies are non-volatile. For example, PCM, RRAM, and MRAM have attached large amounts of R&D attention over the past decades and have been prototyped and even commercialized in a small scale by worldwide semiconductor companies such as Intel, Samsung, Globalfoundries, and Everspin in recent years [12–15]. There are also several emerging memory technologies at early R&D stages, including ferroelectric random access memory (FeRAM), Carbonbased memory, Mott memory etc. [10]. These memories will not be discussed in this thesis.

(a) Classification of semiconductor memories.

(b) Basic 1T-1R memory cell sturcture.

Figure 1.4: Types of semiconductor memory technologies.

1

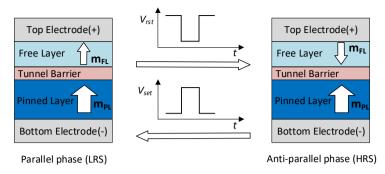

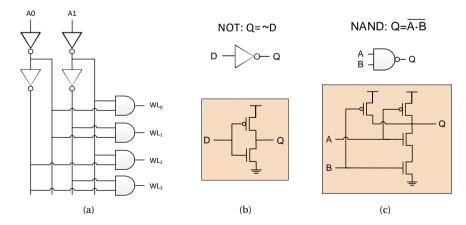

Based on the physical form in which the information is stored, the aforementioned semiconductor memories can also be categorized into charge-based and resistance-based memories. The former category include three existing mainstream semiconductor memories on the market: SRAM, DRAM, and flash memories, which utilize the quantity of electric charge to encode logic state '0' and '1'. The latter category comprises emerging memories: PCM, RRAM, and MRAM, which store data in the form of resistance; based on the write mechanism, MRAM can be further divided into first-generation Toggle-MRAM, second-generation STT-MRAMs, and SOT-MRAM as a representative of third-generation MRAM technologies. As the data-storing devices of these three types of NVM all encode logic states by exploiting the large resistance contrast in distinct physical states (e.g., amorphous and crystalline phases), they are all referred to as Memristors sometimes. These three types of Memristor are all compatible with the conventional CMOS process and are typically integrated between two adjacent metal lines in the back-end-of-line (BEOL) process. Figure 1.4b shows a schematic of the most commonly used 1T-1R memory cell structure. It consists of a transistor (access selector) at the bottom fabricated in the front-end-of-line (FEOL) process and a Memristor device (data-storing element) inserted in the subsequent BEOL process. Note that there exist several other selector candidates such as two-terminal diode or non-linear device in [10, 16], despite transistor is still the most popular one. Next, the working principle of each type of memristor will be elaborated.

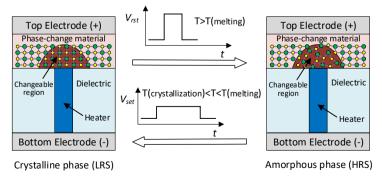

#### PHASE-CHANGE MEMORY (PCM)

Phase-change memory (PCM) stores data by exploiting the large resistance contrast between poly-crystalline and amorphous phases in phase-change materials such as chalcogenide [17, 18]. Figure 1.5 illustrates the basic structure of mushroom-shaped PCM device and the transformation principle between the two phases. To reset the PCM device into the amorphous phase, a positive pulse with large amplitude ( $V_{set}$ ) and short width ( $t_{set}\sim50$ ns) is applied across the device. As a result, a current flows through the heater (resistor) which contacts the above phase-change layer in the device, generating a large amount of Joule heating. The generated Joule heating raises the temperature above the melting point, thus transforming the phase-change material in the mushroom-cap area into the amorphous phase, corresponding to the high resistance state (HRS). To set the PCM device into the crystalline phase, a medium pulse ( $V_{rst}$ ) with the same polarity as

Figure 1.5: Basic mushroom-shaped structure of PCM device and its working principle.

the previous set pulse is applied for  $100 \text{ ns} - 10 \mu \text{s}$  ( $t_{rst}$ ), which anneals the changeable region at a temperature between the crystallization point and the melting point. The crystalline phase corresponds to the low resistance state (LRS), whose resistance can be three or four orders of magnitude lower than that of HRS. The large contrast in resistance is used to distinguish the two phases by applying a small bias to the device without disturbing its state.

PCM is among the most promising NVM technologies and has undergone significant academic and industrial research since the late 1960s. This has resulted numerous demonstration chips including a 1Gb chip by Micron in 2010 [19], a 8Gb chip by Samsung in 2012[12] and even a commercial product: 3D-Xpoint by Intel[20] in 2016. In the 2000s, PCM was considered to serve as a universal memory replacing both DRAM and NAND flash, as it exhibited high speed and scalability competitive to DRAM while being nonvolatile and owning higher endurance than NAND flash. However, this initial goal was not achieved due to the continuous improvement of DRAM and NAND flash as well as the limitations of PCM itself. Further innovations on PCM are needed to reduce power consumption, minimize resistance drift, improve endurance, and increase density [18]. Later on until now, the community has converged on the use of PCM as a SCM candidate complementing the traditional memory hierarchy shown in Figure 1.3.

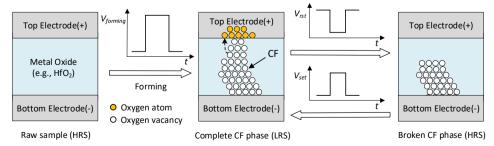

#### **RESISTIVE RANDOM ACCESS MEMORY(RRAM)**

Resistive Random Access Memory (RRAM) stores data by exploiting the large resistance contrast between the complete *conductive filament* (CF) phase and the incomplete CF phase in the metal-oxide materials such as  $HfO_x$  [21]. Figure 1.6 illustrates the basic structure of metal-oxide RRAM device and its working principle as a non-volatile memory. A RRAM device fundamentally consists of two electrodes sandwiching a metal-oxide layer. As pure metal oxides are intrinsically dielectric, a fresh RRAM device (left one in the figure) exhibits a extremely high resistance. To make the RRAM device ready for transitions between the aforementioned binary states, a key manufacturing step known as the forming process is required. It refers to the process of creating a conductive filament, akin to a tunnel for electrons to freely move through, in the metal oxide by applying a high voltage ( $V_{\text{forming}}$ ) across the raw RRAM device. Under the applied high electric field (>10MV/cm), oxygen atoms are knocked out of the lattice and drift in the form of negative ions towards the top electrode (anode). This process leaves oxygen vacancies behind in the oxide layer. When enough oxygen vacancies are localized and form a conductive

Figure 1.6: Basic structure of metal-oxide RRAM device and its working principle.

filament connecting the top and bottom electrodes, the device exhibits high conductance (i.e., LRS) as illustrated with the device schematic in the middle of the figure.

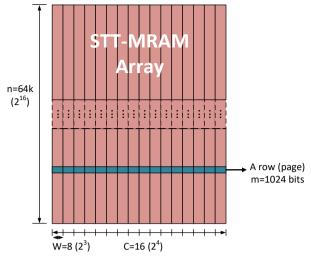

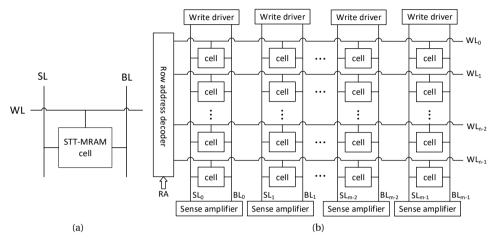

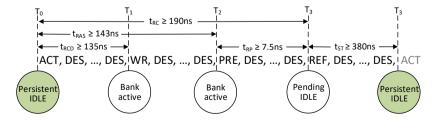

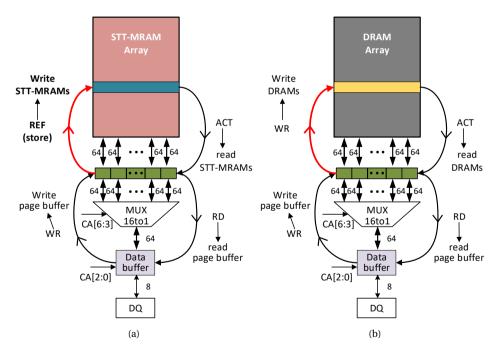

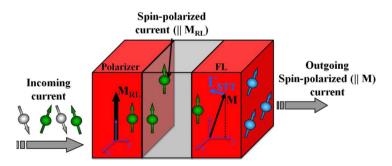

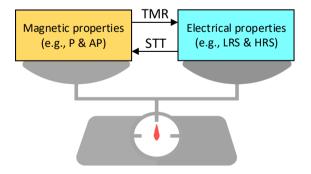

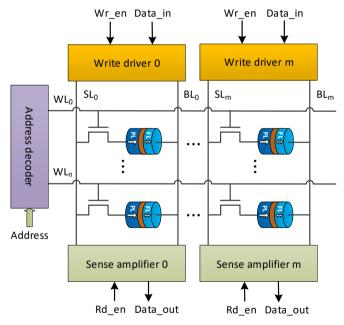

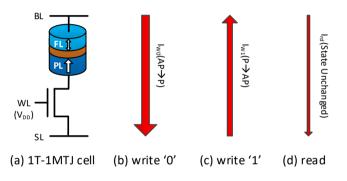

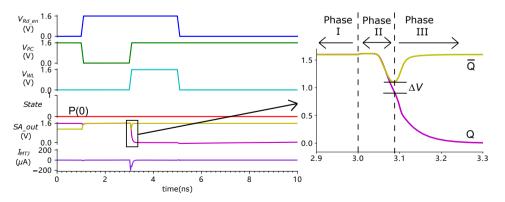

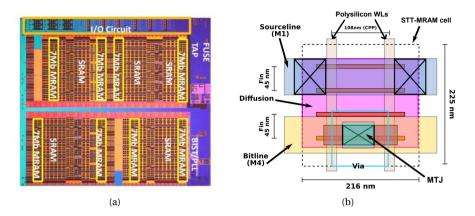

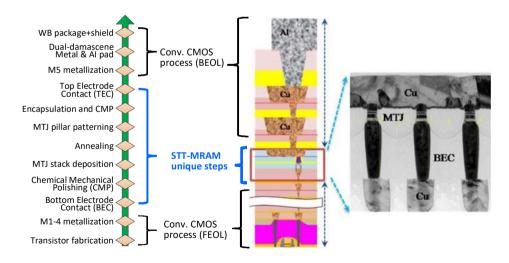

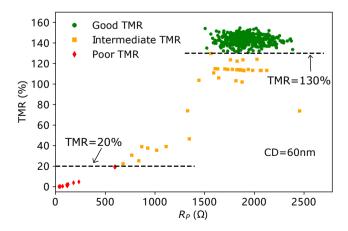

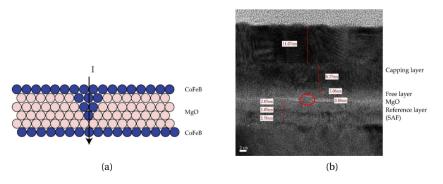

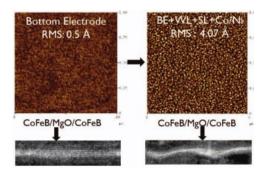

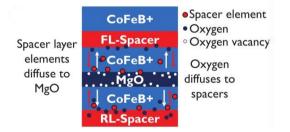

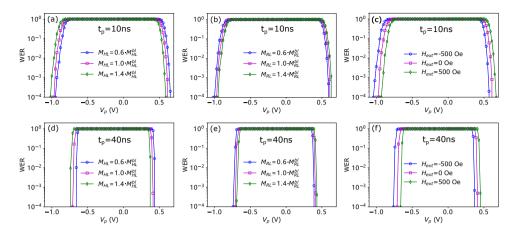

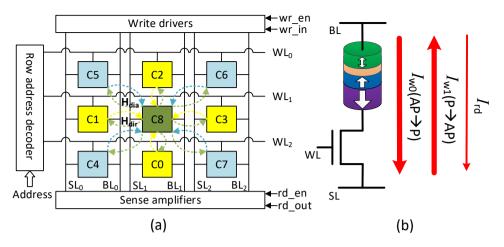

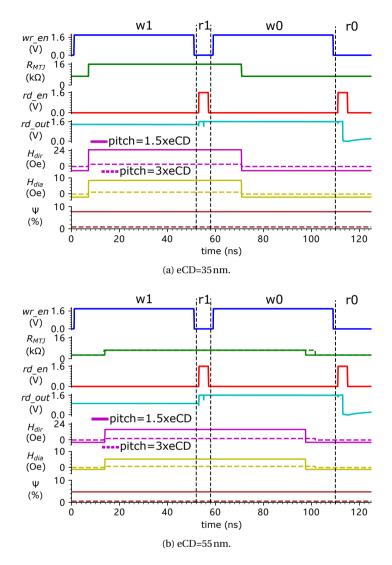

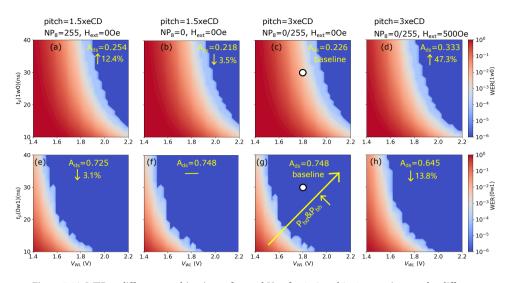

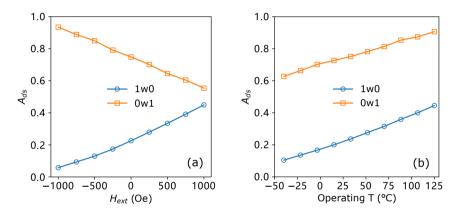

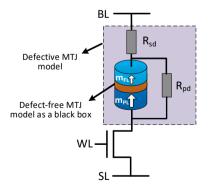

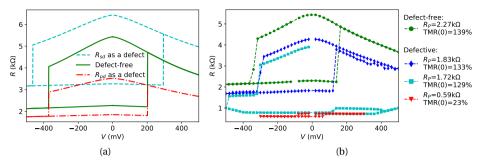

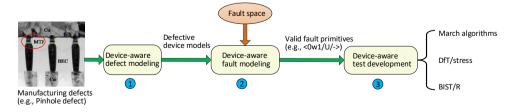

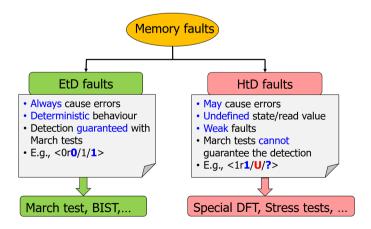

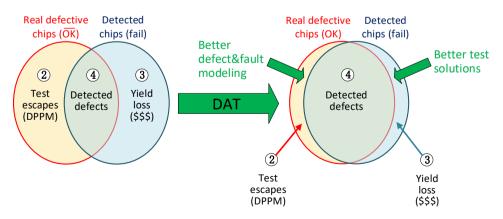

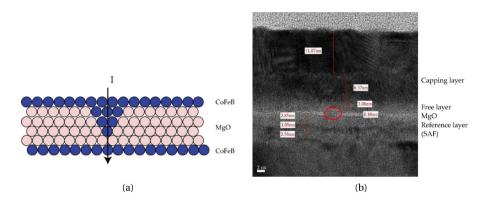

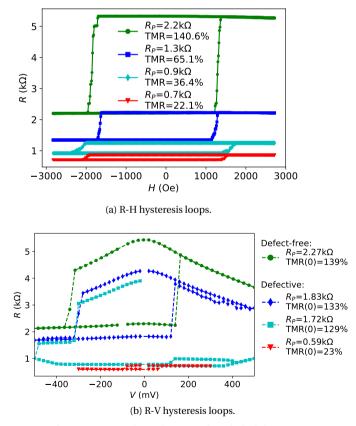

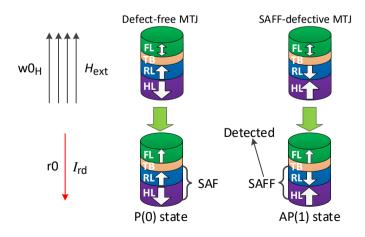

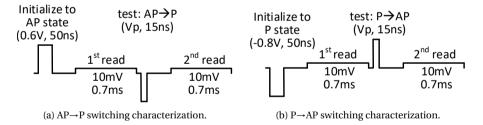

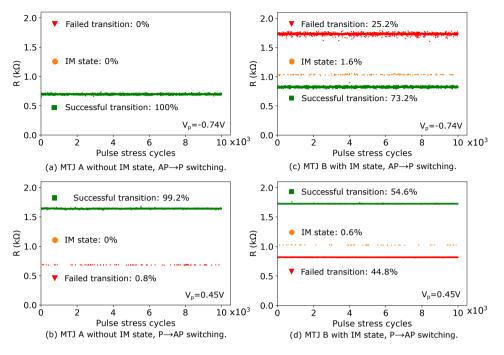

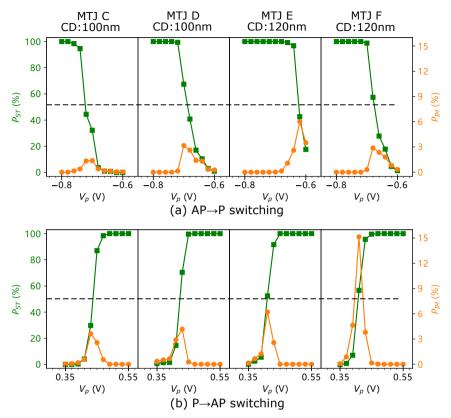

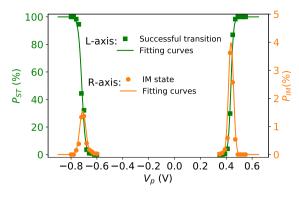

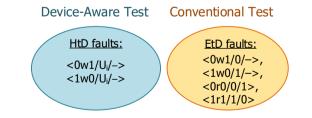

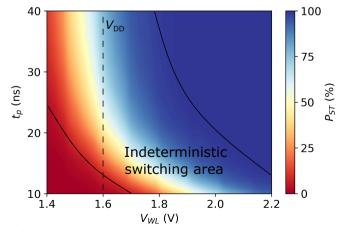

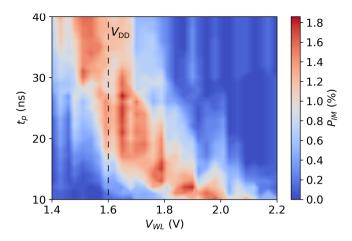

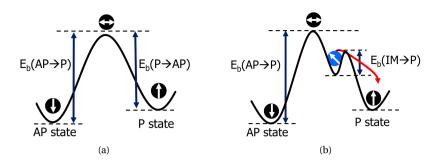

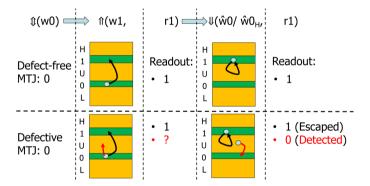

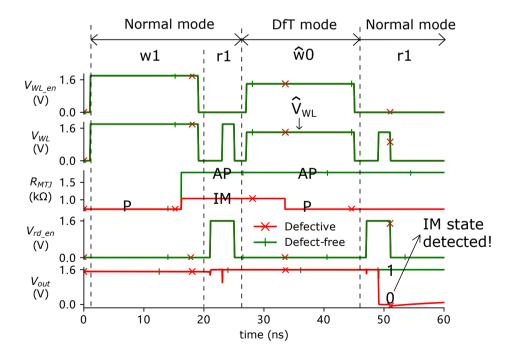

After the forming process, the RRAM device can be transformed from LRS to HRS (reset process) and from HRS to LRS (set process) by applying appropriate pulses. To reset the device, a negative pulse ( $V_{rst}$ ) has to be applied. Under the induced electric field, oxygen ions migrate back to the oxide layer and recombine with a portion of oxygen vacancies near the top electrode. As the device contains an incomplete CF in its oxide layer, it transforms to the HRS (the right device schematic in Figure 1.6). Note that the resistance with an incomplete CF is much smaller than that of raw samples before the forming process, since the incomplete CF acts as a virtual bottom electrode. To set the device, a positive pulse ( $V_{set}$ ) is applied to regenerate the complete CF. Due to the existence of the incomplete CF during normal switching cycles, both  $V_{rst}$  and  $V_{set}$  are smaller than  $V_{forming}$ . To read the resistive state of the device, a small bias is applied, similar to the read operation for the PCM device previously. The read window (i.e., HRS/LRS ratio) for RRAM devices is very wide, typically in the range of  $10^1 - 10^4$  [21].